ESCUELA TÉCNICA SUPERIOR DE INGENIEROS

INDUSTRIALES Y DE TELECOMUNICACIÓN

UNIVERSIDAD DE CANTABRIA

*Trabajo Fin de Grado*

**Diseño de un amplificador de bajo ruido en

tecnología monolítica en la banda Q para

aplicaciones de Radiometría

(Q-Band MMIC Low-Noise Amplifier Design for

Radio-Astronomy Applications)**

Para acceder al Título de

*Graduado en

Ingeniería de Tecnologías de Telecomunicación*

Autor: Adrián Gómez Rumoroso

Octubre – 2015

# **GRADUADO EN INGENIERÍA DE TECNOLOGÍAS DE TELECOMUNICACIÓN**

CALIFICACIÓN DEL TRABAJO FIN DE GRADO

**Realizado por: Adrián Gómez Rumoroso**

**Director del TFG: Mº Luisa de la Fuente Rodríguez y Enrique Villa Benito**

**Título: “Diseño de un amplificador de bajo ruido en tecnología monolítica en la banda Q para aplicaciones de Radiometría”**

**Title: “Q-Band MMIC Low-Noise Amplifier Design for Radio-Astronomy Applications”**

**Presentado a examen el día:**

para acceder al Título de

# **GRADUADO EN INGENIERÍA DE TECNOLOGÍAS DE TELECOMUNICACIÓN**

**Composición del Tribunal:**

Presidente (Apellidos, Nombre):

Secretario (Apellidos, Nombre):

Vocal (Apellidos, Nombre):

Este Tribunal ha resuelto otorgar la calificación de: .....

Fdo.: El Presidente

Fdo.: El Secretario

Fdo.: El Vocal

Fdo.: El Director del TFG

(sólo si es distinto del Secretario)

Vº Bº del Subdirector

Trabajo Fin de Grado Nº

Secretaría)

(a asignar por

# Agradecimientos

En primer lugar me gustaría agradecer a mis directores del proyecto de fin de grado, Luisa de La Fuente y Enrique Villa por su disponibilidad a la hora de resolver cualquier duda, por su infinita paciencia en explicarme los conocimientos necesarios así como también por sus consejos y aportaciones recibidas a lo largo de la realización del proyecto.

En segundo lugar me gustaría agradecer a mi familia por su esfuerzo, la confianza y el inestimable apoyo que me han dado durante estos años.

No puedo olvidar de mis mejores amigos, con los cuales sigo pasando buenos ratos día tras día, con los que he disfrutado y estoy seguro que disfrutaré de grandes momentos en los tiempos libres, además de por su apoyo, ayuda y disponibilidad siempre que lo necesite.

También agradecer a todos mis compañeros de promoción, en especial para aquellos con los cuales he compartido clases, ratos de estudio y grandes momentos, que han hecho que estos años hayan sido mucho más llevaderos.

Tampoco me puedo olvidar de todos aquellos profesores con los cuales he compartidos muchas horas de clase, y que me han proporcionado los conocimientos necesarios para estar hoy donde estoy.

Y por último agradecer también a José Vicente Terán, miembro del departamento de DICOM, que con su experiencia en otros proyectos muy similares, me ha sacado de varios apuros en diferentes momentos.

# Índice

|                                                                  |    |

|------------------------------------------------------------------|----|

| <b>1. Introducción</b> .....                                     | 9  |

| <b>2. Objetivos y marco de trabajo</b> .....                     | 10 |

| <b>3. Tecnología utilizada</b> .....                             | 11 |

| 3.1 Proceso D007IH de OMMIC .....                                | 11 |

| 3.2 Definición del sustrato .....                                | 12 |

| 3.3 MMIC vs MIC .....                                            | 14 |

| <b>4. Diseño</b> .....                                           | 16 |

| 4.1 Especificaciones de diseño.....                              | 16 |

| 4.2 Configuración de las etapas amplificadoras.....              | 17 |

| 4.3 Caracterización del transistor .....                         | 18 |

| 4.3.1 Análisis DC .....                                          | 18 |

| 4.3.2 Realimentación fuente .....                                | 20 |

| 4.4 Diseño eléctrico: Esquemático.....                           | 23 |

| 4.4.1 Redes de polarización .....                                | 23 |

| 4.4.2 Primera etapa amplificadora: Red entrada .....             | 28 |

| 4.4.3 Segunda etapa amplificadora .....                          | 30 |

| 4.4.4 Tercera etapa amplificadora .....                          | 34 |

| 4.4.5 Cuarta etapa amplificadora.....                            | 36 |

| 4.4.6 Valoraciones del diseño .....                              | 39 |

| 4.5 Diseño electromagnético: Momentum .....                      | 40 |

| 4.5.1 Consideraciones previas.....                               | 40 |

| 4.5.2 Red entrada .....                                          | 42 |

| 4.5.3 Red entre el primer y segundo transistor .....             | 45 |

| 4.5.4 Red entre el segundo y tercer transistor .....             | 48 |

| 4.5.5 Red entre el tercer y cuarto transistor.....               | 51 |

| 4.5.6 Red de salida.....                                         | 54 |

| 4.5.7 Diseño del Layout .....                                    | 57 |

| 4.5.8 Valoraciones del diseño .....                              | 58 |

| <b>5. Conclusiones finales</b> .....                             | 60 |

| <b>6. Bibliografía</b> .....                                     | 63 |

| <b>Anexo1. Layout del amplificador de bajo ruido (LNA)</b> ..... | 64 |

# Índice de figuras

|                                                                                                                                                                                                                |    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| <b>Figura 1-</b> Perfil de las capas del proceso D007IH de OMMIC .....                                                                                                                                         | 11 |

| <b>Figura 2-</b> Distribución de capas del sustrato utilizado para simulaciones electromagnéticas para la tecnología D007IH de OMMIC.....                                                                      | 12 |

| <b>Figura 3-</b> Fotografías de diseños de un amplificador LNA. A la izquierda con tecnología MIC y a la derecha con tecnología MMIC.....                                                                      | 15 |

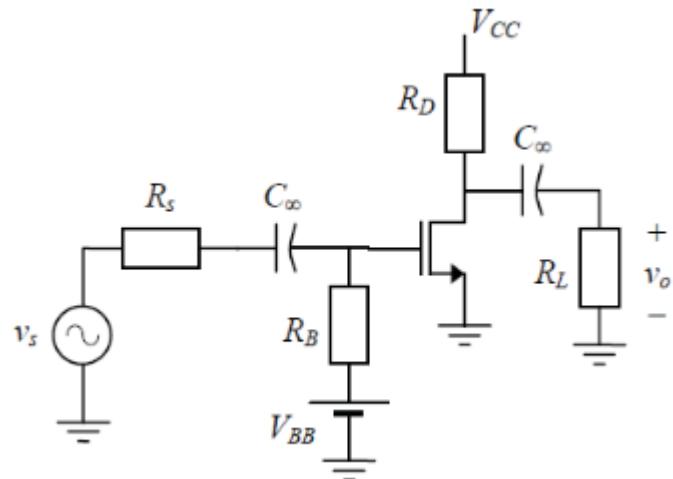

| <b>Figura 4-</b> Configuración en fuente común de un transistor.....                                                                                                                                           | 17 |

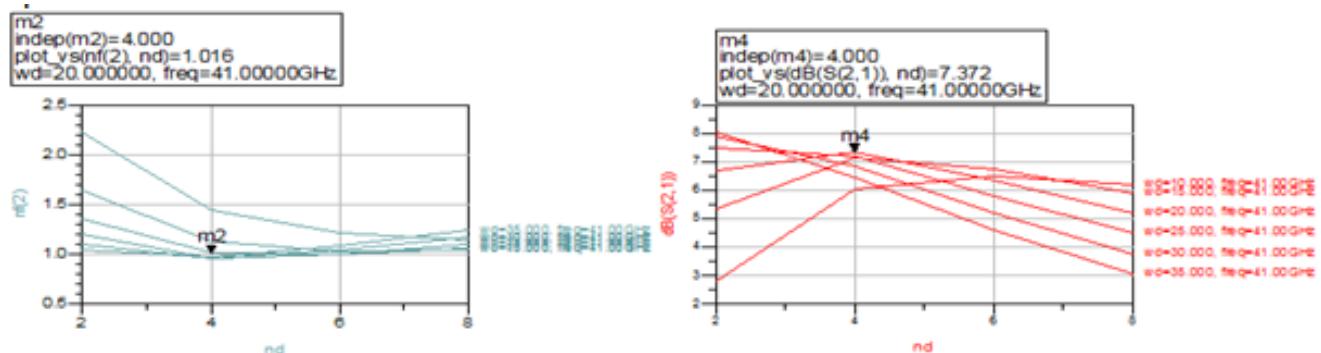

| <b>Figura 5-</b> Resultados de figura de ruido y ganancia del estudio del tamaño del transistor .....                                                                                                          | 18 |

| <b>Figura 6-</b> Resultados de ganancia y figura de ruido del estudio de la polarización del transistor.....                                                                                                   | 19 |

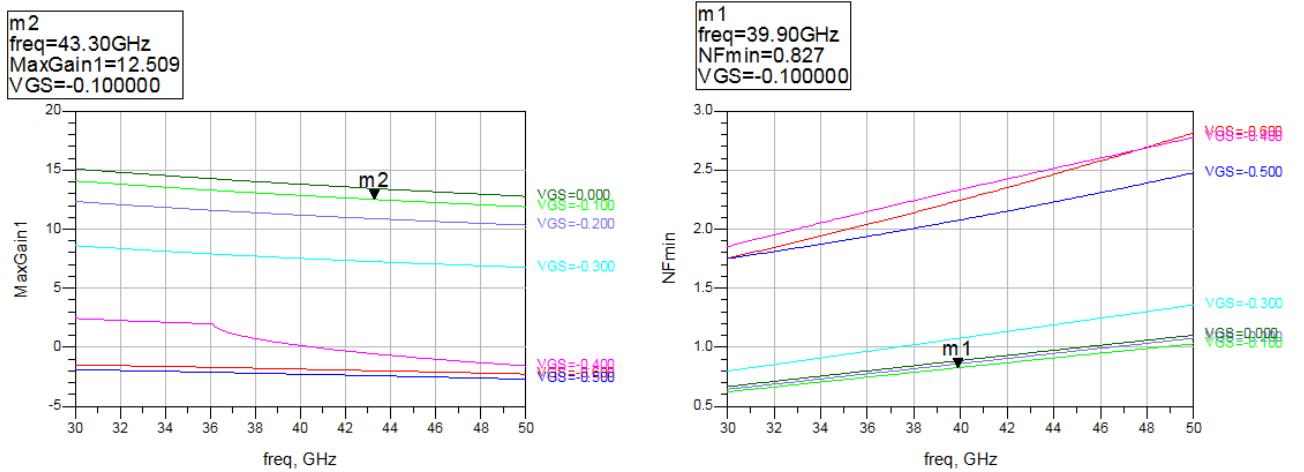

| <b>Figura 7-</b> $S_{opt}$ y $S_{11}^*$ del transistor en la carta de Smith, antes (parte izquierda) y después (parte derecha) de incluir la realimentación fuente .....                                       | 20 |

| <b>Figura 8-</b> Esquema de un transistor con realimentación serie .....                                                                                                                                       | 21 |

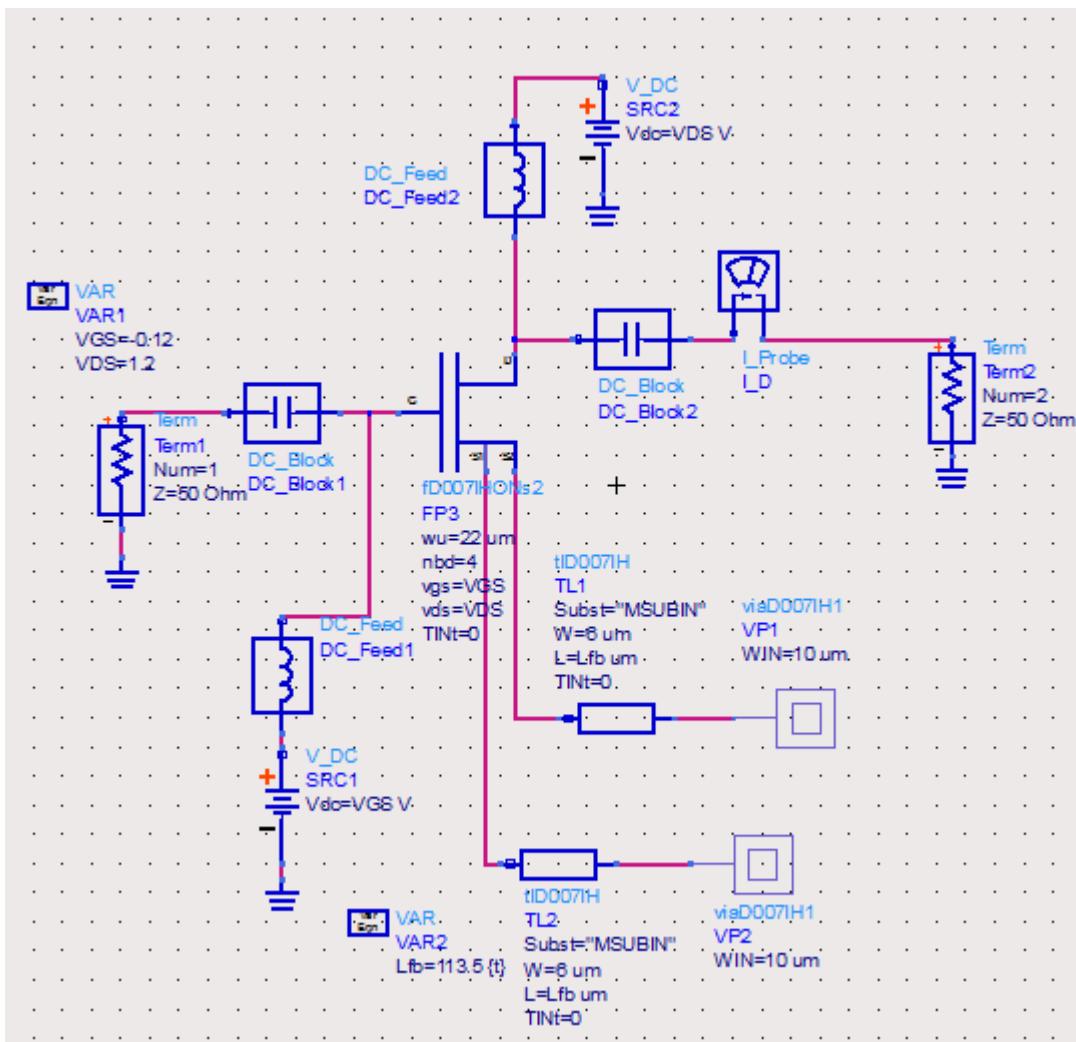

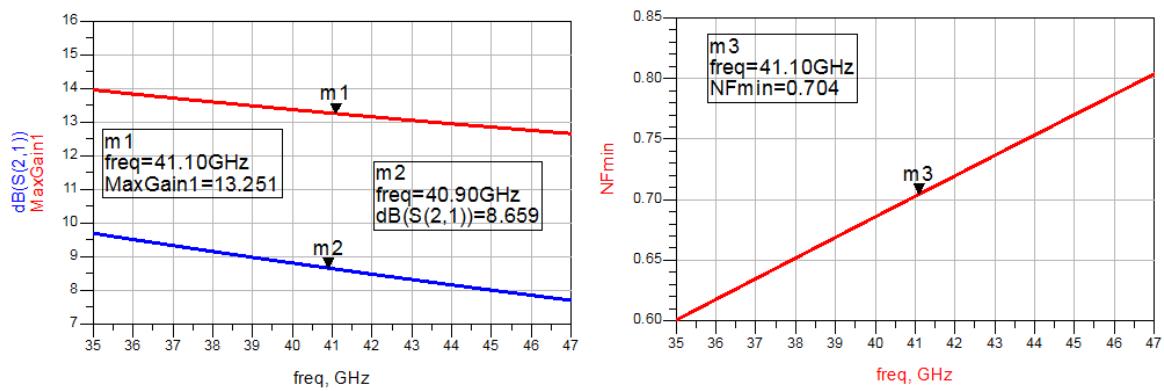

| <b>Figura 9-</b> Resultados de simulación del transistor sin realimentación. A la izquierda máxima ganancia (rojo) y ganancia disponible (azul) y a la derecha la figura de ruido mínima .....                 | 21 |

| <b>Figura 10-</b> Resultados de simulación del transistor con realimentación en fuente. A la izquierda máxima ganancia (rojo) y ganancia disponible (azul) y a la derecha la figura de ruido .....             | 22 |

| <b>Figura 11-</b> Esquema de la red de polarización.....                                                                                                                                                       | 23 |

| <b>Figura 12-</b> Comportamiento del condensador de valor $C=0.26\text{ pF}$ en el rango de frecuencias de interés (35 a 47 GHz).....                                                                          | 24 |

| <b>Figura 13-</b> Esquema eléctrico de la red de polarización del transistor .....                                                                                                                             | 25 |

| <b>Figura 14-</b> Respuesta de la red de polarización en el rango de frecuencias de interés formada a través de un condensador $C=0.26\text{ pF}$ y una línea $\lambda/4$ de 10 $\mu\text{m}$ de anchura ..... | 25 |

| <b>Figura 15-</b> Red de estabilidad.....                                                                                                                                                                      | 26 |

| <b>Figura 16-</b> Herramienta 'Impedance Matching' de ADS para la implementación de redes de adaptación .....                                                                                                  | 27 |

| <b>Figura 17-</b> Esquema eléctrico de la primera etapa amplificadora: red de entrada.....                                                                                                                     | 28 |

| <b>Figura 18-</b> Adaptación de entrada y salida de la primera etapa amplificadora .....                                                                                                                       | 29 |

|                                                                                                                                                        |    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|----|

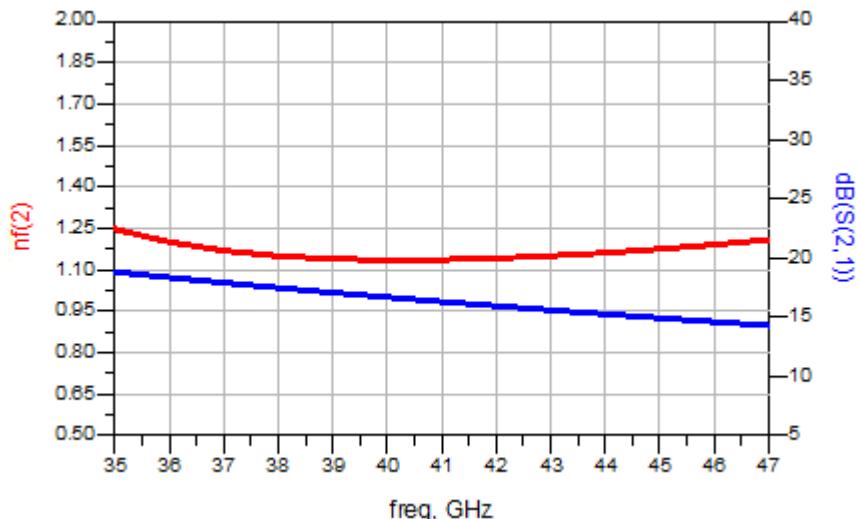

| <b>Figura 19-</b> Figura mínima de ruido (rojo) y ganancia (azul) de la primera etapa amplificadora .....                                              | 29 |

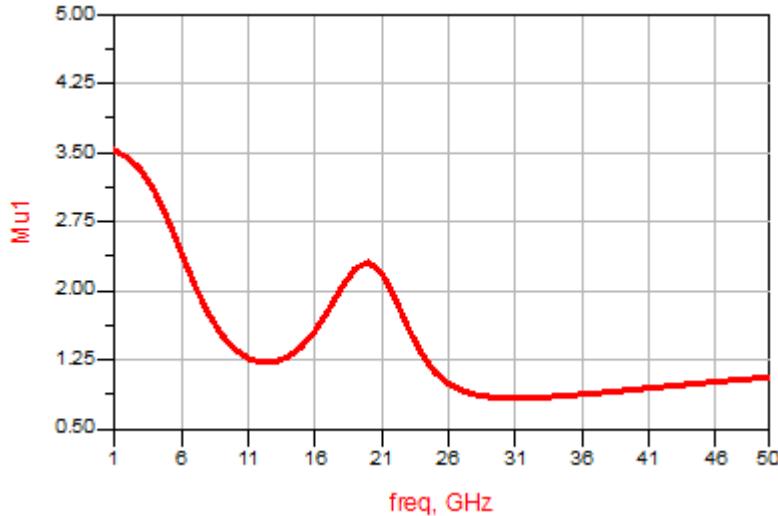

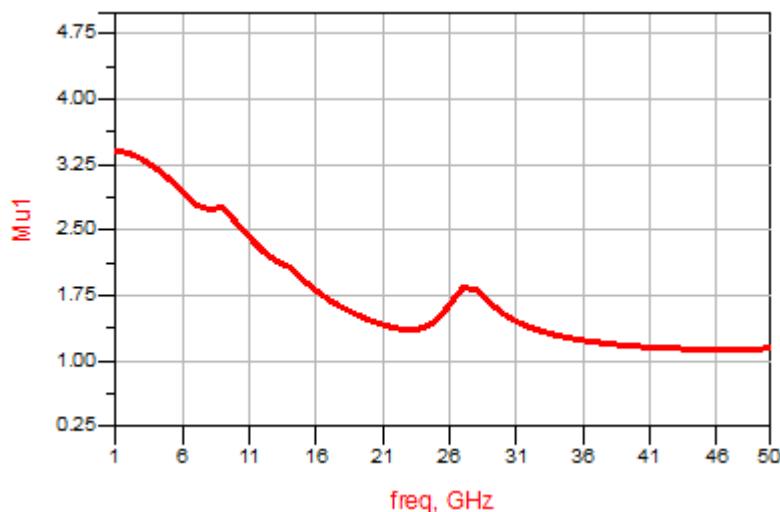

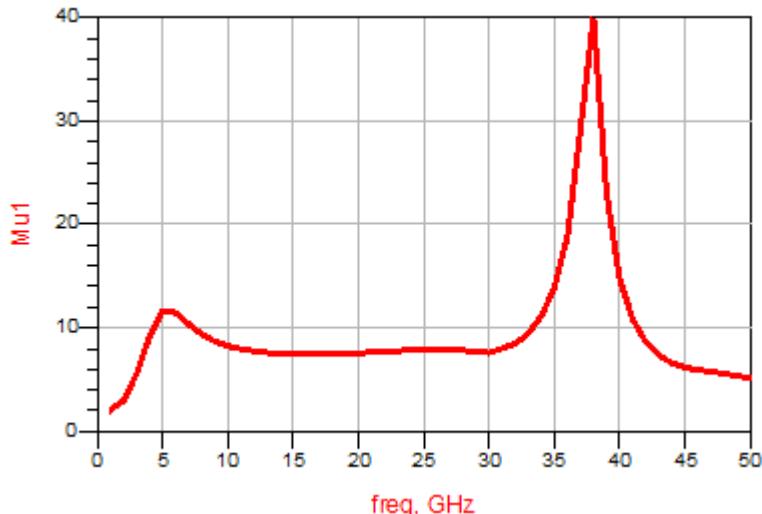

| <b>Figura 20-</b> Estabilidad de la primera etapa amplificadora a través del factor $\mu$ .....                                                        | 30 |

| <b>Figura 21-</b> Circuito eléctrico de la segunda etapa amplificadora .....                                                                           | 31 |

| <b>Figura 22-</b> Condensador de bloqueo de la DC añadido en las redes de adaptación.....                                                              | 32 |

| <b>Figura 23-</b> Adaptación de entrada y salida del amplificador con las dos primeras etapas.....                                                     | 32 |

| <b>Figura 24-</b> Figura de ruido (rojo) y ganancia en transferencia (azul) del amplificador con las dos primeras etapas .....                         | 33 |

| <b>Figura 25-</b> Estabilidad del amplificador LNA con las dos primeras etapas .....                                                                   | 33 |

| <b>Figura 26-</b> Circuito eléctrico de la red interetapa entre el 2º y 3º transistor.....                                                             | 34 |

| <b>Figura 27-</b> Adaptación de entrada y salida del amplificador con las tres primeras etapas.....                                                    | 34 |

| <b>Figura 28-</b> Figura de ruido (rojo) y ganancia en transferencia (azul) del amplificador con las tres primeras etapas .....                        | 35 |

| <b>Figura 29-</b> Estabilidad del amplificador LNA con las tres primeras etapas.....                                                                   | 35 |

| <b>Figura 30-</b> Circuito eléctrico de la última etapa del amplificador.....                                                                          | 36 |

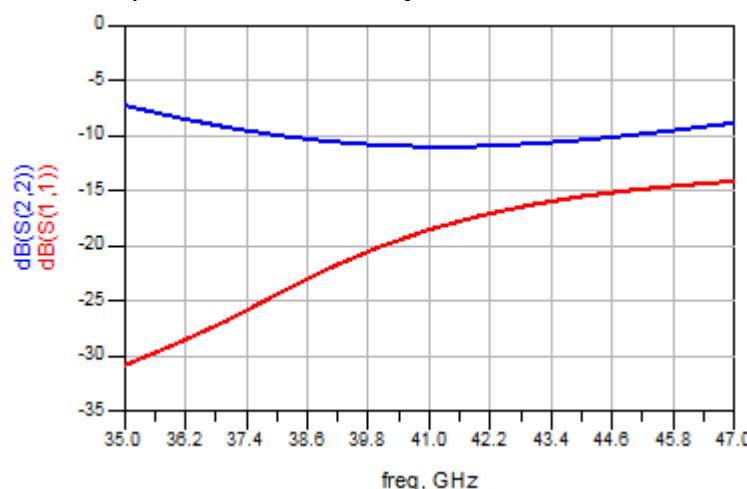

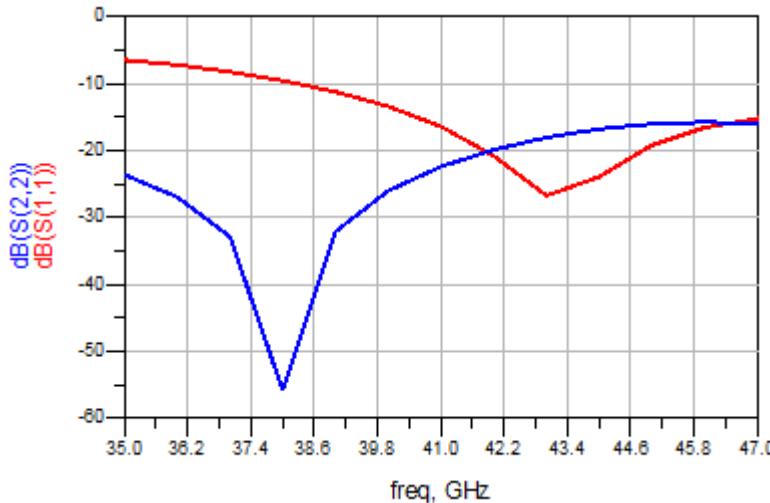

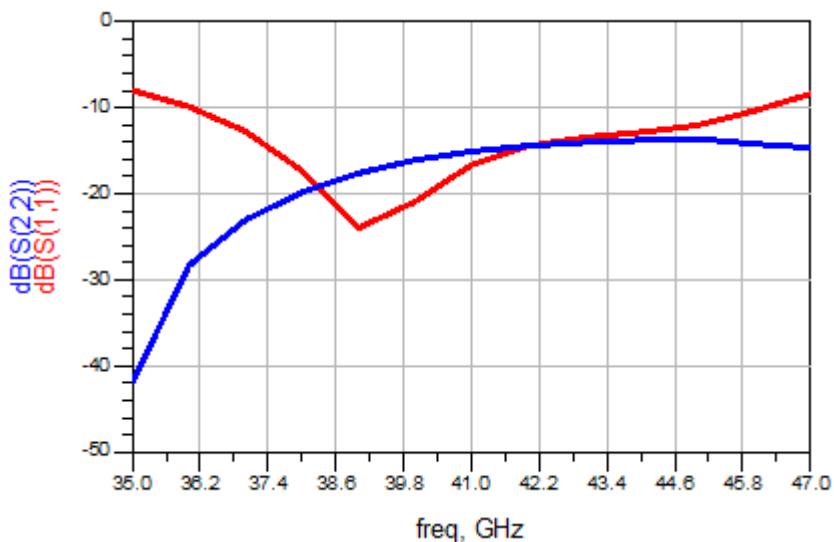

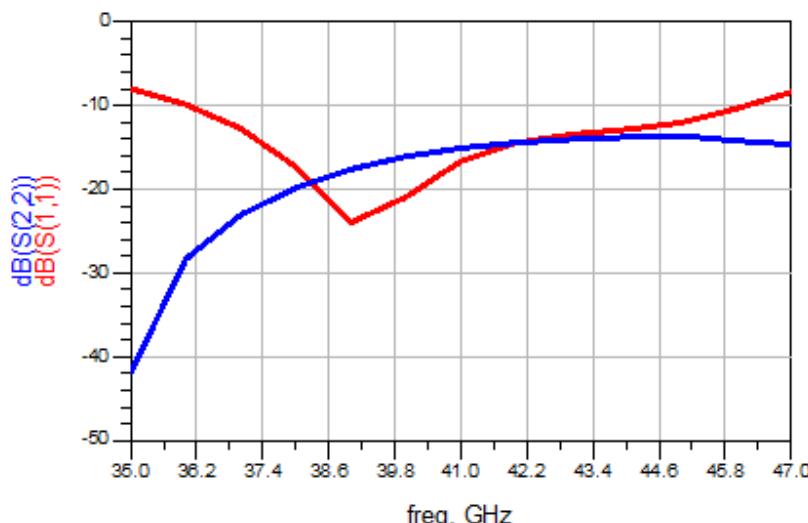

| <b>Figura 31-</b> Adaptación de entrada y salida del amplificador con las cuatro etapas.....                                                           | 36 |

| <b>Figura 32-</b> Figura de ruido (rojo) y ganancia en transferencia (azul) del amplificador con las cuatro etapas.....                                | 37 |

| <b>Figura 33-</b> Estabilidad del amplificador con cuatro etapas.....                                                                                  | 37 |

| <b>Figura 34-</b> Ejemplo de un meandro en sustitución a una línea de transmisión recta .....                                                          | 38 |

| <b>Figura 35-</b> Capas del sustrato definido para simulaciones electromagnéticas.....                                                                 | 40 |

| <b>Figura 36-</b> Estructuras de capas de condensador sin añadir la capa CG .....                                                                      | 41 |

| <b>Figura 37-</b> Estructuras de capas de condensador añadiendo la capa CG .....                                                                       | 41 |

| <b>Figura 38-</b> Layout de la red de entrada.....                                                                                                     | 42 |

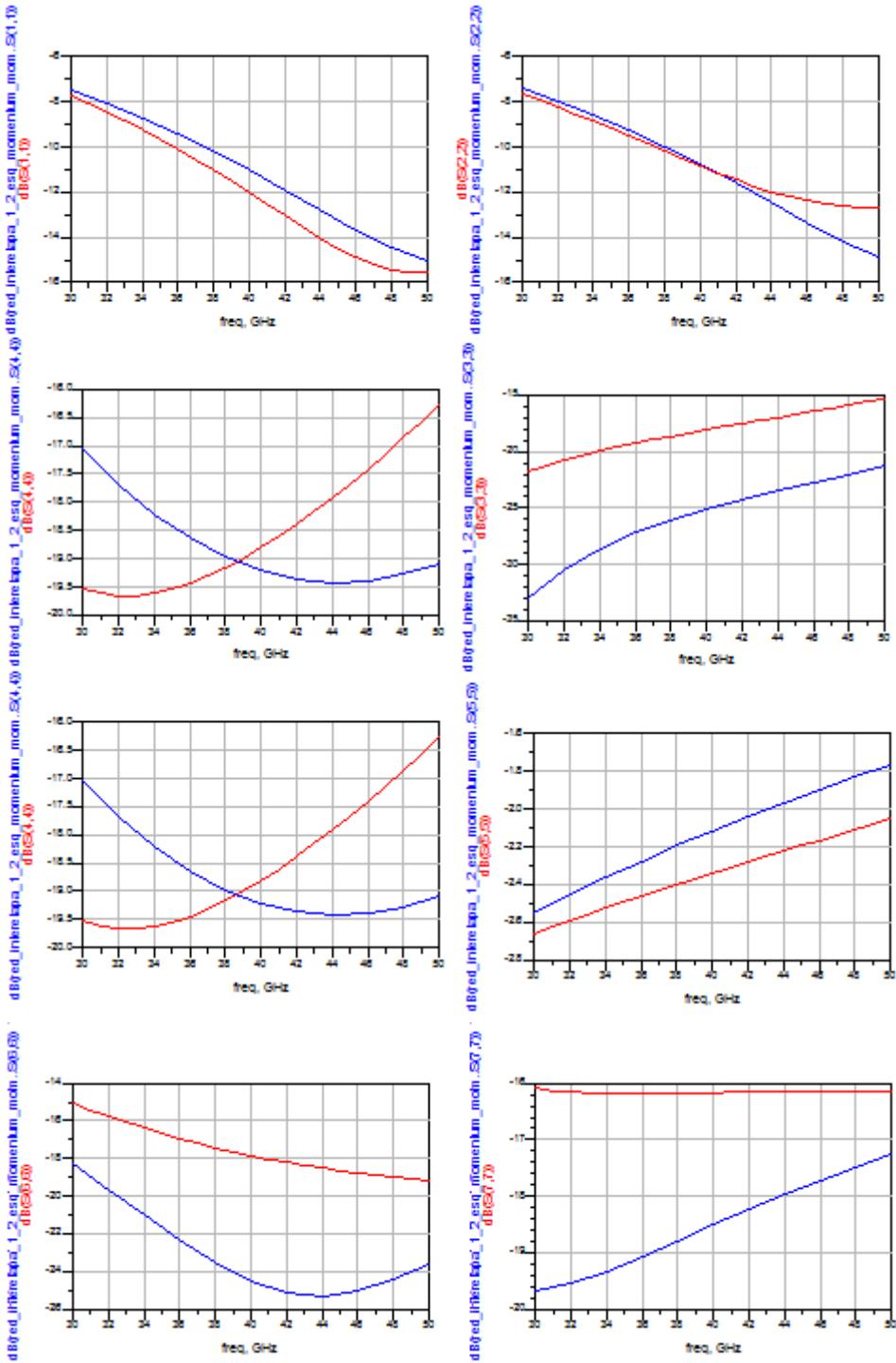

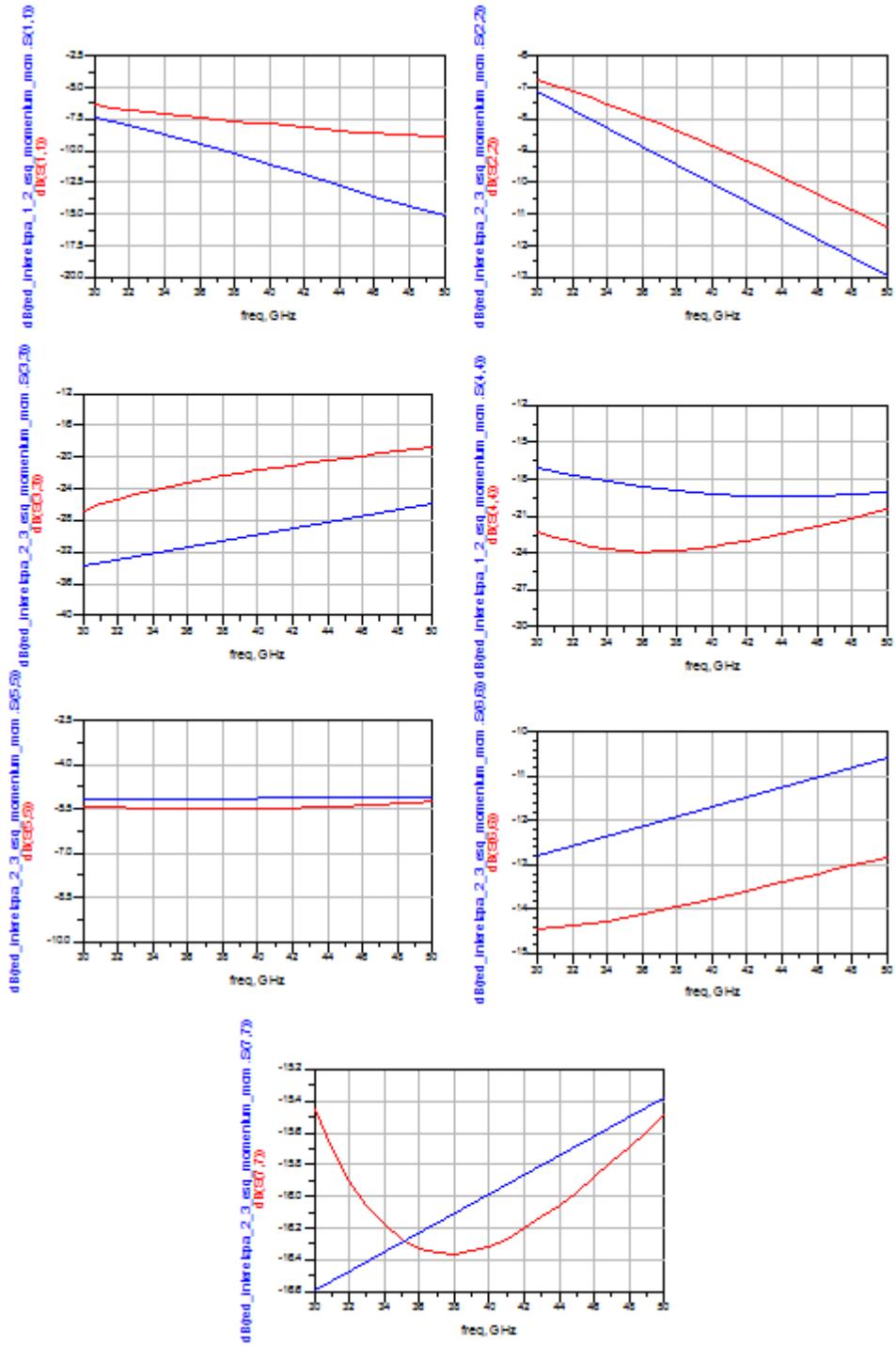

| <b>Figura 39-</b> Comparativa simulación electromagnética (azul) y simulación en esquemático (rojo) de la red de entrada.....                          | 43 |

| <b>Figura 40-</b> Adaptación de entrada (rojo) y adaptación de salida (azul) incluyendo la simulación electromagnética de la red de entrada.....       | 44 |

| <b>Figura 41-</b> Figura mínima de ruido (rojo) y ganancia en transferencia (azul) incluyendo la simulación electromagnética de la red de entrada..... | 44 |

| <b>Figura 42-</b> Factor de estabilidad $\mu$ de la red de entrada .....                                                                               | 45 |

|                                                                                                                                                                    |    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| <b>Figura 43-</b> Layout de la red que conecta al transistor nº1 con el nº 2 .....                                                                                 | 45 |

| <b>Figura 44-</b> Comparativa simulación electromagnética (azul) y simulación en esquemático (rojo) de la red que conecta al transistor nº1 con el nº 2.....       | 46 |

| <b>Figura 45-</b> Figura de ruido (rosa) y ganancia en transferencia (azul) incluyendo la simulación electromagnética de la red que conecta transistor 1 y 2.....  | 47 |

| <b>Figura 46-</b> Adaptación de entrada (rojo) y adaptación de salida (azul) incluyendo la simulación electromagnética de la red que conecta transistor 1 y 2..... | 47 |

| <b>Figura 47-</b> Factor de estabilidad $\mu$ incluyendo la red que conecta transistor 1 y 2 .....                                                                 | 48 |

| <b>Figura 48-</b> Layout de la red que conecta al transistor nº 2 con el nº 3 .....                                                                                | 48 |

| <b>Figura 49-</b> Comparativa simulación electromagnética (azul) y simulación en esquemático (rojo) de la red que conecta transistor 2 y 3 .....                   | 49 |

| <b>Figura 50-</b> Figura de ruido (rojo) y ganancia en transferencia (azul) incluyendo la simulación electromagnética de la red que conecta transistor 2 y 3.....  | 50 |

| <b>Figura 51-</b> Adaptación de entrada (rojo) y adaptación de salida (azul) incluyendo la simulación electromagnética de la red que conecta transistor 2 y 3..... | 50 |

| <b>Figura 52-</b> Factor de estabilidad $\mu$ incluyendo la red que conecta transistor 2 y 3 .....                                                                 | 51 |

| <b>Figura 53-</b> Layout de la red que conecta al transistor nº 3 con el nº 4 .....                                                                                | 51 |

| <b>Figura 54-</b> Comparativa simulación electromagnética (azul) y simulación en esquemático (rojo) de la red que conecta transistor 3 y 4 .....                   | 52 |

| <b>Figura 55-</b> Figura de ruido (rojo) y ganancia en transferencia (azul) incluyendo la simulación electromagnética de la red que conecta transistor 3 y 4.....  | 53 |

| <b>Figura 56-</b> Adaptación de entrada (rojo) y adaptación de salida (azul) incluyendo la simulación electromagnética de red que conecta transistor 3 y 4.....    | 53 |

| <b>Figura 57-</b> Factor de estabilidad $\mu$ incluyendo la red que conecta transistor 2 y 3 .....                                                                 | 54 |

| <b>Figura 58-</b> Layout de la red de salida .....                                                                                                                 | 54 |

| <b>Figura 59-</b> Figura de ruido (rojo) y ganancia en transferencia (azul) incluyendo la simulación electromagnética de la red de salida.....                     | 55 |

| <b>Figura 60-</b> Adaptación de entrada (rojo) y adaptación de salida (azul) incluyendo la simulación electromagnética de la red de salida.....                    | 55 |

| <b>Figura 61-</b> Factor de estabilidad $\mu$ con la red de salida.....                                                                                            | 56 |

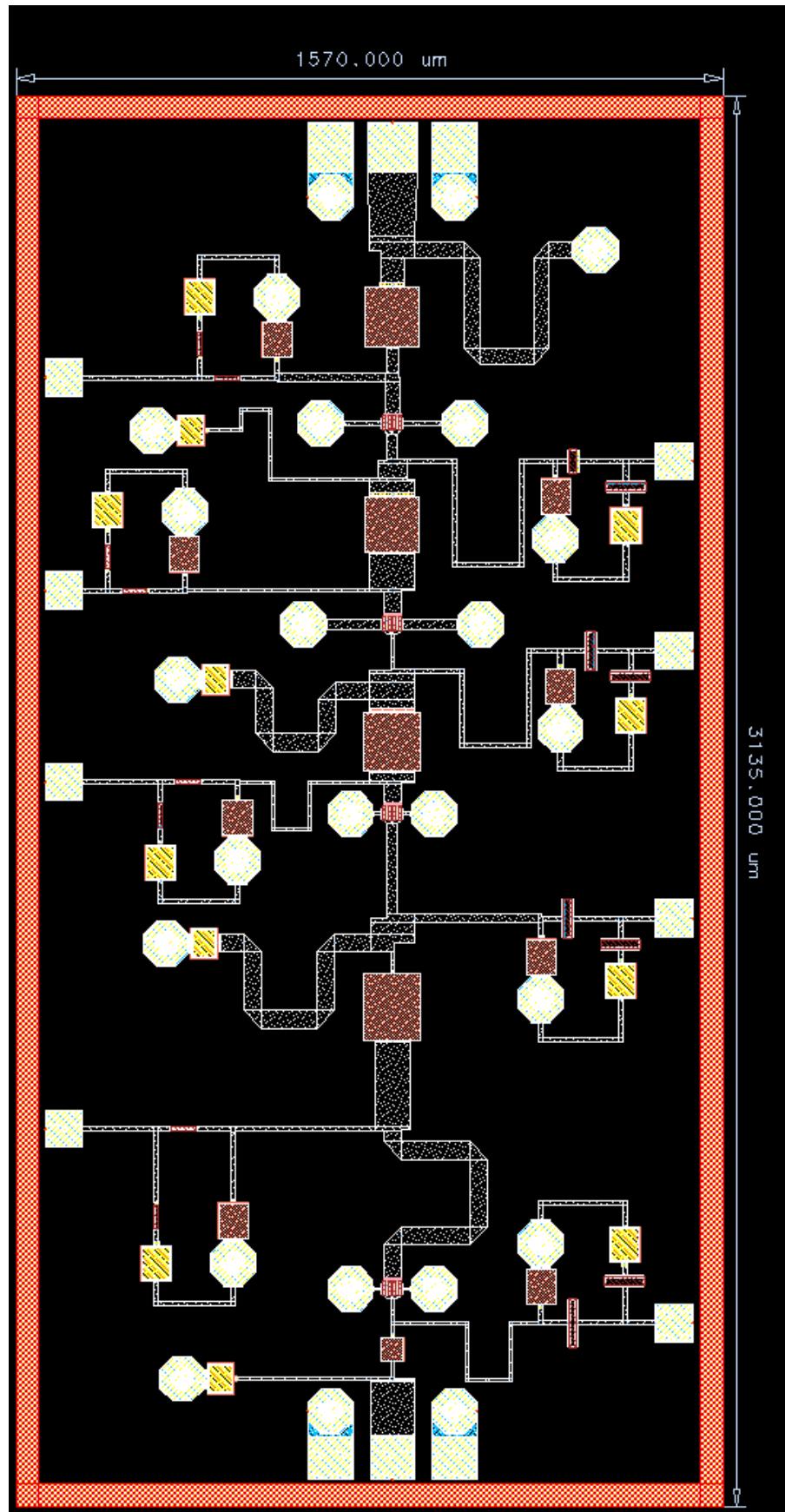

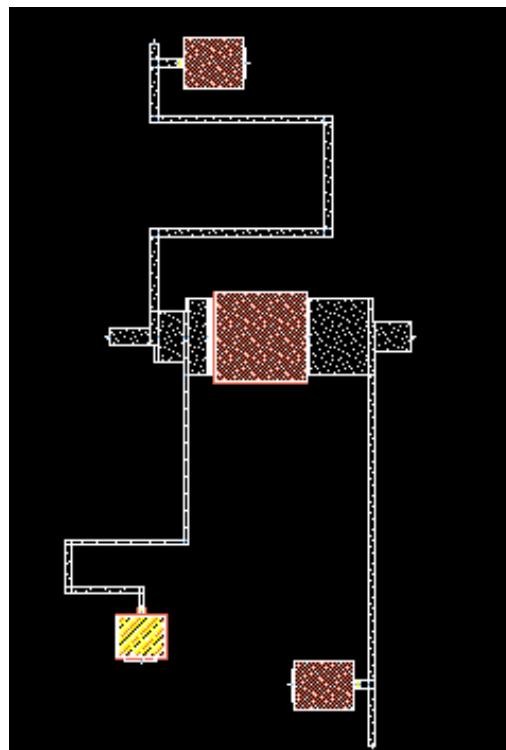

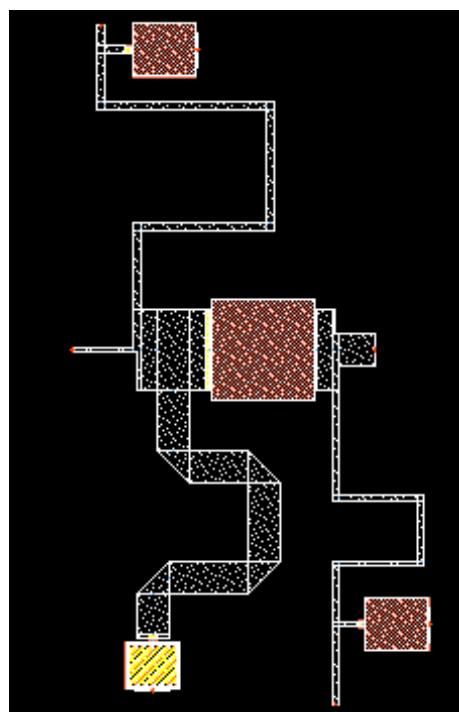

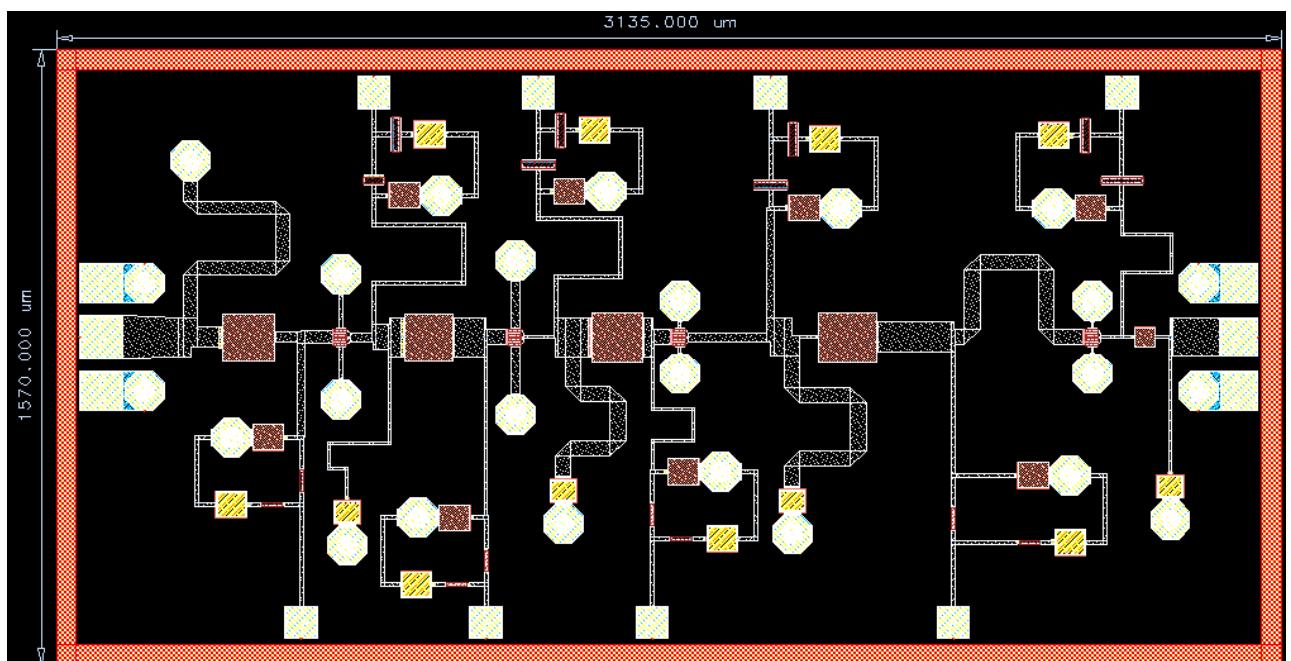

| <b>Figura 62-</b> Layout del amplificador de bajo ruido (LNA) .....                                                                                                | 57 |

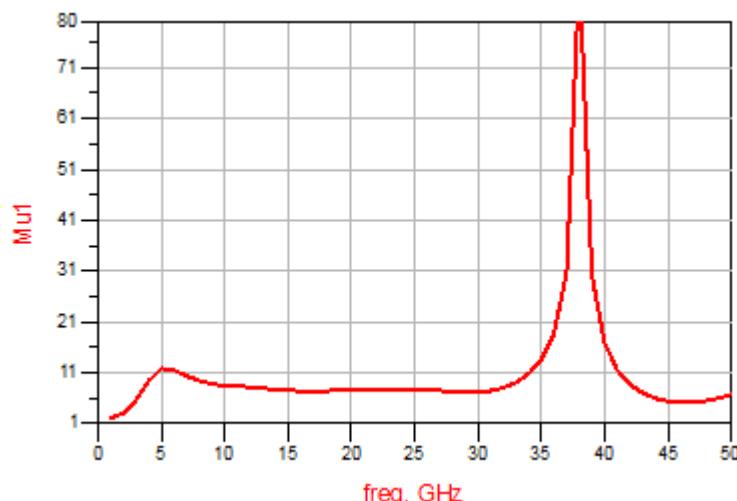

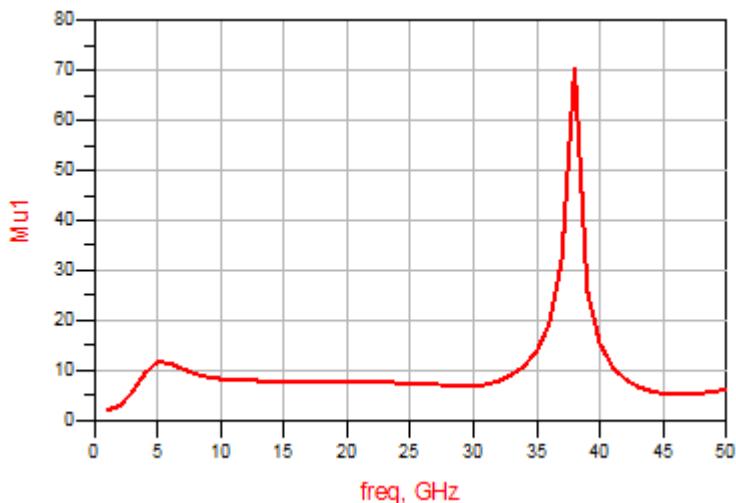

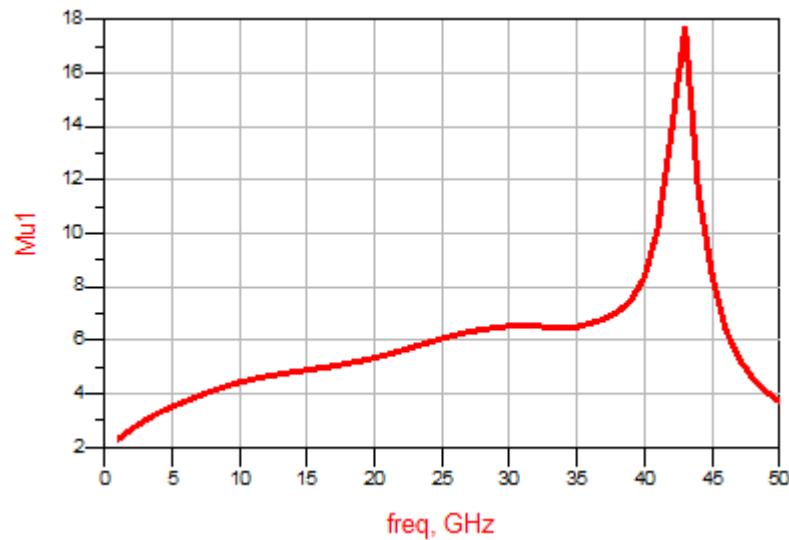

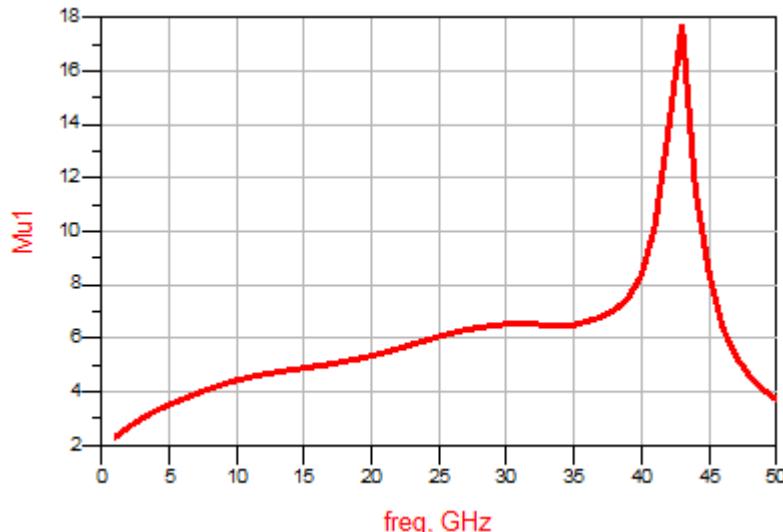

| <b>Figura 63-</b> Factor de estabilidad $\mu$ del LNA tras simulación electromagnética .....                                                                       | 58 |

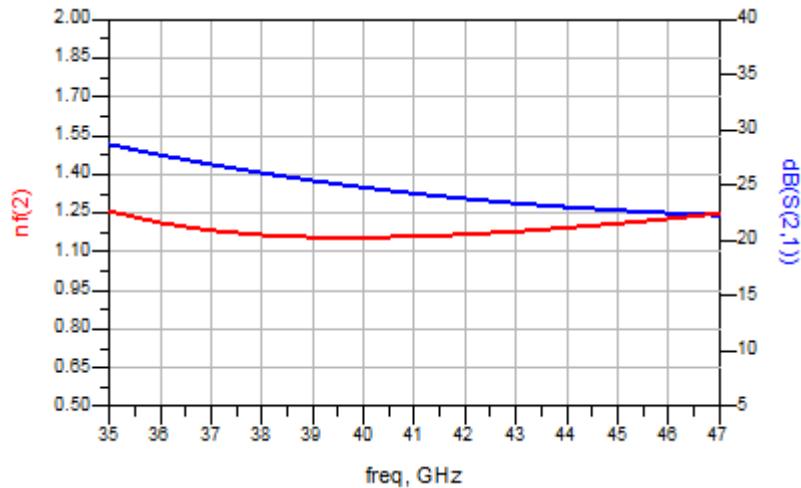

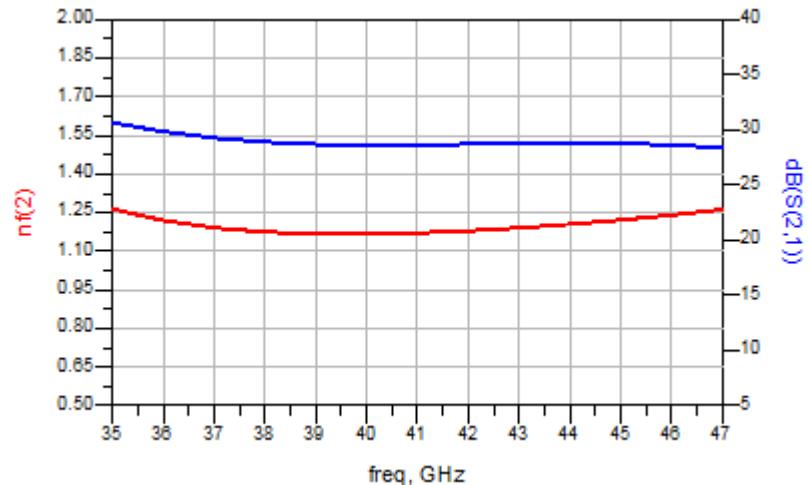

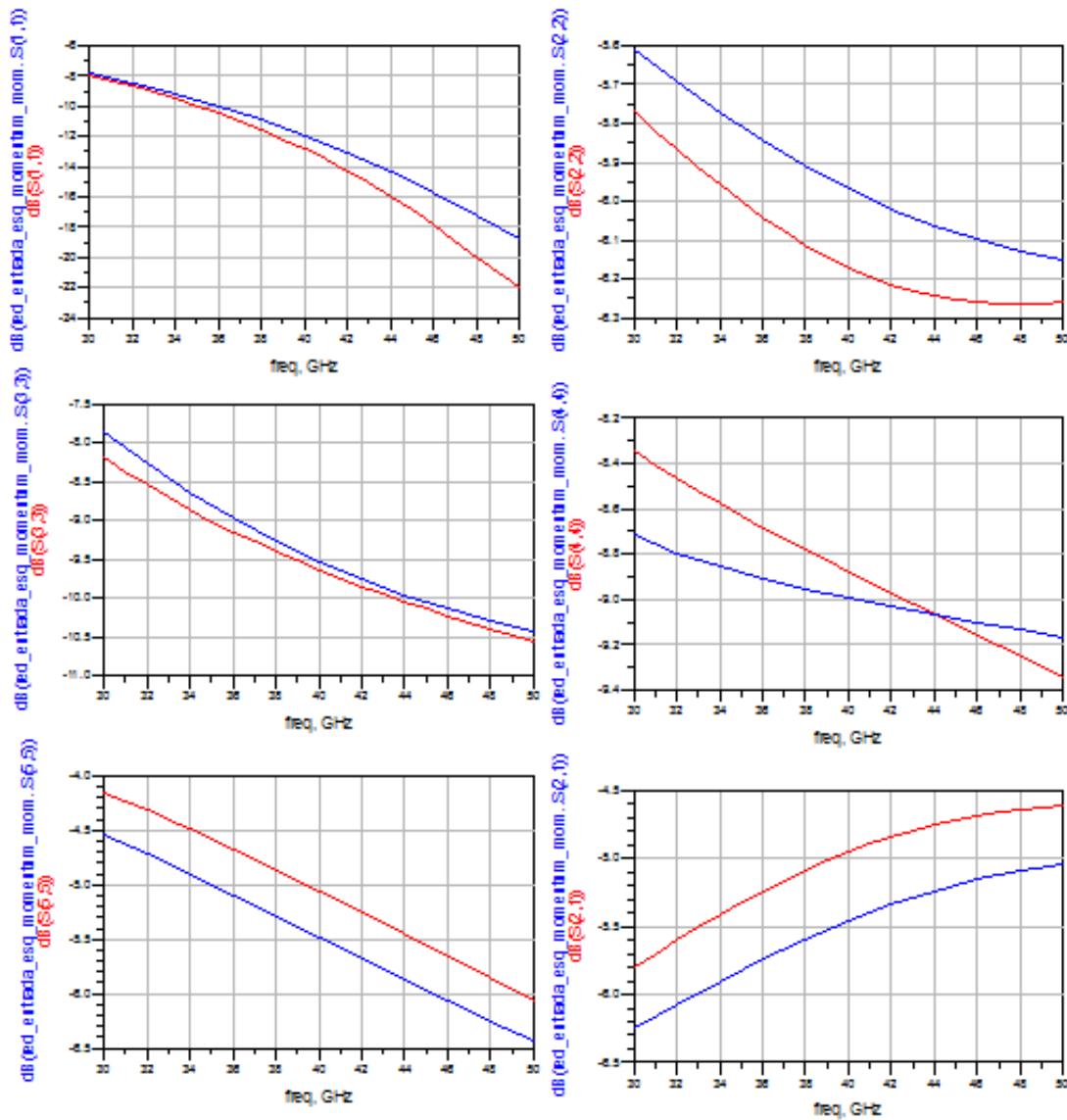

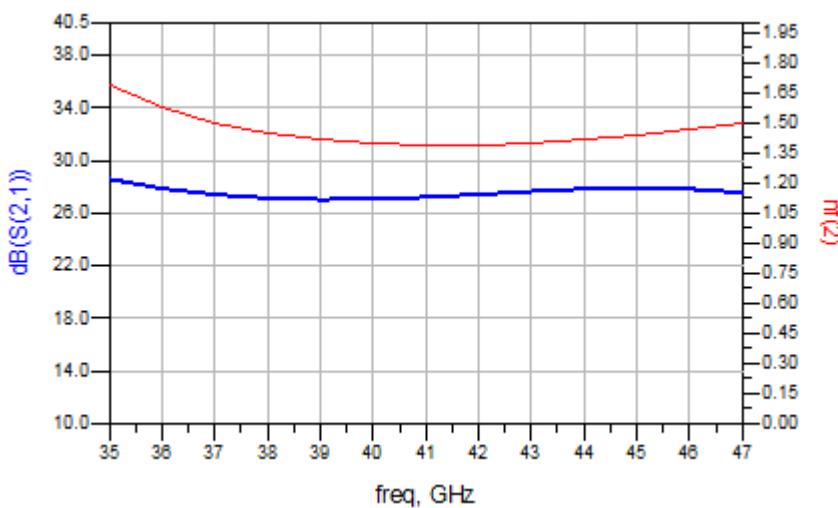

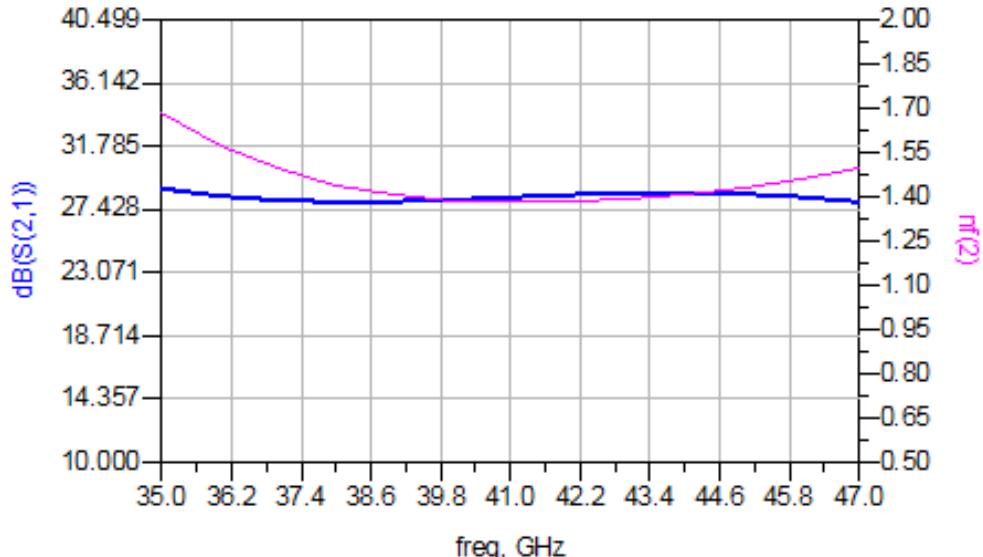

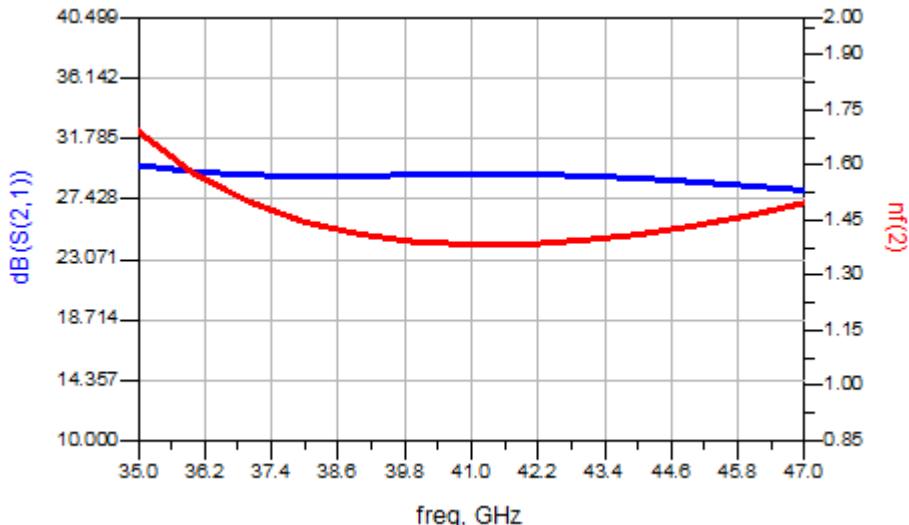

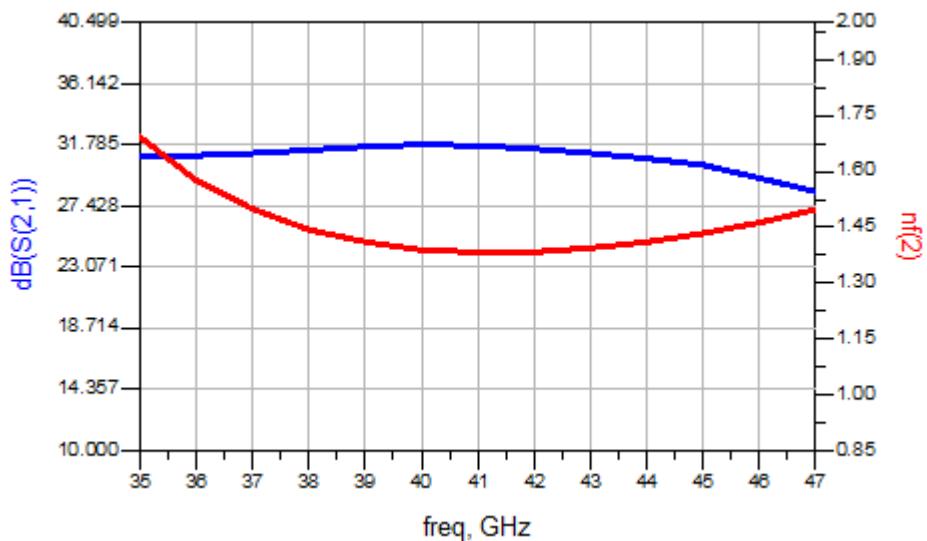

**Figura 64-** Ganancia en transferencia S21 (azul) y figura de ruido (rojo) del LNA tras simulación electromagnética ..... 59

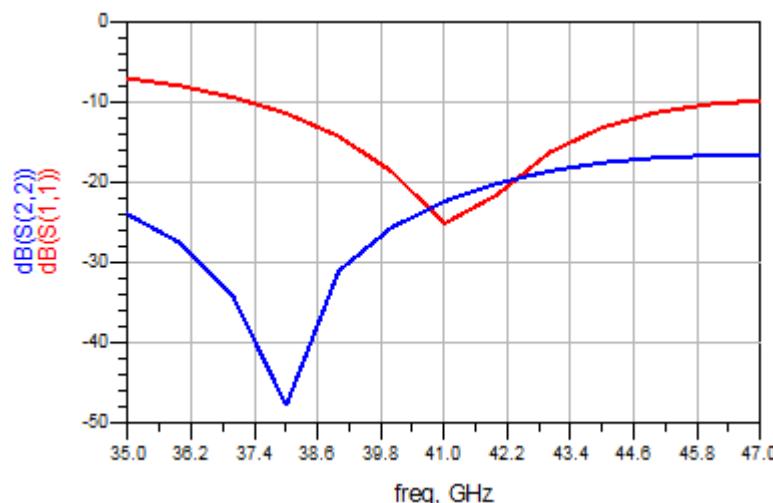

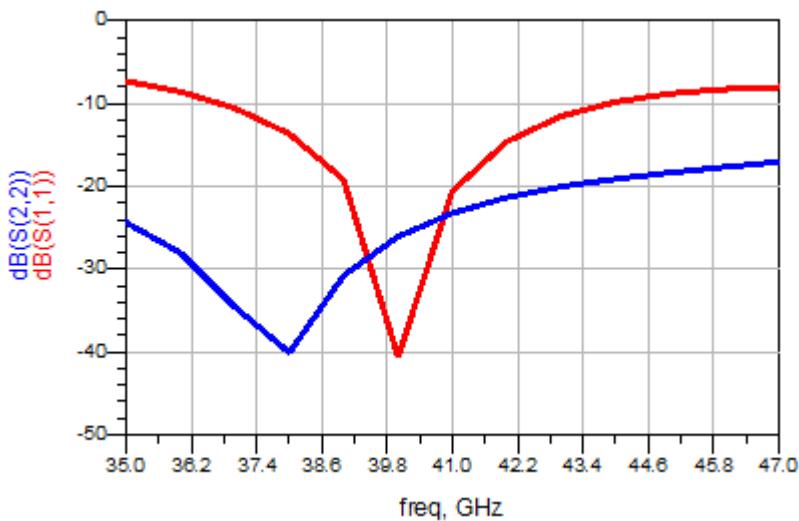

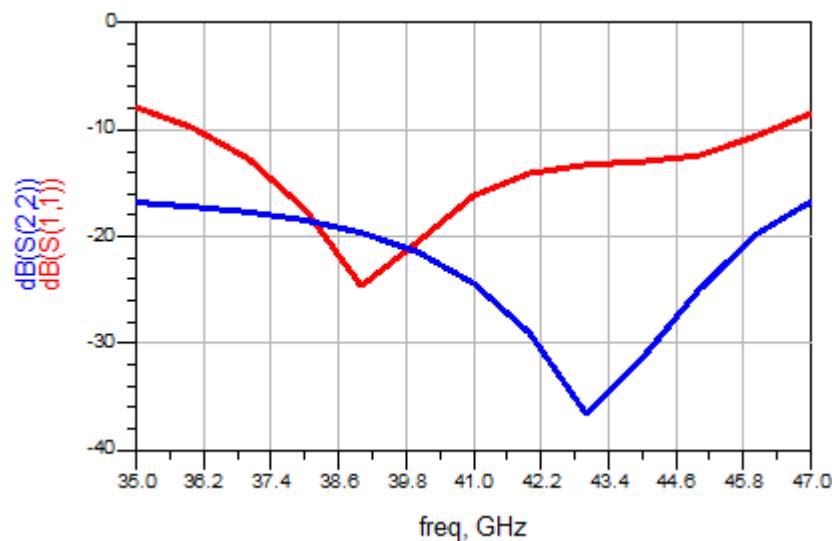

**Figura 65-** Adaptación de entrada (azul) y adaptación de salida (rojo) del LNA tras simulación electromagnética ..... 59

# Índice de tablas

**Tabla 1.** Ventajas y desventajas de la tecnología híbrida frente a la monolítica ..... 15

**Tabla 2.** Valores adecuados de polarización y tamaño del transistor según las simulaciones ..... 19

**Tabla 3.** Valores finales de polarización y tamaño del transistor ..... 19

**Tabla 4.** Comparativa de las especificaciones de diseño y resultados obtenidos (valores medios, excepto  $\mu$  que es valor mínimo en toda la banda) ..... 39

**Tabla 5.** Comparativa entre especificaciones de diseño y valores medios obtenidos en la banda tanto en esquemático como en momentum ..... 62

# 1. Introducción

El presente trabajo de fin de grado consiste en el diseño de un amplificador de bajo ruido (LNA) en la banda de frecuencias que va desde 35 a 47 GHz. Estos dispositivos electrónicos son utilizados a menudo para amplificar señales que llegan con una potencia muy débil, por lo tanto en el diseño del amplificador es muy importante conseguir el mínimo ruido posible.

Según la fórmula de Friis (1) que se utiliza para calcular el factor de ruido total de un numero de etapas en serie.

$$F_{sys} = F_1 + \frac{F_2 - 1}{G_1} + \frac{F_3 - 1}{G_1 G_2} + \dots + \frac{F_n - 1}{G_1 G_2 \dots G_{n-1}} \quad (1)$$

Donde  $F_n$  y  $G_n$  son el factor de ruido y la ganancia disponible respectivamente, de cada etapa.

La fórmula de Friis expresa información relevante a la hora del diseño del amplificador LNA, y es que como se puede observar en la expresión, el ruido total del sistema es la suma del ruido de cada etapa del amplificador, pero además se observa que es la primera etapa la más crítica en cuanto a nivel de ruido, puesto que en las siguientes etapas la ganancia de las etapas anteriores ( $G$ ) va atenuando el ruido ( $F$ ).

Por lo tanto a la hora del diseño del amplificador se deberá tener especial cuidado con el diseño de la red de entrada y en menor medida, de la segunda etapa para conseguir el menor factor de ruido del amplificador, puesto que el factor de ruido total dependerá principalmente de las dos primeras etapas.

Otra requisito también importante es la ganancia, que deberá ser lo más alta posible para así reducir el posible ruido que vayan introduciendo los circuitos posteriores a este amplificador.

## 2. Objetivos y línea de trabajo

Este proyecto fin de grado tiene como objetivo principal el diseño de un amplificador de bajo ruido (LNA) utilizando tecnología monolítica (MMIC), diseñado para trabajar en un amplio rango de la banda Q que va desde 30 a 50 GHz, en particular desde 35 a 47 GHz.

Para el diseño del amplificador se ha utilizado el proceso D007IH de OMMIC. En este proceso se utilizan estructuras metamórficas para conseguir una transición gradual entre el sustrato de AsGa y la capa activa, presentando bajos niveles de ruido.

El amplificador LNA a diseñar tiene como principales objetivos cumplir con las siguientes especificaciones:

- Ser incondicionalmente estable en todo el rango de frecuencias.

- Bajo nivel de ruido en la banda de trabajo, por debajo de los 2.8 dB.

- Ganancia ecualizada por encima de 25 dB en la banda de trabajo.

- Adaptación de entrada y salida mejor de -10 dB en la banda de trabajo.

Para lograr estos objetivos se ha seguido una línea de trabajo, que coincide con la estructura con la cual se ha elaborado esta memoria. A continuación se exponen los diferentes capítulos que componen la memoria y en los cuales se describe paso a paso el proceso seguido en el diseño del amplificador LNA.

- **Introducción:** Se realiza una breve descripción a grandes rasgos del diseño que se va a realizar.

- **Objetivos y línea de trabajo:** Se especifica los objetivos generales del diseño así como la estructura que se ha seguido.

- **Tecnología a utilizar:** Se presenta el proceso tecnológico de la fundición OMMIC con el cual se ha realizado el diseño y además se realiza una comparación entre los dos tipos de circuitos integrados (MIC y MMIC).

- **Diseño:** Se detalla paso a paso el proceso de diseño eléctrico como electromagnético del amplificador de bajo ruido.

- **Conclusiones:** Se realiza un análisis de todo el trabajo realizado con el fin de evaluar los resultados obtenidos y extraer unas conclusiones.

- **Bibliografía:** Se encuentran las referencias bibliográficas que se han consultado en la realización tanto del diseño como de la memoria.

# 3. Tecnología utilizada

## 3.1 Proceso D007IH de OMMIC

Para el diseño del amplificador LNA se ha elegido el proceso D007IH de la fundición OMMIC. Es una tecnología francesa y en la que algunas de sus características principales se resumen bajo sus siglas:

- D porque son transistores de deplexión.

- 007 porque la longitud de puerta del transistor es de 70 nanómetros.

- IH porque los transistores son HEMT con dopado de fosfuro de indio (InP) en la capa activa.

El uso de este dopado de fosfuro de indio (InP) en la capa activa, hace que esta tecnología sea muy útil para aplicaciones que requieran muy bajo ruido y además permite el diseño de circuitos a altas frecuencias (aproximadamente hasta 180 GHz). Otros datos relevantes de este proceso son que la frecuencia de corte  $f_t$  es de 300 GHz y la frecuencia máxima de oscilación  $f_{max}$  es de 450 GHz.

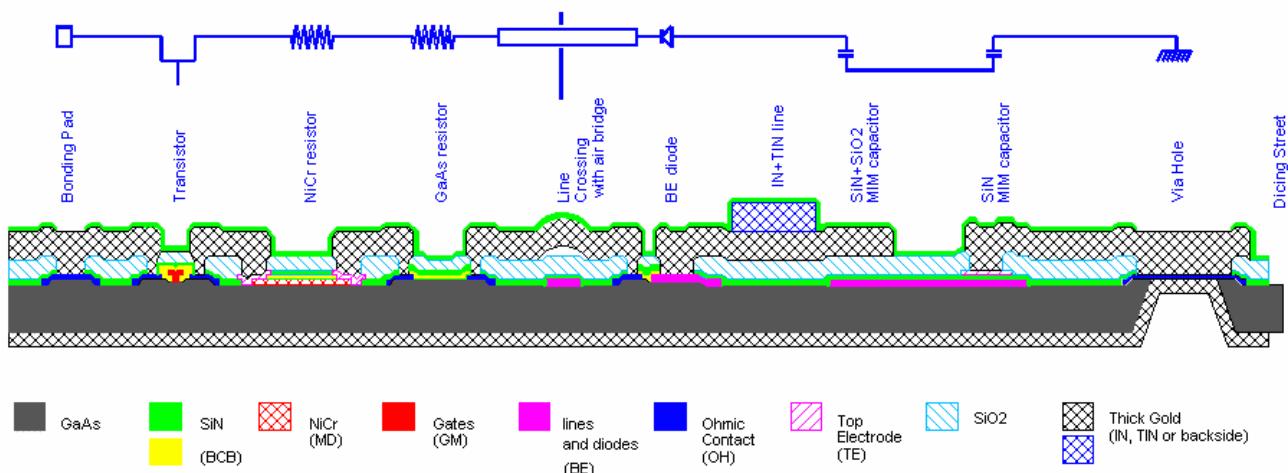

En figura 1, se observa un esquema de cómo se forman los distintos componentes dentro del proceso D0071IH, en él se pueden observar transistores, líneas de transmisión o condensadores que luego se utilizan en el diseño del LNA.

Figura 1. Perfil de las capas del proceso D007IH de OMMIC.

## 3.2 Definición del sustrato

OMMIC ofrece al usuario una serie de librerías de simulación, en donde se especifican las características de cada uno de los componentes electrónicos que existen en el proceso. Para que la simulación electromagnética tenga un comportamiento muy similar al diseño realizado, es necesario definir de forma adecuada la estructura de capas del proceso.

Existen varios simuladores para el diseño de circuitos de radiofrecuencia como pueden ser Genesys, Orcad, ADS, ...etc. En este caso para el diseño del LNA se ha optado por utilizar el simulador ADS (Advanced Desing System) de la empresa Keysight.

Este simulador es muy potente y nos permite realizar simulaciones tanto a nivel de circuito eléctrico como a nivel electromagnético. En este proyecto se realizarán ambas simulaciones y para la parte de simulaciones electromagnéticas, que también recibe el nombre de Momentum por el método de simulación que utiliza, se definirán las capas que componen el sustrato.

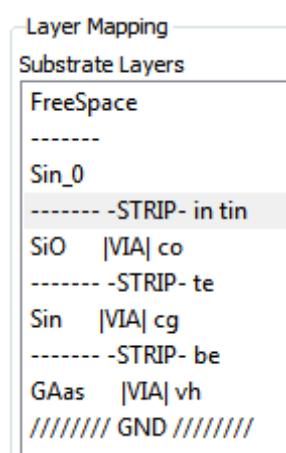

En la figura 2 vienen definidas las diferentes capas del sustrato utilizado para la simulación electromagnética del amplificador de bajo ruido, desde la primera y más externa capa llamada FreeSpace (espacio libre) hasta GND (tierra).

Figura 2. Distribución de capas del sustrato utilizado para simulaciones electromagnéticas para la tecnología D007IH de OMMIC.

A continuación se detallan con más precisión las diferentes capas del proceso D007IH que definen el sustrato utilizado en las simulaciones electromagnéticas realizadas en este proyecto.

- Entre la primera capa de nitruro de silicio (SiN<sub>0</sub>) y la capa de óxido de silicio van situadas las dos capas conductoras más externas IN y TIN. La capa IN es la segunda capa metálica de interconexión de TiPtAu con espesor de 1.25 µm. La capa TIN es una capa adicional a la capa IN del mismo material y del mismo espesor.

- En la siguiente capa que es la de óxido de silicio (SiO), donde se pueden realizar vías o agujeros pasantes para interconectar las capas IN y TIN con la siguiente capa conductora (TE). Este vía está definido como un hueco en la capa CO. Esta capa está formada por una deposición dieléctrica de óxido de silicio de espesor 0.8 µm en la oblea.

- La siguiente es TE, que forma el electrodo superior de los electrodos de los condensadores MIM. También se usa como protección entre las puertas de TiAl y las líneas de oro (Au), que garantiza una alta fiabilidad en la conexión. El espesor de esta capa es de 0.560 µm.

- A continuación de la capa TE, se encuentra la segunda capa de nitruro de silicio (SiN), sobre el que se pueden implementar otro vías con la máscara CG que está formada por una capa negativa de nitruro de silicio (Si<sub>3</sub>N<sub>4</sub>) y sirve como interconexión entre metales.

- La anteúltima capa es la BE formada por TiPtAu que es una metalización usada para formar el electrodo inferior de los condensadores MIM. También se usa en los diodos de 3 µm de longitud de puerta. El espesor de esta capa es de 0.650µm.

- Por último esta la capa de GaAs mapeada como vía para permitir la definición de pasos a la masa del plano inferior (vh).

Existen otras capas definidas dentro del proceso D007IH de OMMIC como es el caso de: LI, MD, OH, BCB etc., pero no han sido introducidas en el sustrato debido a que en las simulaciones electromagnéticas realizadas sobre el amplificador LNA en este caso no son necesarias. Es el caso por ejemplo de la capa MD que es utilizada para la simulación de resistencias, pero que en nuestro caso no se va hacer, o de otras capas utilizadas para la simulación de elementos activos como son los transistores.

### 3.3 MMIC vs MIC

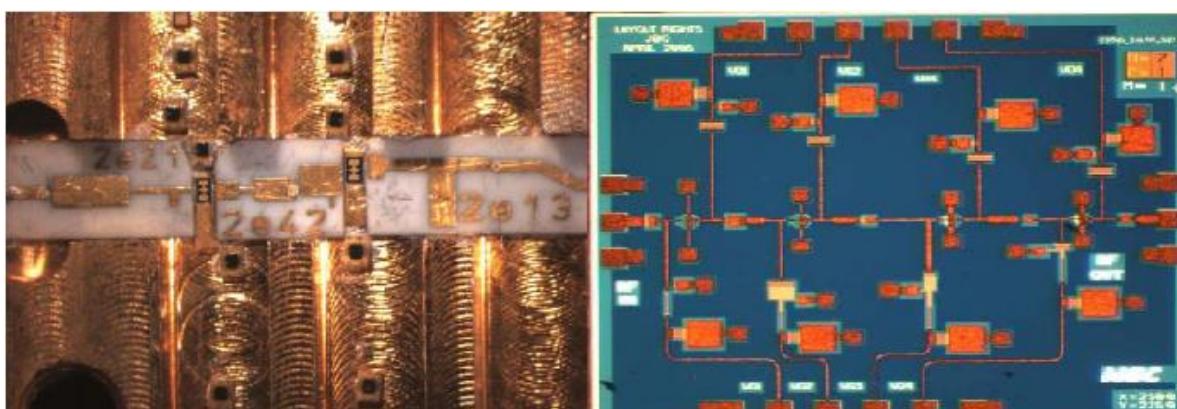

La evolución tecnológica que han sufrido los distintos dispositivos activos de microondas ha permitido una mayor integración de los componentes, y con ello una reducción considerable del tamaño de los circuitos. Como consecuencia de esto se obtienen dispositivos más reducidos, compactos y portables.

A continuación se explican las dos principales tecnologías utilizadas en el diseño de amplificadores de bajo ruido LNA: MIC (Microwaves Integrated Circuits ) y MMIC (Monolithic Microwave Integrated Circuits).

En primer lugar aparecieron los circuitos integrados MIC, que son circuitos híbridos donde algunos elementos aparecen impresos en el sustrato, y otros componentes discretos se encuentran conectados al sustrato mediante soldadura o algún material adhesivo que permita la conducción eléctrica. Posteriormente aparecieron los circuitos monolíticos integrados MMIC, que son circuitos en donde todos los componentes se integran dentro de un sustrato semiconductor.

La tecnología híbrida tiene algunas ventajas sobre la tecnología monolítica, como es la utilización de componentes discretos con una alta calidad, la capacidad de una vez elaborados poder realizar modificaciones o la reducción del tiempo de fabricación respecto a los circuitos MMIC, puesto que se evita su construcción en una fundición.

Aunque la principal ventaja de la tecnología híbrida es su magnífico comportamiento en aplicaciones que requieran bajo ruido, debido a las bajas pérdidas dieléctricas del sustrato dieléctrico.

En cambio, en este proyecto se ha decidido utilizar la tecnología MMIC, puesto que la banda de frecuencia en la que se diseña el amplificador LNA, hace que el montaje de dispositivos híbridos sea muy crítico y sea realmente complicado.

Como principales ventajas de la tecnología monolítica hay que citar que son circuitos mucho más pequeños, su precio en grandes cantidades es menor, y que como se ha comentado con anterioridad, la formación de los componentes se realiza en el propio sustrato semiconductor con lo cual se reduce considerablemente el tamaño del circuito. Por otro lado, el control de las conexiones de los distintos componentes que forman el circuito es mucho mayor en tecnología MMIC si se compara con la tecnología híbrida, factor muy importante en frecuencias de microondas y milimétricas.

A continuación en la Tabla 1 se muestran resumidas las principales ventajas y desventajas de cada tecnología.

|                    | <b>Híbridos (MIC)</b>                                                                                                                                                                     | <b>Monolíticos (MMIC)</b>                                                                                                                                              |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Ventajas</b>    | <ul style="list-style-type: none"> <li>• Reparación sencilla</li> <li>• Medidas fáciles</li> <li>• Líneas de bajas pérdidas</li> </ul>                                                    | <ul style="list-style-type: none"> <li>• Pequeño tamaño y peso</li> <li>• Alta fiabilidad</li> <li>• Reproducible</li> <li>• Diseño flexible</li> </ul>                |

| <b>Desventajas</b> | <ul style="list-style-type: none"> <li>• Diseño poco flexible</li> <li>• Poco reproducible</li> <li>• Tamaño grande</li> <li>• Efectos parásitos</li> <li>• Montaje alto coste</li> </ul> | <ul style="list-style-type: none"> <li>• Líneas altas pérdidas</li> <li>• Imposible el ajuste</li> <li>• Equipamiento caro</li> <li>• Limitación de valores</li> </ul> |

**Tabla 1.**Ventajas y desventajas de la tecnología híbrida frente a la monolítica

Por último se muestran unas imágenes (Figura 3) de diseño de amplificadores de bajo ruido utilizando tecnología híbrida y monolítica.

**Figura 3.** Fotografías de diseños de un amplificador LNA. A la izquierda con tecnología MIC y a la derecha con tecnología MMIC.

# 4. Diseño

En esta sección se explica en profundidad el proceso llevado a cabo para el diseño del amplificador LNA, desde el momento en el que se tienen las especificaciones de diseño hasta el momento de finalización del mismo.

## 4.1 Especificaciones de diseño

La banda de trabajo, en la cual el comportamiento del amplificador debería ser el marcado en las especificaciones previas de diseño, va desde 35 GHz a 47 GHz.

Las especificaciones previas de diseño que, que ya se han comentado con antelación, vendrán definidas por los parámetros de Scattering y el ruido del amplificador. A continuación se exponen estas especificaciones:

- Factor de estabilidad ( $\mu$ ) >1

- $|S_{11}| < -10\text{dB}$  y  $|S_{22}| < -10\text{ dB}$

- $|S_{21}| > 25\text{dB}$

- NF (Figura de ruido) < 2.8 dB

Partiendo de estas especificaciones, la primera decisión importante es el número de etapas con las que se va a diseñar el amplificador. Debido a que se requiere una ganancia considerablemente alta, se ha decidido por utilizar **4 etapas amplificadoras**, que en la parte de caracterización del transistor, se explica más detalladamente el porqué.

Otro aspecto importante es que para el diseño del LNA se ha utilizado el modelo de pequeña señal para transistores, pues es el único modelo que tiene incluida información sobre los parámetros de ruido.

## 4.2 Configuración de las etapas amplificadoras

Existen 3 topologías básicas para la configuración de un transistor: fuente común, drenador común y puerta común. En este diseño para la configuración de las etapas amplificadoras se ha utilizado la configuración en fuente común, debido principalmente a que es la que se utiliza más a menudo, y a que es la más conveniente para el diseño de nuestro LNA.

Esta configuración en fuente común (ejemplo en Figura 4) consiste en tomar como referencia el terminal de fuente conectándola a tierra. Una de las principales ventajas que permite obtener buenos niveles de ganancia.

Figura 4. Configuración en fuente común de un transistor.

## 4.3 Caracterización del transistor

Para el diseño de un amplificador de bajo ruido, es necesario conocer previamente el comportamiento de los transistores mHEMT (Metamorphic High Electron Mobility transistor), en cuanto a las prestaciones en ruido y ganancia que pueden dar en función del punto de polarización y geometría.

### 4.3.1 Análisis Corriente Continua (DC)

El primer paso para el diseño del amplificador de bajo ruido, es encontrar aquel punto de polarización del transistor que tenga un comportamiento óptimo de trabajo. Para ello se realiza un barrido de la tensión de puerta ( $V_{gs}$ ), buscando un valor adecuado para conseguir maximizar y minimizar la ganancia y el ruido del transistor respectivamente.

Con el valor de la tensión de drenador ( $V_{ds}$ ) no se realiza ningún barrido, debido a que el fabricante solo suministra parámetros de ruido para la tensión de drenador ( $V_{ds}$ ) de valor 1,2 V.

Para tener un punto de partida del tamaño de los transistores, se realiza una simulación para obtener el número de dedos ( $nd$ ) y su correspondiente anchura ( $wd$ ), para los cuales se obtenga el mejor comportamiento en cuanto a ganancia y ruido. Para esta simulación, según la librería de componentes del proceso D007IH de OMMIC, el número de dedos pueden tomar los siguientes valores 2, 4, 6 y 8, en cuanto a la anchura de dedo debe valer entre 10  $\mu\text{m}$  y 75  $\mu\text{m}$ .

Según los resultados obtenidos (Figura 5), se han escogido para el diseño del amplificador LNA de este proyecto transistores de 4 x 20  $\mu\text{m}$  (4 dedos de 20  $\mu\text{m}$  de anchura cada uno). La simulación se ha realizado a la frecuencia intermedia de 41 GHz y para anchuras de menos de 35  $\mu\text{m}$  para una mejor visualización, puesto que para anchuras superiores el comportamiento se degradaba.

Figura 5. Resultados de figura de ruido y ganancia del estudio del tamaño del transistor.

Una vez obtenido el tamaño del transistor, se calcula mediante simulación el valor adecuado de la tensión de puerta ( $V_{gs}$ ) del transistor, del mismo modo que se realizó con la geometría del transistor.

En la Figura 6 se muestra la evolución de la ganancia y el ruido con la tensión de puerta del transistor. Se puede observar como el mínimo ruido,  $NF=0.827$  dB, se obtiene para una tensión de puerta de  $V_{gs}=-0.1$  V. Bajo esas mismas condiciones de tensión se obtiene una ganancia máxima de 12.5 dB.

**Figura 6.** Resultados de ganancia y figura de ruido del estudio de la polarización del transistor.

En resumen, los valores escogidos del punto de polarización y de tamaño del transistor son los mostrados en la Tabla 2.

| $V_{gs}$ | $V_{ds}$ | $N_d$ | $W_d$      |

|----------|----------|-------|------------|

| -0.1 V   | 1.2 V    | 4     | 20 $\mu$ m |

**Tabla 2.** Valores adecuados de polarización y tamaño del transistor según las simulaciones.

Estos valores han sido obtenidos inicialmente sin tener en cuenta el diseño completo del amplificador LNA, por lo tanto alguno de estos valores se optimizarán ligeramente para la obtención de unos mejores resultados considerando todo el circuito según vaya avanzando en el diseño. De este modo los valores finales con los que se ha realizado el diseño son los siguientes:

| $V_{gs}$ | $V_{ds}$ | $N_d$ | $W_d$      |

|----------|----------|-------|------------|

| -0.12 V  | 1.2 V    | 4     | 22 $\mu$ m |

**Tabla 3.** Valores finales de polarización y tamaño del transistor.

### 4.3.2 Realimentación fuente

Cuando se diseñan amplificadores de bajo ruido con transistores en configuración fuente común, suele existir una fuerte desadaptación de entrada cuando se le presenta al transistor la impedancia de ruido óptima. Para evitar esto, se incluye una realimentación serie en la fuente del transistor.

Esta realimentación consiste en conectar a la fuente del transistor una línea de transmisión conectada a un paso a masa, incluyendo de este modo un efecto inductivo en la realimentación. El valor de longitud y anchura de esa línea de transmisión se deberá optimizar hasta conseguir que el coeficiente de reflexión de entrada complejo conjugado ( $S_{11}^*$ ) y el coeficiente de reflexión óptimo de ruido ( $S_{opt}$ ) se aproximen, como se ve en la Figura 7. Es importante destacar que esta realimentación inductiva tiene como efecto negativo una disminución en la ganancia máxima que se puede conseguir.

**Figura 7.**  $S_{opt}$  y  $S_{11}^*$  del transistor en la carta de Smith, antes (parte izquierda) y después (parte derecha) de incluir la realimentación fuente.

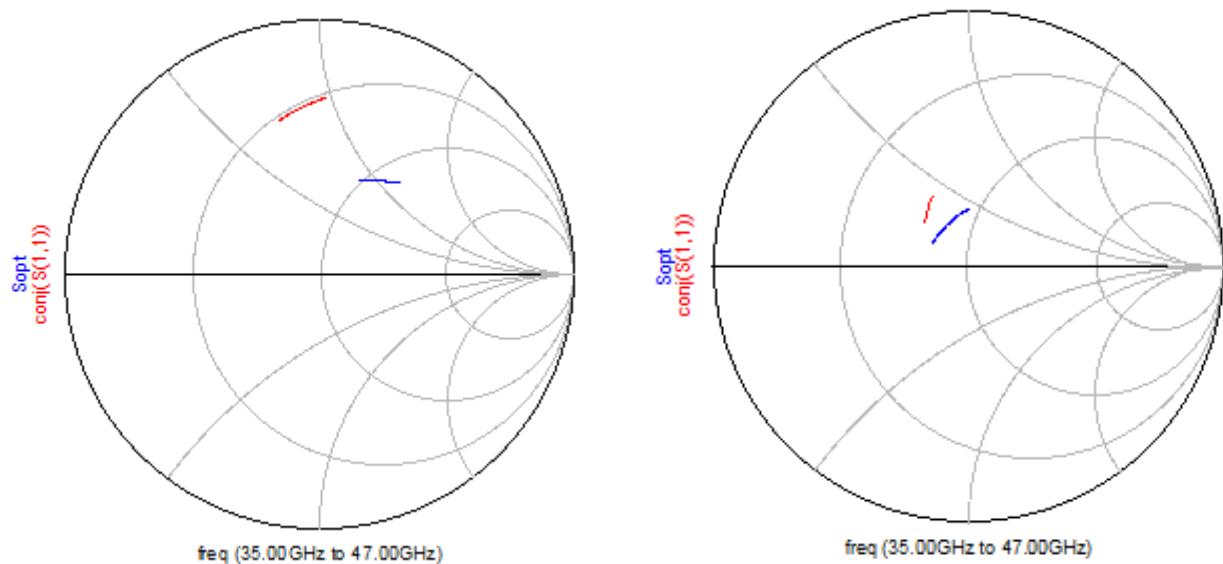

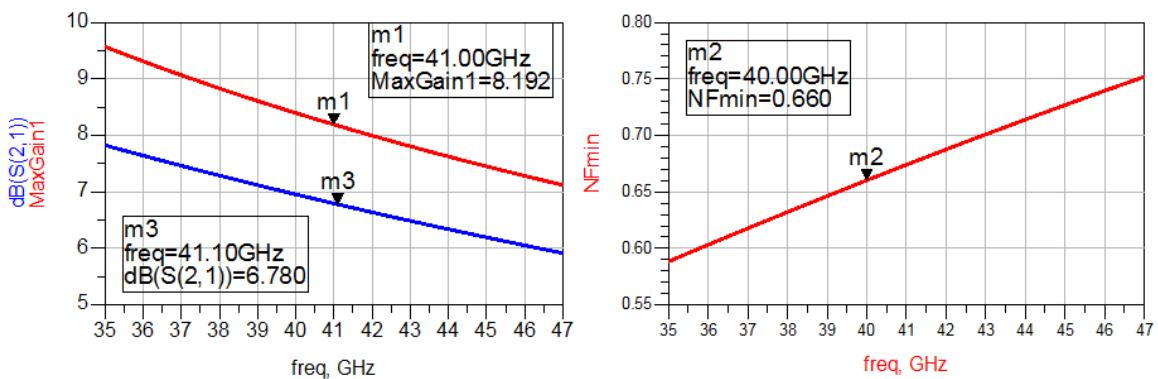

En la Figura 8 se muestra un esquema eléctrico de cómo queda el transistor realimentado, conectado a las líneas de transmisión y a un paso a masa. Estas líneas tienen una anchura de 6  $\mu\text{m}$  y una longitud de 112.5  $\mu\text{m}$ .

Figura 8. Esquema de un transistor con realimentación serie.

Obteniendo los siguientes resultados en términos de ganancia y ruido.

Figura 9. Resultados de simulación del transistor sin realimentación. A la izquierda máxima ganancia (rojo) y ganancia disponible (azul) y a la derecha la figura de ruido mínima.

**Figura 10.** Resultados de simulación del transistor con realimentación en fuente. A la izquierda máxima ganancia (rojo) y ganancia disponible (azul) y a la derecha la figura de ruido.

Observando el comportamiento del transistor en términos de ganancia trabajando en el punto de polarización definido anteriormente, cada transistor puede dar una ganancia máxima de 8.192 dB, por lo tanto si se desea que el amplificador de bajo ruido (LNA) tenga una ganancia mayor de 25 dB, **se necesita diseñarle con al menos 4 etapas**.

Por lo tanto, se podría llegar a tener una ganancia máxima teórica de  $G_{TOTAL} = 4 \times 8.192 = 32.7$  dB, si no tuviésemos en cuenta las pérdidas de las redes de adaptación.

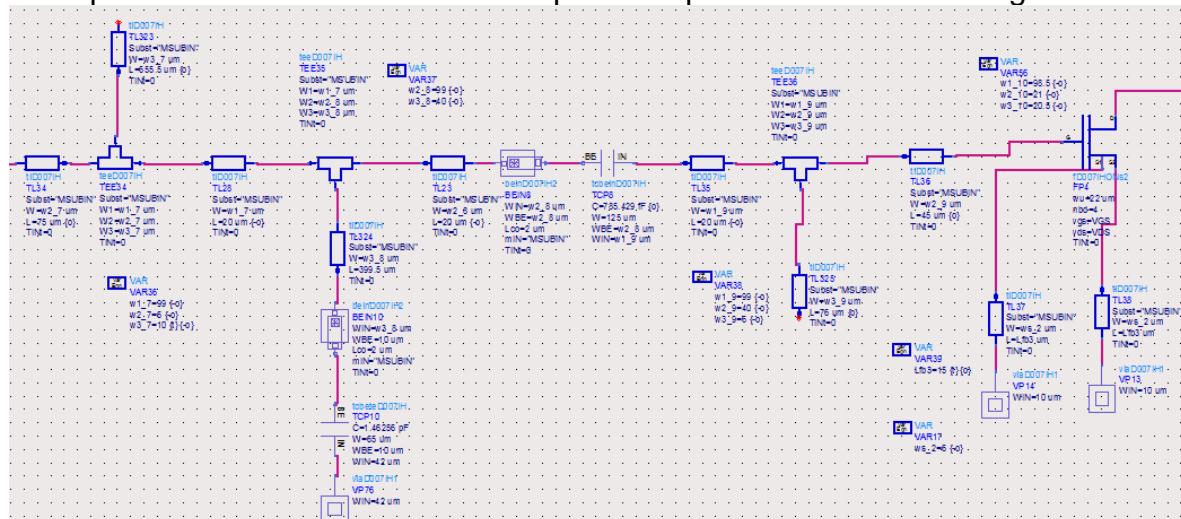

## 4.4 Diseño eléctrico: Esquemático

En esta parte de la memoria se explica paso a paso el diseño de las dos partes más importantes del diseño, que son las redes de adaptación y las redes de polarización. Las cuatro etapas se diseñan etapa por etapa, comenzando por la primera y las redes de adaptación entre etapas estarán compuestas por líneas de transmisión y condensadores implementados con elementos concentrados.

Para el diseño del amplificador se ha tenido en cuenta las siguientes consideraciones a la hora del diseño de cada etapa.

- Las dos primeras etapas se diseñan con el fin de conseguir el mejor comportamiento en cuanto a ruido y ganancia suficiente para minimizar la contribución de ruido de las etapas posteriores.

- Las dos siguientes etapas se diseñan para conseguir la ganancia objetivo y ecualizar la respuesta, compensando así el comportamiento natural de cada transistor con la frecuencia.

### 4.4.1 Red de polarización

En primer lugar se explicará el diseño de las redes de polarización, que permiten polarizar el transistor en continua y en cambio debe ser totalmente transparente para la señal de radiofrecuencia (RF) en la banda de interés, es decir no debe alterar el comportamiento en RF del amplificador. Por otro lado, estas redes suelen ayudar a estabilizar el circuito en frecuencias bajas, donde los transistores presentan ganancias muy altas, evitando así realimentaciones que estabilicen el amplificador.

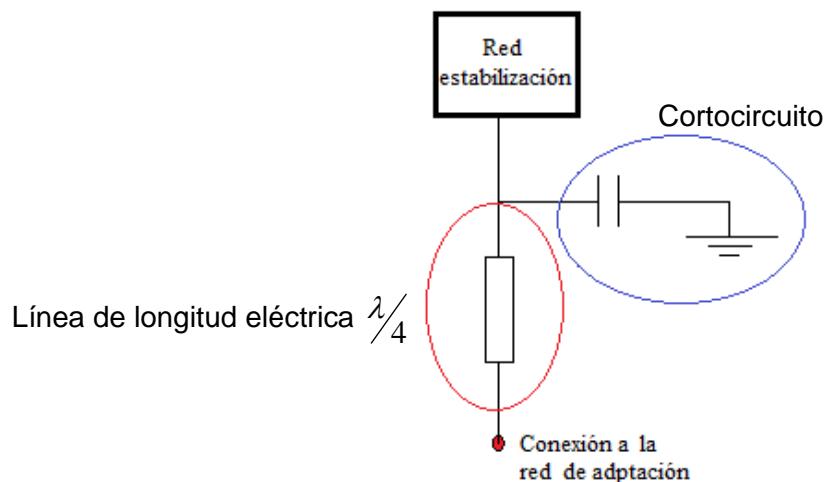

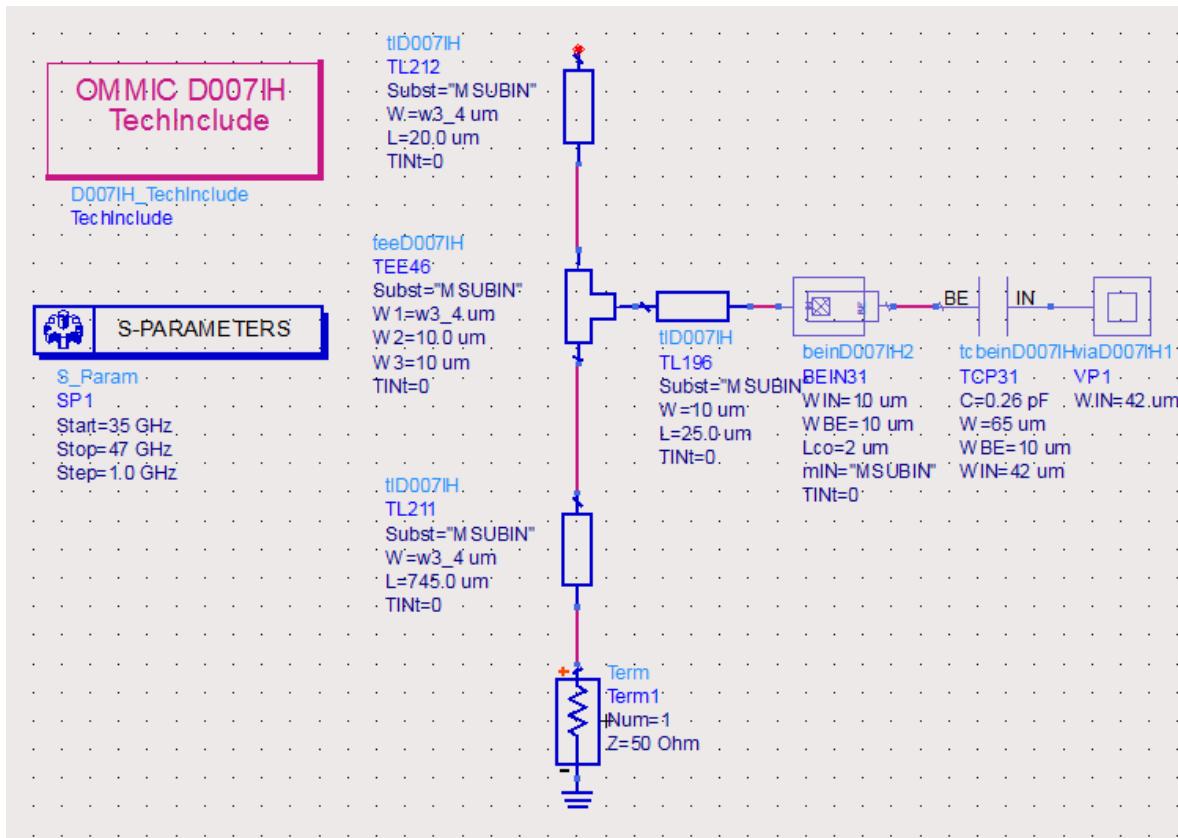

Esta red de polarización está formada por las siguientes partes que se observan en la Figura 11:

Figura 11. Esquema de la red de polarización.

- **Un cortocircuito**, formado por un condensador de valor 0.26 pF, que su función es evitar que la señal de RF se transmita a la red de polarización.

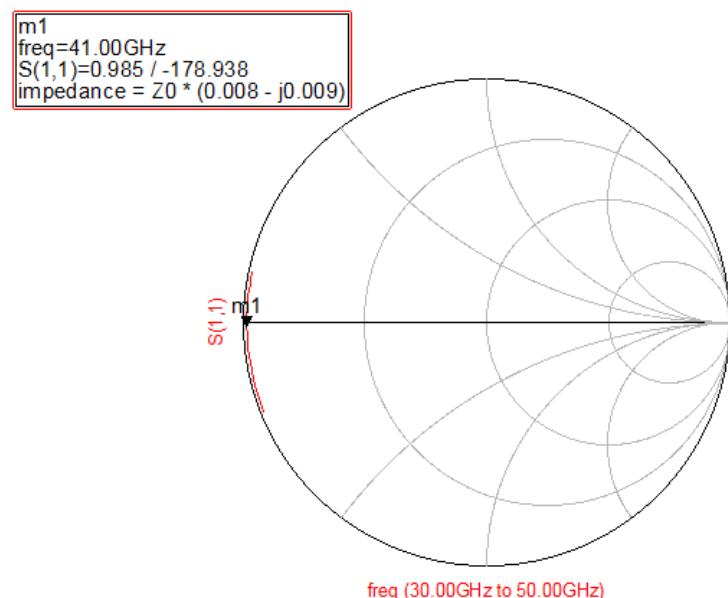

Para el diseño de este condensador, se varía el valor del mismo hasta que la respuesta del coeficiente de reflexión en la carta de Smith presente un cortocircuito. En la figura 12 se observa la respuesta del condensador en la carta de Smith a través del coeficiente de reflexión ( $S_{11}$ ). Esta red presenta cortocircuito, ya que los valores se encuentran en el extremo izquierdo de la carta y centrado en 41 GHz.

**Figura 12.** Comportamiento del condensador de valor  $C=0.26$  pF en el rango de frecuencias de interés (35 a 47 GHz).

- **Una línea de longitud eléctrica  $\lambda/4$**  para conseguir un circuito abierto para la señal de RF, cuya longitud es de 745  $\mu$ m y anchura 10  $\mu$ m.

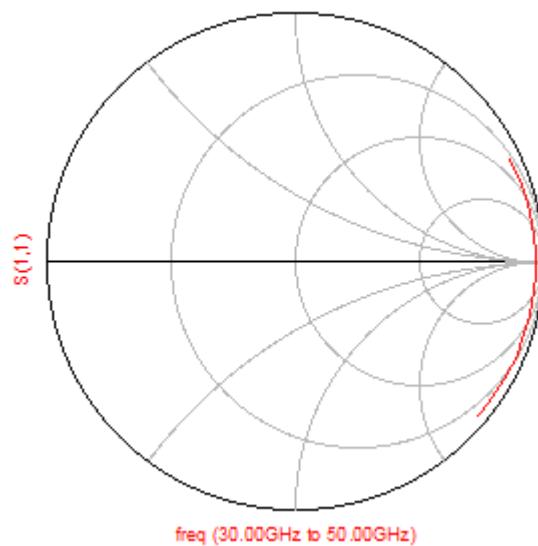

A continuación, Figura 13, se muestra la red de polarización del amplificador LNA, en donde se comprueba que funciona como un circuito abierto a la señal de RF. En la Figura 14 se observa la respuesta de la red de polarización en la carta de Smith a través del coeficiente de reflexión ( $S_{11}$ ). Esta red presenta un circuito abierto, ya que los valores se encuentran en el extremo derecho de la carta.

Figura 13. Esquema eléctrico de la red de polarización del transistor

Figura 14. Respuesta de la red de polarización en el rango de frecuencias de interés formada a través de un condensador  $C=0.26$  pF y una línea  $\lambda/4$  de 10  $\mu$ m de anchura.

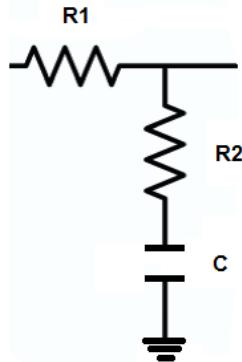

Para finalizar la red de polarización se ha añadido una red adicional que ayudará a estabilizar el circuito:

- **Una red de estabilidad**, Figura 15, compuesta por una resistencia  $R_2=600 \Omega$ , un condensador de  $C=2 \text{ pF}$  y un paso a masa. Esta red funciona como un filtro con una frecuencia de corte del orden de los MHz y lo que se quiere evitar es que a bajas frecuencias puedan producirse realimentaciones que inestabilizan el amplificador.

Para la elección de los valores del filtro de paso bajo se ha tenido en cuenta la expresión 2, de modo que se escoge un valor de  $R$  y  $C$  razonable para tener una frecuencia de corte de orden de los MHz.

$$f_C = \frac{1}{2\pi RC} \quad (2)$$

**Figura 15.** Red de estabilidad.

También se ha añadido una resistencia  $R_1$ , sin embargo dependiendo de la red de polarización en la que se inserte el valor de esta resistencia variará, ya que, si es el caso de la red de polarización de puerta, pueden utilizarse resistencias de valor alto puesto que la intensidad que circula es muy baja y por lo tanto el consumo de potencia no es significativo, sin embargo para el caso de redes las redes de polarización de drenador se debe utilizar resistencias de valor bajo ya que la intensidad que circula ahora ya no es baja.

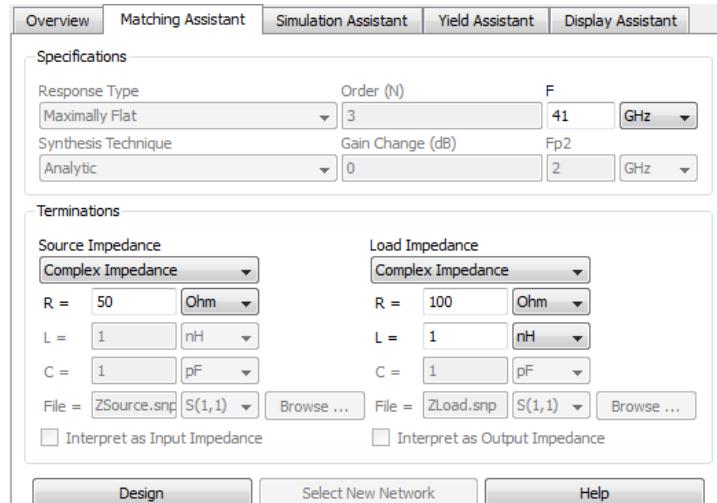

Una vez explicada la red de polarización se pasa al diseño de cada etapa amplificadora, para ello se diseñan las redes de adaptación de cada etapa utilizando la herramienta de ‘Impedance Matching’ que incluye ADS. La interfaz gráfica que nos presenta se muestra en la Figura 16.

**Figura 16.** Herramienta ‘Impedance Matching’ de ADS para la implementación de redes de adaptación.

Esta herramienta diseña automáticamente redes de adaptación, proporcionándole la frecuencia de trabajo, la impedancia que se ve desde la fuente y la impedancia que se observa desde la carga. A continuación ofrece una serie de redes posibles y según convenga en el diseño se elegirá la más conveniente.

Estas redes de adaptación que están formadas por elementos inductivos (bobinas) y capacitivos (condensadores), ADS nos las diseñará con unos valores iniciales ideales. A continuación se deberá implementar estos elementos con los elementos de la librería del proceso D007IH, y posteriormente se optimizarán para conseguir las especificaciones de diseño. Las inductancias concentradas que se obtienen en “Impedance Matching” se sustituyen por líneas de transmisión.

## 4.4.2 Primera etapa amplificadora: red de entrada

Esta red está formada por la red de adaptación de la entrada y la red de polarización de puerta del primer transistor.

La primera etapa del amplificador es la más crítica en términos de figura de ruido, y es por eso por lo cual debe diseñarse intentando minimizar el ruido todo lo posible.

Esta red de entrada está formada, Figura 17, por líneas de transmisión y un condensador que cumple la función de desacoplo, es decir aísla la señal de RF de la señal de DC de la red de polarización del transistor.

Los objetivos marcados a la hora de diseñar esta etapa son tener el mínimo de ruido posible, una adaptación de entrada mejor de -10 dB y la máxima ganancia que se pueda sin estropear demasiado la adaptación de entrada. De este modo a la hora del diseño y la optimización de esta etapa se prioriza la figura del ruido.

Figura 17. Esquema eléctrico de la primera etapa amplificadora: red de entrada.

En el terminal libre de la línea de transmisión TL236, marcado en rojo, es donde se sitúa la red de polarización de puerta del transistor, que para una mejor visualización de la red de adaptación de entrada se ha suprimido.

Los resultados obtenidos de la simulación en parámetros de Scattering y ruido del esquemático de la Figura 175 son los mostrados en las Figura 18 y Figura 19.

**Figura 18.** Adaptación de entrada y salida de la primera etapa amplificadora.

**Figura 19.** Figura mínima de ruido (rojo) y ganancia (azul) de la primera etapa amplificadora.

En la figura 18 se muestra la adaptación tanto de entrada como de salida de la primera etapa amplificadora. Como se observa una buena adaptación de entrada por debajo de los -10 dB, y la adaptación de salida por el momento no importa su comportamiento, si tenemos en cuenta que lo que se está diseñando en estos momentos es la red de entrada.

En el diseño de esta etapa, como se ha explicado con anterioridad, se ha intentado minimizar al máximo la figura de ruido mínimo (Figura 19 en rojo), con un valor medio en la banda de trabajo de  $NF=0.994$  dB. En esta misma figura se representa la ganancia en transferencia  $S_{21}$  (en azul) que tiene un valor medio de  $|S_{21}|=9.8$  dB, con un rizado de 2.226 dB entre el valor máximo 11.1 dB y el mínimo 8.9 dB.

A modo información, también se analiza la estabilidad del circuito a través del factor  $\mu$ .

**Figura 20.** Estabilidad de la primera etapa amplificadora a través del factor  $\mu$ .

Como se puede apreciar en la Figura 20 hay valores del factor  $\mu$  menores de 1, por lo tanto esta etapa es inestable. En las optimizaciones sucesivas se priorizará que este parámetro sea mayor que 1.

Cabe recordar que el factor de estabilidad  $\mu$  representa la mínima distancia desde la zona inestable al centro de la carta de Smith, de este modo se debe conseguir un factor  $\mu > 1$  para que el amplificador sea estable en todo el rango de frecuencias y para cualquier impedancia pasiva. Este parámetro  $\mu$  viene definido por la siguiente expresión:

$$\mu = \frac{1 - |S_{11}|^2}{|S_{22} - \Delta \cdot S_{11}^*| + |S_{12} \cdot S_{21}|} \quad (3)$$

Donde  $\Delta$  es:

$$\Delta = S_{11} \cdot S_{22} - S_{12} \cdot S_{21} \quad (4)$$

Y por lo tanto para que el amplificador sea incondicionalmente estable se debe cumplir que:

$$\mu = \frac{1 - |S_{11}|^2}{|S_{22} - \Delta \cdot S_{11}^*| + |S_{12} \cdot S_{21}|} > 1 \quad (5)$$

#### 4.4.3 Segunda etapa amplificadora

La segunda etapa corresponde a la red de adaptación que conecta al 1<sup>er</sup> y 2<sup>o</sup> transistor, la red de polarización de drenador del primer transistor así como la red de polarización de puerta del segundo transistor.

En esta etapa, al igual que sucede con la primera etapa, contribuye en gran medida al aumento del ruido total del LNA puesto que la ganancia que se tiene no es aún muy grande (fórmula de Friis).

De modo que a la hora de optimizar se tiene en cuenta significativamente el ruido, además de seguir mejorando la adaptación de entrada y aumentar la ganancia. El circuito eléctrico de esta etapa se muestra en la Figura 21.

W\_31-21.5 (9)

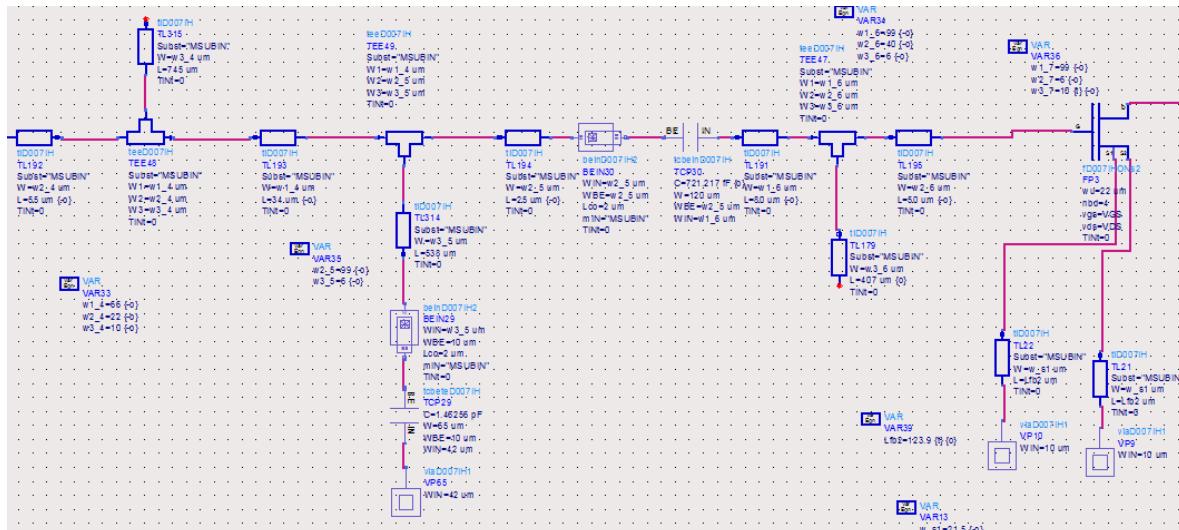

A partir de la primera etapa amplificadora y, en sucesivas etapas, se realiza una modificación de la red de adaptación y es que se añade un condensador, en este caso el nombrado según TCP29, que cumple las funciones de bloqueo de la tensión DC provenientes de la red de polarización de drenador.

El esquema de la red donde va este condensador se muestra en la Figura 22. Sin este condensador esa rama de la red de adaptación es un cortocircuito para la tensión de DC y entonces la tensión en el drenador del transistor sería  $V_{ds}=0$  V.

**Figura 22.** Condensador de bloqueo de la DC añadido en las redes de adaptación.

A continuación se muestran los resultados de la simulación del amplificador LNA, hasta la 2º etapa. En la Figura 23, se observa como se ha mejorado la adaptación de entrada, siendo mejor que -15 dB.

**Figura 23.** Adaptación de entrada y salida del amplificador con dos etapas.

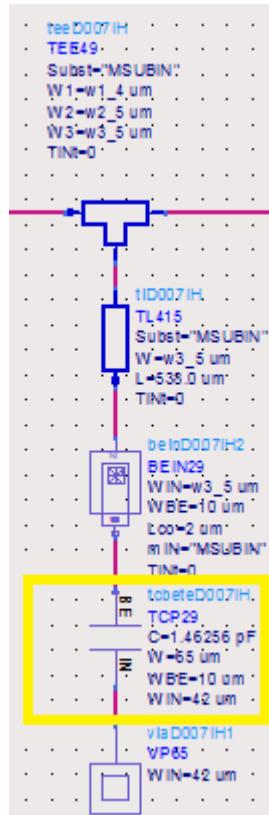

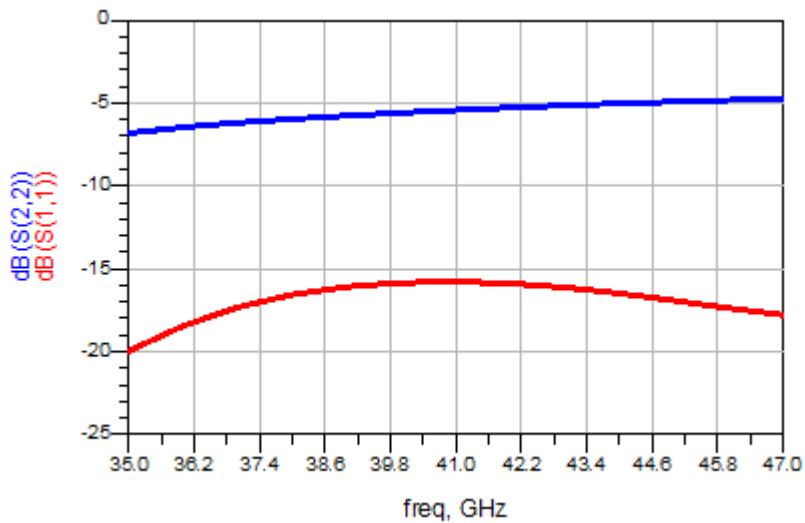

La ganancia (azul) que está representada en la Figura 24 tiene un valor medio de  $|S_{21}|=16.3$  dB obteniendo un rizado de 4.5 dB bastante alto, con un valor máximo de 18.818 dB y un valor mínimo de 14.3 dB.

En cuanto a la figura de ruido (rojo en la Figura 24) de las dos primeras etapas ha aumentado como era normal hasta un valor medio de  $NF=1.137$  dB.

**Figura 24.** Figura de ruido del amplificador con 2 etapas (rojo) y ganancia en transferencia (azul) del amplificador con las dos primeras etapas.

Por último en la Figura 25 se puede observar la estabilidad del amplificador. El amplificador en este momento es incondicionalmente estable ya que el factor de estabilidad  $\mu$  es siempre mayor que 1.

**Figura 25.** Estabilidad del amplificador LNA con las dos primeras etapas.

#### 4.4.4 Tercera etapa amplificadora

La tercera etapa corresponde a la red de adaptación que conecta al 2º y 3º transistor, la red de polarización de drenador del segundo transistor así como la red de polarización de puerta del tercer transistor.

Esta etapa ya no tiene como objetivo minimizar la figura de ruido puesto que el ruido añadido por esta etapa viene dividido por la ganancia de las etapas anteriores y por lo tanto se intentará seguir aumentando la ganancia.

De modo que en esta etapa se diseña para mantener bastante bien la adaptación de entrada menor de -10 dB, mejorar el rizado en banda y aumentar la ganancia. Otro objetivo en esta etapa es mejorar la estabilidad del amplificador de manera que el amplificador se mantenga incondicionalmente estable, para ello se intentará que el factor  $\mu > 1$ . El esquema eléctrico de la red interetapa es el que se muestra en la Figura 26.

**Figura 26.** Circuito eléctrico de la red interetapa entre el 2º y 3º transistor.

En la Figura 27 se muestra la adaptación de entrada que ha empeorado un poco a ciertas frecuencias aunque sigue bastante bien por debajo casi siempre de los -15 dB, con un valor medio de 18.9 dB. En cuanto a la adaptación de salida se ha mejorado bastante, aunque será en la última etapa en donde se mejorará sustancialmente.

**Figura 27.** Adaptación de entrada y salida del amplificador con las tres primeras etapas.

En la figura 28, se observa como la figura de ruido respecto a la que se tenía antes (Figura 24) es muy similar apenas ha aumentado 0.02 dB. Representado en azul se tiene la ganancia en transferencia que se ha aumentado bastante hasta un valor medio de 24.264 dB, el rizado es de 6.393 bastante superior a lo obtenido anteriormente y se intentará disminuir en la última etapa amplificadora.

**Figura 28.** Figura de ruido (rojo) y ganancia en transferencia (azul) del amplificador con las tres primeras etapas.

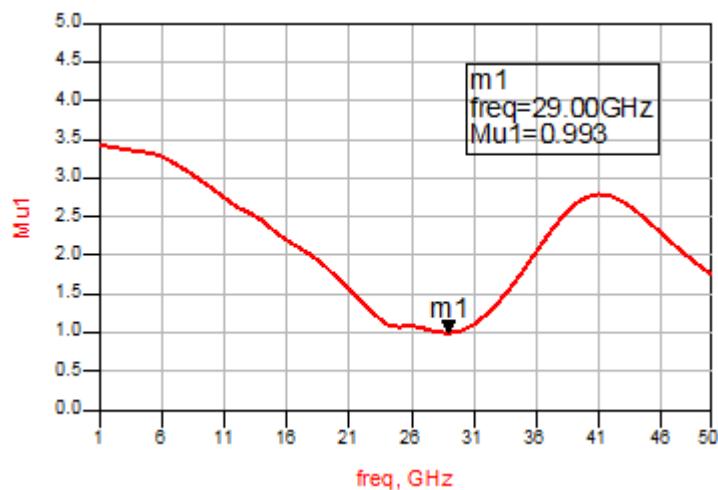

La estabilidad del amplificador ha mejorado considerablemente (Figura 29), sin embargo a la frecuencia de 29 GHz el factor de estabilidad  $\mu$  es menor que 1, de modo que el amplificador vuelve a ser inestable. Este parámetro pasará a ser un objetivo importante en la optimización de la cuarta etapa amplificadora.

**Figura 29.** Estabilidad del amplificador LNA con las tres primeras etapas.

#### 4.4.5 Cuarta etapa amplificadora

La cuarta etapa corresponde a la red de adaptación que conecta al 3<sup>er</sup> y 4<sup>o</sup> transistor, la red de polarización de drenador del tercer y cuarto transistor así como la red de polarización de puerta del cuarto transistor.

En esta etapa se intenta buscar una respuesta de la ganancia en transferencia lo más alta y plana posible, tener una adaptación tanto de entrada como de salida menor de -10 dB en el rango de trabajo (35 – 47 GHz) y un factor de estabilidad mayor que 1, requisito indispensable para el correcto funcionamiento del amplificador sin riesgo de oscilación.

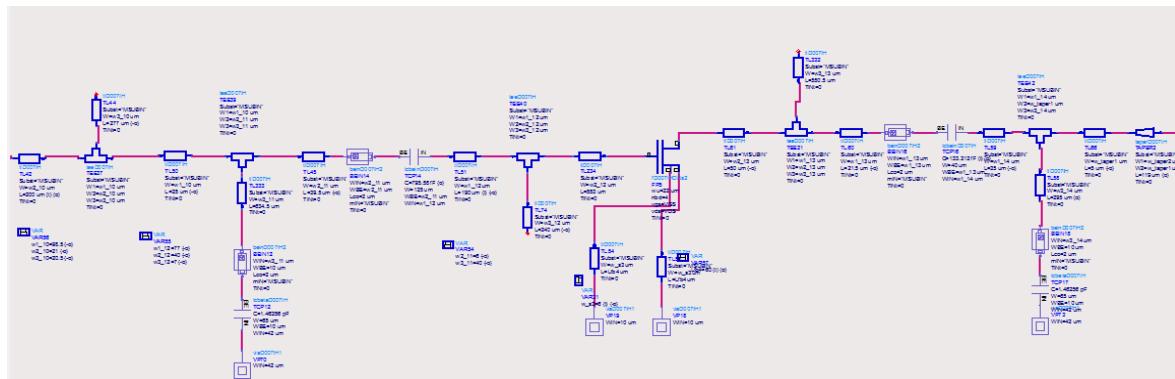

Con esta última etapa se da por finalizado el diseño del amplificador y los objetivos marcados en las especificaciones de diseño iniciales se deben cumplir en su totalidad, como son la figura de ruido (NF) por debajo de 1.8 dB, adaptaciones de entrada y salida menores de -10 dB ( $|S_{11}|$  y  $|S_{22}|$  respectivamente), ganancia en transferencia ( $|S_{21}|$ ) mayor de 25 dB con una respuesta lo más plana posible y un amplificador incondicionalmente estable, es decir, con un factor de estabilidad  $\mu$  mayor que 1. En la Figura 30 se muestra el circuito eléctrico de la última etapa del amplificador.

Figura 30. Circuito eléctrico de la última etapa del amplificador.

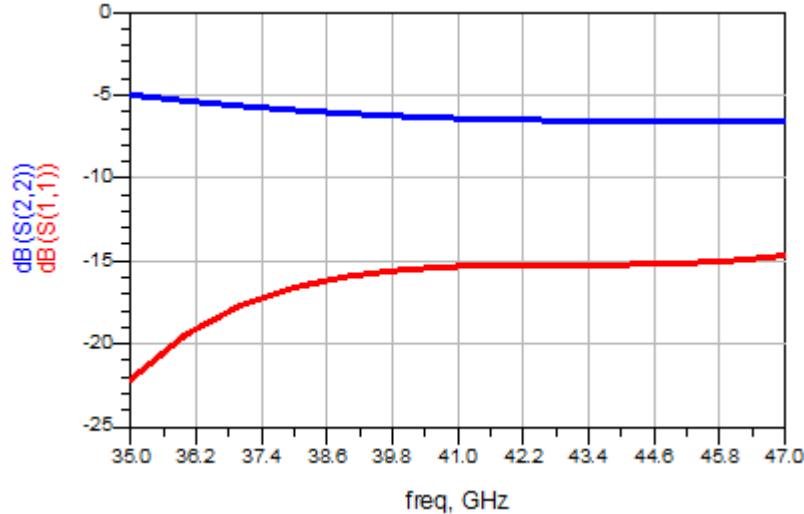

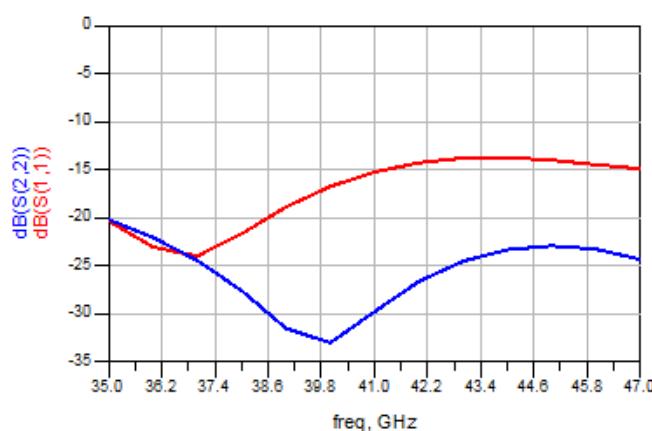

En la Figura 31 se muestra la adaptación de entrada y salida ( $S_{11}$  y  $S_{22}$  respectivamente), como se observa la adaptación de entrada tiene un valor medio de -15.223 dB, por debajo de -10 dB en toda la banda de trabajo, en cuanto a la adaptación de salida con un valor medio de -29.759 dB está siempre por debajo de los -20 dB obteniendo así una magnifica adaptación de salida.

Figura 31. Adaptación de entrada y salida del amplificador con las cuatro etapas

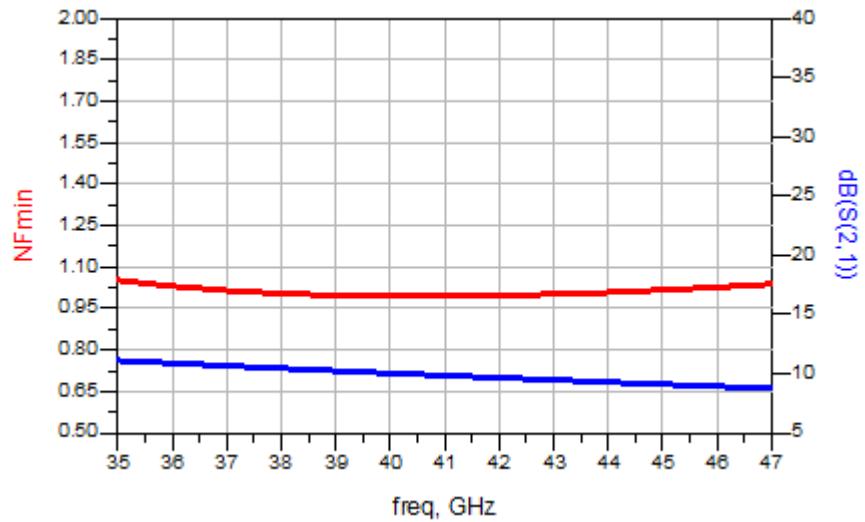

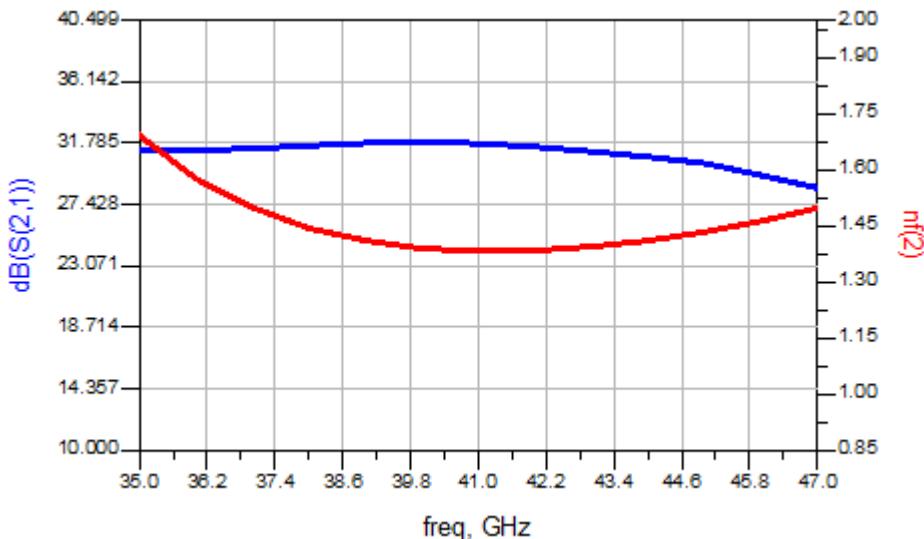

En la Figura 32 se representa la ganancia de transferencia ( $S_{21}$  en azul). Su valor medio dentro de la banda de trabajo es de  $|S_{21}|=28.62$  dB, con un valor máximo de 30.5 dB y un mínimo de 28.4 dB, como se aprecia la respuesta de la ganancia es plana exceptuando de 35 a 36 GHz que se sube ligeramente, sin embargo en el resto de la banda se tiene un valor medio de 28.6 dB.

El resultado de la figura de ruido se encuentra en la Figura 32 en rojo donde se comprueba que casi en la totalidad de la banda se encuentra por debajo de  $NF=1.26$  dB.

**Figura 32.** Figura de ruido (rojo) y ganancia en transferencia (azul) del amplificador con las cuatro etapas.

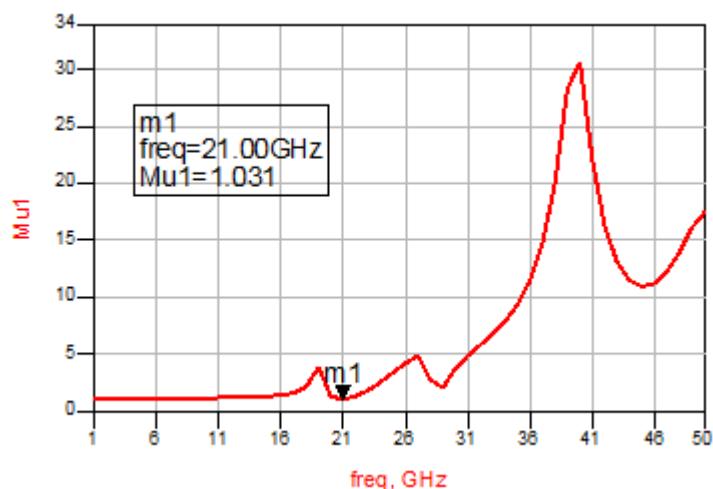

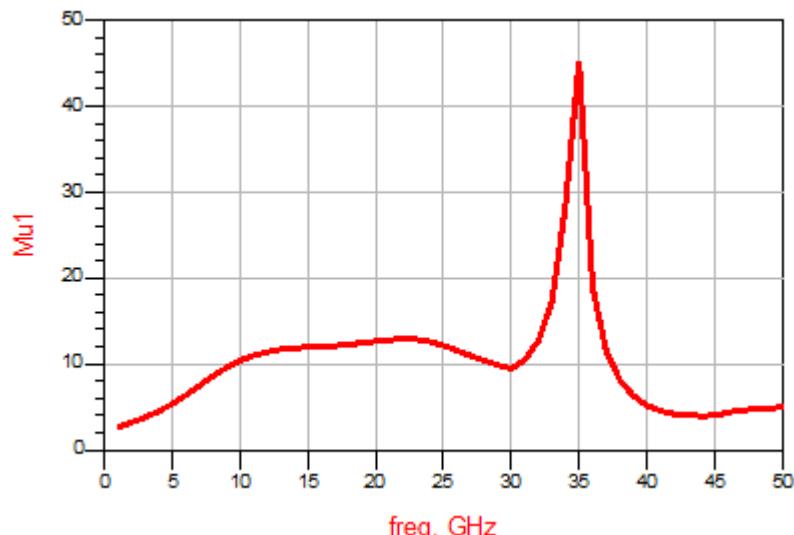

Por último de la Figura 33 se puede extraer que la estabilidad del amplificador está asegurada ya que tenemos un factor de estabilidad  $\mu$  siempre mayor que 1, siendo el valor mínimo de este parámetro en nuestro diseño de 1.031. Por lo tanto se puede concluir que el **amplificador de bajo ruido es incondicionalmente estable**.

**Figura 33.** Estabilidad del amplificador con cuatro etapas.

Antes de hacer las valoraciones de este diseño, es importante reseñar que después de este diseño aquellas líneas con grandes dimensiones han sido transformadas por meandros cuya longitud eléctrica total debe ser igual que la longitud eléctrica de la línea a la que sustituye.

Esto se hace así para que el layout o máscara del amplificador de bajo ruido que se entrega a la fundición para su fabricación, sea lo más compacto posible y de esta manera reducir el tamaño del mismo. Por consiguiente, esto supone una reducción del coste puesto que su precio es función de la superficie del layout. A continuación, Figura 34, se muestra un ejemplo en el que se ha sustituido una línea de transmisión recta por un meandro para minimizar el espacio del circuito.

**Figura 34.** Ejemplo de un meandro en sustitución a una línea de transmisión recta.

#### 4.4.6 Valoraciones del diseño

El resultado obtenido de la simulación en esquemático del amplificador de bajo ruido (LNA) presenta unos buenos resultados, cumpliendo todas las especificaciones iniciales de diseño.

Por una parte las adaptaciones conseguidas tanto de entrada como de salida ( $|S_{11}|$  y  $|S_{22}|$  respectivamente) se encuentran por debajo de los -10 dB, la ganancia está por encima de los 25 dB con una respuesta bastante plana exceptuando a la frecuencia inicial que hay un ligero mayor rizado respecto a otras frecuencias, además el ruido está muy por debajo de los 2.8 dB que se exigían en las especificaciones iniciales. A parte de esto se puede asegurar la estabilidad del amplificador evitando así posibles oscilaciones que podría ocurrir.

A continuación se muestra en la Tabla 4 la comparativa entre valores previstos iniciales (Especificaciones de diseño) y valores finales obtenidos Comportamiento LNA diseñado (Esquemático).

|                                        | Especificaciones de diseño | Comportamiento LNA diseñado (Esquemático) |

|----------------------------------------|----------------------------|-------------------------------------------|

| Adaptación entrada ( $S_{11}$ )        | $ S_{11}  > -10$ dB        | $ S_{11}  = -15.223$ dB                   |

| Adaptación salida ( $S_{22}$ )         | $ S_{22}  > -10$ dB        | $ S_{22}  = -29.759$ dB                   |

| Ganancia en transferencia ( $S_{21}$ ) | $ S_{21}  > 25$ dB         | $ S_{21}  = 28.620$ dB                    |

| Figura de ruido (nf2)                  | $NF < 1.8$ dB              | $NF = 1.264$ dB                           |

| Factor de estabilidad ( $\mu$ )        | $\mu > 1$                  | $\mu = 1.031$                             |

**Tabla 4.** Comparativa de las especificaciones de diseño y resultados obtenidos (valores medios, excepto  $\mu$  que es valor mínimo en toda la banda).

## 4.5 Diseño electromagnético: Momentum

Una vez se ha finalizado el diseño del amplificador de bajo ruido en esquemático con modelos eléctricos para los elementos de las redes pasivas, cumpliéndose las especificaciones definidas en un principio, es necesario realizar una simulación electromagnética con el objetivo de que el diseño sea más fiable y real.

Estas simulaciones electromagnéticas se realizan a través de la herramienta Momentum, que viene implícita en el propio simulador ADS. Esta simulación tiene en cuenta los efectos tanto parásitos como capacitivos producidos por líneas de transmisión y condensadores que en alta frecuencia pueden ser algo diferentes a los simulados en esquemático. Generalmente las simulaciones con Momentum predicen más pérdidas que en esquemático y por lo tanto el ruido simulado será superior.

Estas simulaciones electromagnéticas se van a realizar sobre los elementos pasivos del amplificador, excluyendo resistencias y pasos a masa. Para estos elementos y a la frecuencia de diseño de este amplificador, se considera que los modelos eléctricos son razonablemente buenos.

El objetivo que se marca en este punto es simular las 5 redes en las que se divide el LNA: red entrada, las 3 redes que conectan los transistores y la red de salida. La simulación electromagnética de cada red genera un fichero con los parámetros de Scattering en el rango de frecuencias simulado.

A continuación estos ficheros se cargarán en un '*Data Item*', y se sustituirán por la red en esquemático.

### 4.5.1 Consideraciones previas

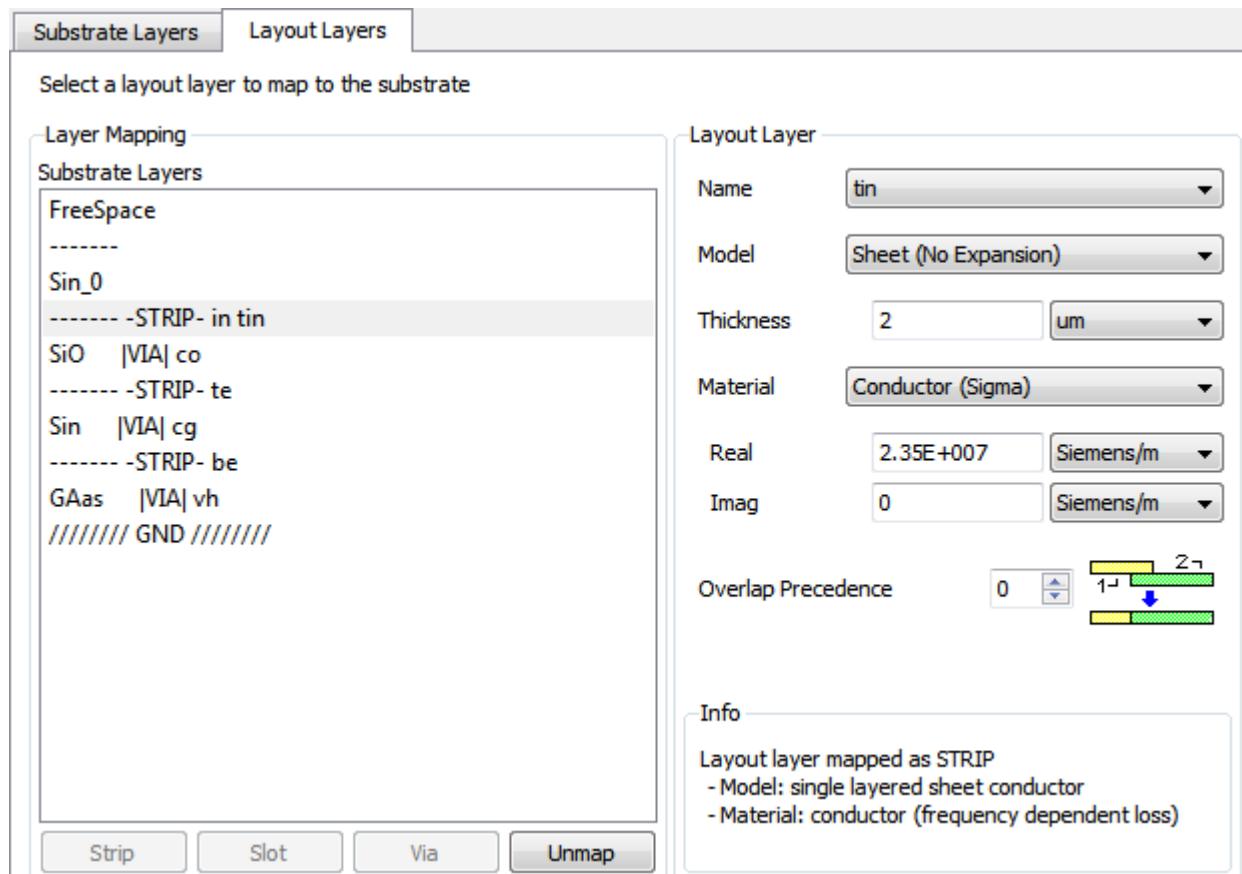

Para conseguir las especificaciones fijadas en un principio, se irán sustituyendo las redes pasivas por su correspondiente '*Data Item*', y aquellas redes que aún no estén simuladas electromagnéticamente se irán optimizando y simulando las electromagnéticamente hasta que se hayan finalizado las 5 redes del amplificador de bajo ruido. Para la realización de estas simulaciones es muy importante haber definido anteriormente el sustrato (Figura 35) para que la simulación sea lo más precisa posible (Capítulo 3.2).

Figura 35. Capas del sustrato definido para simulaciones electromagnéticas.

Antes de empezar a realizar las simulaciones electromagnéticas, es conveniente analizar el comportamiento de un elemento pasivo para comprobar que el substrato está bien caracterizado, y en este caso se ha escogido un condensador. Se han seguido las consideraciones definidas en la librería de OMMIC.

El sustrato electromagnético definido por la librería OMMIC tiene un pequeño problema cuando se desea realizar una simulación electromagnética de interconexiones y condensadores en un mismo circuito. Y es que utiliza la misma capa CO para simular tanto las interconexiones como los condensadores de modo que se debe añadir una nueva capa CG al sustrato para poder simular correctamente este elemento de librería.

Por lo tanto para conectar la capa TE con la capa BE es necesario aplicar un rectángulo de la capa CG sobre el terminal que entra al condensador por la capa CO (Figura 37). Añadiendo esta capa CG lo que se consigue es poder simular interconexiones y condensadores con el mismo sustrato de forma correcta. De modo que la capa CO permita la conexión entre las capas IN y TE y la capa CG entre las capas TE y BE.

**Figura 36.** Capa CO de condensador sin añadir la capa CG.

**Figura 37.** Capa CO de condensador añadiendo capa CG.

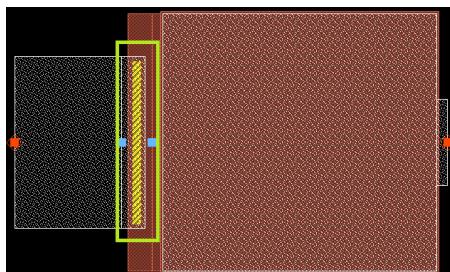

En la figura 36 se puede apreciar la zona señalada con un cuadrado verde, que es la capa CO de los condensadores donde se añade el rectángulo de la capa CG. En cambio en la figura siguiente (Figura 37) también señalizado con un cuadrado azul se aprecia la capa CO una vez superpuesta la capa CG.

Una vez estudiado los condensadores se procede a realizar el diseño electromagnético y a continuación se detalla paso a paso el proceso seguido como se ha hecho con la simulación en esquemático.

Otra cosa importante de los condensadores con esta librería de OMMIC es que existen 2 tipos:

- BETE para valores de capacidades entre los (0.06 pF < C < 50 pF).

- BEIN para valores de capacidades entre los (1 fF < C < 1 pF).

#### 4.5.2 Red entrada

Al igual que sucede con la simulación en esquemático, en primer lugar se simula la red de entrada en Momentum, tal como quedó optimizada en el proceso de diseño en esquemático. A continuación se genera un layout automático de la red y se realiza la simulación electromagnética.

El layout resultado de la red de entrada es el de la Figura 38. Otra cosa importante antes de realizar la simulación es añadir los puertos en el layout, donde cada puerto debe estar en la capa correspondiente (IN o BE).

**Figura 38.**Layout de la red de entrada

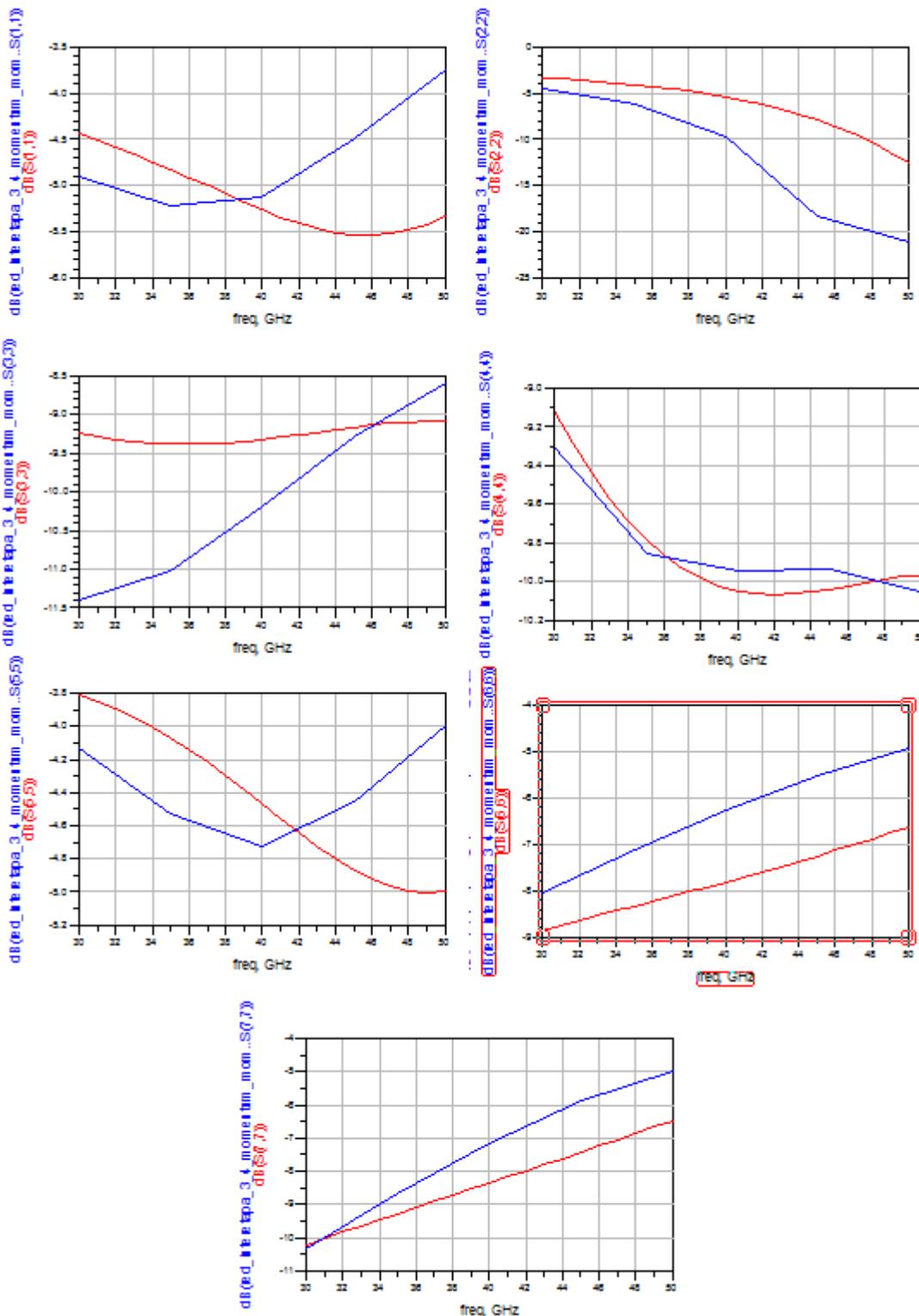

A continuación se realiza la simulación electromagnética y se comparan los resultados entre esta simulación y la de esquemático con el fin de comprobar que ambas simulaciones tienen un comportamiento lo más similar posible y en caso contrario poder realizar alguna pequeña modificación para que así sea. Estas respuestas se comparan en la Figura 36.

**Figura 39.** Comparativa simulación electromagnética (azul) y simulación en esquemático (rojo) de la red de entrada

En la Figura 39 se comparan los resultados de la simulación electromagnética (azul) y esquemático (rojo). Y como se observa los resultados se ajustan bastante bien.

Estas variaciones se deben principalmente a que en la simulación electromagnética se tienen en cuenta determinados efectos que pueden no estar bien modelados en los modelos eléctricos y que son más significativos según aumenta la frecuencia. Se considera que estas simulaciones son más reales pero a la vez predicen más perdidas.

Una vez simulado y comprobado que la red se ajusta a lo que se tenía en un principio simulado, se introduce la simulación de parámetros de Scattering de la red de entrada simulada con Momentum dentro del esquemático de LNA que se tenía previamente. Para comprobar su comportamiento en parámetro de ruido, estabilidad, adaptación y ganancia.

En la Figura 40 se observa la adaptación de entrada (rojo) y la adaptación de salida (azul) en la banda de trabajo de 35 a 47 GHz, el valor medio de la adaptación de entrada es  $|S_{11}|=-16.43$ , sin embargo se tienen a frecuencias bajas adaptaciones por debajo de los  $|S_{11}|=-10$  dB que se intentarán mejorar con las siguientes etapas. El valor medio de la adaptación de salida es  $|S_{22}|=-22.42$ , teniendo además en todo el rango una adaptación muy buena por debajo de -15 dB.

**Figura 40.** Adaptación de entrada (rojo) y adaptación de salida (azul) incluyendo la simulación electromagnética de la red de entrada.

En la Figura 41, viene reflejada tanto la ganancia en transferencia  $S_{21}$  (Azul) como la figura mínima de ruido (Rojo). En la derecha se observa la ganancia con un valor medio de  $|S_{21}|=27.21$  dB con un rizado máximo de 1.01 dB en la banda de trabajo desde el mínimo 27.57 dB hasta el máximo 28.58 dB. A la izquierda se observa la figura de ruido mínima que ha aumentado como es normal hasta un valor medio de  $NF=1.39$  dB.

**Figura 41.** Figura de ruido (rojo) y ganancia en transferencia (azul) incluyendo la simulación electromagnética de la red de entrada.

Por acabar con esta red de entrada en la Figura 42 viene analizada la estabilidad del LNA mediante el factor  $\mu$  y como se observa el amplificador es incondicionalmente estable con un valor mínimo de 2.04.

Figura 42. Factor de estabilidad  $\mu$  de la red de entrada.

#### 4.5.3 Red entre el primer y segundo transistor

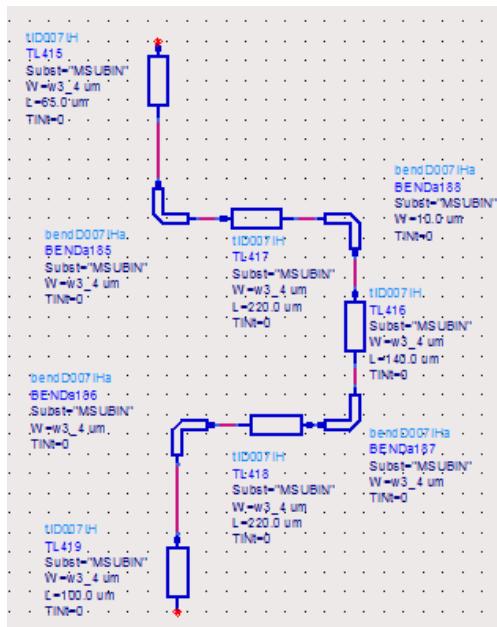

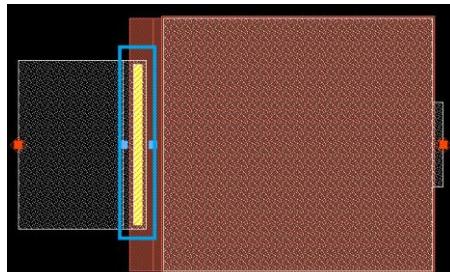

La siguiente red a analizar en el simulador electromagnético es la que conecta al primer transistor con el segundo. Como sucedió con la red de entrada se genera el layout automáticamente, obteniendo la máscara de la Figura 40.

Figura 43. Layout de la red que conecta al transistor nº1 con el nº 2.

Al igual que antes se comparan los resultados obtenidos en la simulación electromagnética (azul) y en la simulación en esquemático (Rojo). En este caso los resultados (Figura 44) siguen asemejándose aunque en menor medida que antes por lo que se realiza alguna optimización mínima para que no se empeoren los resultados.

**Figura 44.** Comparativa simulación electromagnética (azul) y simulación en esquemático (rojo) de la red que conecta al transistor nº1 con el nº 2

A continuación se añade la simulación electromagnética al esquemático del LNA y se visualizan los resultados, con la red entrada y la red que conecta los transistores primero y segundo en simulación electromagnética y lo demás con simulación en esquemático.

En primer lugar en la Figura 42 se observa en la parte derecha la ganancia en transferencia  $S_{21}$  del LNA obteniendo de valor medio 28.26 dB, con un rizado de 0.92 dB. A la izquierda en rojo la figura mínima de ruido con un valor medio de  $NF=1.38$  dB.

**Figura 45.** Figura de ruido (rosa) y ganancia en transferencia (azul) incluyendo la simulación electromagnética de la red que conecta transistor 1 y 2.

En la Figura 46 se observa la adaptación de entrada (rojo) y la adaptación de salida (azul) en la banda de trabajo de (35 – 47 GHz), el valor medio de la adaptación de entrada es -25.13, sin embargo se tienen a frecuencias bajas adaptaciones por debajo de los -10 dB que se intentarán mejorar con las siguientes etapas -22.35 dB. El valor medio de la adaptación de salida es -22.42, en este caso se sigue manteniendo en todo el rango una adaptación muy buena por debajo de -15 dB.

**Figura 46.** Adaptación de entrada (rojo) y adaptación de salida (azul) incluyendo la simulación electromagnética de red que conecta transistor 1 y 2.

En la figura 47 se analiza la estabilidad del LNA mediante el factor  $\mu$  y como se observa el amplificador sigue siendo incondicionalmente estable con un valor mínimo de 2.043.

**Figura 47.** Factor de estabilidad  $\mu$  incluyendo la red que conecta transistor 1 y 2.

#### 4.5.4 Red entre segundo y tercer transistor

La siguiente red a analizar en el simulador electromagnético es la que conecta al transistor segundo con el tercero. Como sucedió con anterioridad se genera el layout automáticamente obteniendo la Figura 48.

**Figura 48.** Layout de la red que conecta al transistor nº 2 con el nº 3.

Se comparan los resultados, en la Figura 49, obtenidos en la simulación electromagnética (azul) y en la simulación en esquemático (rojo). En este caso los resultados siguen asemejándose aunque se podría mejorar el puerto 3 ya que presenta unos 8 dB de diferencia.

**Figura 49.** Comparativa simulación electromagnética (azul) y simulación en esquemático (rojo) de la red que conecta transistor 2 y 3.

A continuación se añade la simulación electromagnética al esquemático del LNA y se visualizan los resultados, con la red entrada, red que conecta transistor primero y segundo y la red que conecta transistor segundo y tercero en simulación electromagnética y lo demás con simulación en esquemático.

En primer lugar en la Figura 50 se observa en la parte derecha la ganancia en transferencia  $S_{21}$  del LNA obteniendo de valor medio  $|S_{21}|=28.26$  dB, con un rizado de 0.92 dB. A la izquierda en rojo la figura mínima de ruido con un valor medio de  $NF=1.38$  dB.

**Figura 50.** Figura de ruido (rojo) y ganancia en transferencia (azul) incluyendo la simulación electromagnética de la red que conecta transistor 2 y 3.

En la Figura 51 se observa la adaptación de entrada (rojo) y la adaptación de salida (azul) en la banda de trabajo de 35 a 47 GHz, el valor medio de la adaptación de entrada es  $|S_{11}|=-20.54$ , sin embargo se tienen a frecuencias bajas y altas adaptaciones por debajo de los -10 dB, como se está observando este parámetro es el que más guerra está dando. El valor medio de la adaptación de salida es  $|S_{22}|=-23.21$ , en este caso se sigue manteniendo en todo el rango una adaptación muy buena por debajo de -15 dB.

**Figura 51.** Adaptación de entrada (rojo) y adaptación de salida (azul) incluyendo la simulación electromagnética de red que conecta transistor 2 y 3.

En la Figura 52 se analiza la estabilidad del LNA mediante el factor  $\mu$  y como se observa el amplificador sigue siendo incondicionalmente estable con un valor mínimo de 2.042.

**Figura 52.** Factor de estabilidad  $\mu$  incluyendo la red que conecta transistor 2 y 3.

#### 4.5.5 Red entre el tercer y el cuarto transistor

Esta red conecta los transistores tercero y cuarto entre sí. En la Figura 53 se representa el layout generado automáticamente de esta red a partir del cual se realiza la simulación electromagnética.

**Figura 53.** Layout de la red que conecta al transistor nº 3 con el nº 4.

Se comparan los resultados obtenidos en la simulación electromagnética (azul) y en la simulación en esquemático (rojo), mostrado en la Figura 54.

**Figura 54.** Comparativa simulación electromagnética (azul) y simulación en esquemático (rojo) de la red que conecta transistor 3 y 4.

A continuación se añade la simulación electromagnética al esquemático del LNA y se visualizan los resultados, con la red entrada, red que conecta transistor nº1 y 2, red que conecta transistor nº 2 y 3 y red que conecta transistor nº 3 y 4 en simulación electromagnética y lo demás con simulación en esquemático.

En primer lugar en la Figura 55 se observa en la parte derecha la ganancia en transferencia  $S_{21}$  del LNA obteniendo de valor medio  $|S_{21}|=31.74$  dB, con un rizado de 2.65 dB. A la izquierda en rojo la figura mínima de ruido con un valor medio de  $NF=1.38$  dB.

**Figura 55.** Figura de ruido (rojo) y ganancia en transferencia (azul) incluyendo la simulación electromagnética de la red que conecta transistor 3 y 4.

En la Figura 56 se observa la adaptación de entrada (rojo) y la adaptación de salida (azul) en la banda de trabajo es 35 a 47 GHz, el valor medio de la adaptación de entrada es  $|S_{11}|=-16.65$ , sin embargo se tienen a frecuencias bajas y altas adaptaciones por debajo de los -10 dB, aunque se ha mejorado respecto a la anterior simulación. El valor medio de la adaptación de salida es  $|S_{22}|=-15.09$ , en este caso se sigue manteniendo en todo el rango una adaptación muy buena por debajo de -15 dB.

**Figura 56.** Adaptación de entrada (rojo) y adaptación de salida (azul) incluyendo la simulación electromagnética de red que conecta transistor 3 y 4.

En la figura 54 se analiza la estabilidad del LNA mediante el factor  $\mu$  y como se observa el amplificador sigue siendo incondicionalmente estable con un valor mínimo de 2.636.

**Figura 57.** Factor de estabilidad  $\mu$  incluyendo la red que conecta transistor 2 y 3.

#### 4.5.6 Red de salida.

Para finalizar se estudia la red de salida del amplificador de bajo ruido, esta red de salida es definida por el siguiente layout de la Figura 55.

**Figura 58.** Layout de la red de salida.

A continuación se añade la simulación electromagnética al esquemático del LNA y se visualizan los resultados, en este punto todas las redes del amplificador de bajo ruido tienen su funcionamiento según la simulación electromagnética.

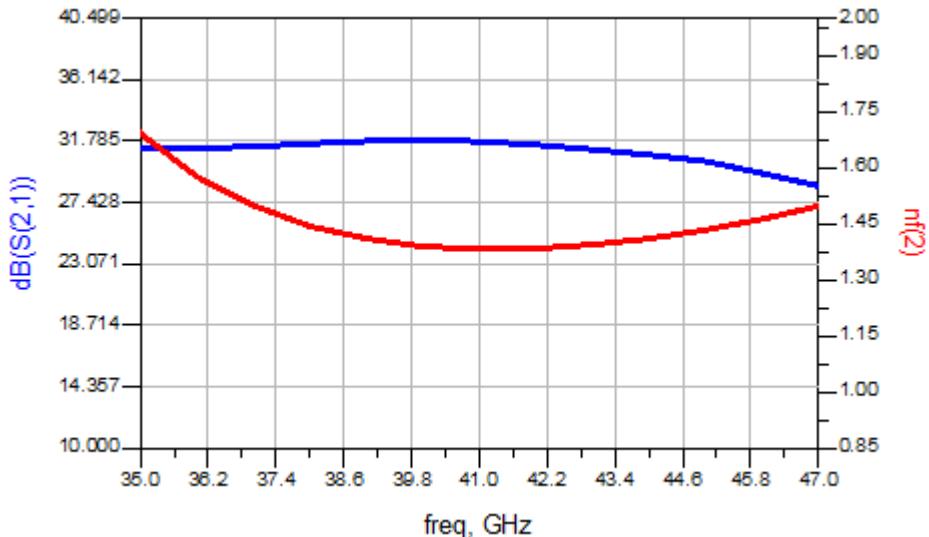

En primer lugar en la Figura 59 se observa en la parte derecha la ganancia en transferencia  $S_{21}$  del LNA obteniendo de valor medio  $|S_{21}|=31.71$  dB, con un rizado de 2.55 dB. A la izquierda en rojo la figura mínima de ruido con un valor medio de  $NF=1.38$  dB.

**Figura 59.** Figura de ruido (rojo) y ganancia en transferencia (azul) incluyendo la simulación electromagnética de la red de salida.

En la Figura 60 se observa la adaptación de entrada (rojo) y la adaptación de salida (azul) en la banda de trabajo es 35 a 47 GHz, el valor medio de la adaptación de entrada es  $|S_{11}|=-16.2$ , sin embargo se tienen a frecuencias bajas y altas adaptaciones por debajo de los -10 dB. El valor medio de la adaptación de salida es  $|S_{22}|=-24.41$ , en este caso se sigue manteniendo en todo el rango una adaptación muy buena por debajo de -15 dB.

**Figura 60.** Adaptación de entrada (rojo) y adaptación de salida (azul) incluyendo la simulación electromagnética de la red de salida.

En la Figura 61 se analiza la estabilidad del LNA mediante el factor  $\mu$  y se observa que el amplificador va a ser incondicionalmente estable con un valor mínimo de 2.3.

**Figura 61.** Factor de estabilidad  $\mu$  con la red de salida.

#### 4.5.7 Diseño del layout.

Una vez se tiene el diseño del LNA optimizado con simulaciones electromagnéticas, se procede a realizar el layout automático del amplificador de bajo ruido completo. A la hora del optimizado del diseño había que tener en cuenta unas consideraciones para que el layout cumpla con todas las normas de diseño que vienen expresadas en la librería de OMMIC. Algunas de estas reglas de diseño son las siguientes:

- Todas las puertas de los transistores deben estar alineadas con el eje X.

- Distancias entre líneas en la capa IN mayores de 3  $\mu\text{m}$ .

- Que la distancia entre centros de los pasos a masa superior a 250  $\mu\text{m}$  para una correcta realización de la celda y así evitar posibles roturas.

- Evitar tener en el centro del layout un paso a masa o vía hole.

- Comprobar que el acople entre las líneas y los TEE, y las líneas y los condensadores es el correcto.

- Condensadores con una geométrica lo más cuadrada posible.

Estas normas de diseño que nos indica la librería OMMIC, han sido verificadas en nuestro layout utilizando la herramienta “DRC” de ADS, que lo que hace es realizar un chequeo del layout y comprobar que cumple con todas las normas de diseño.

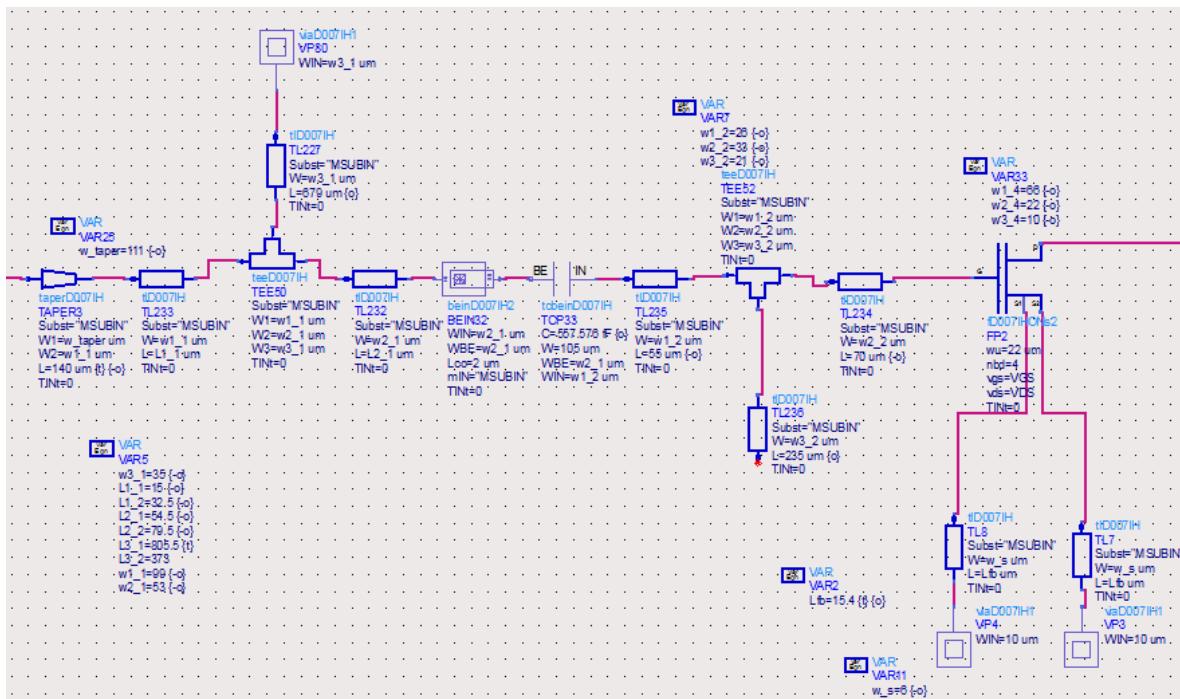

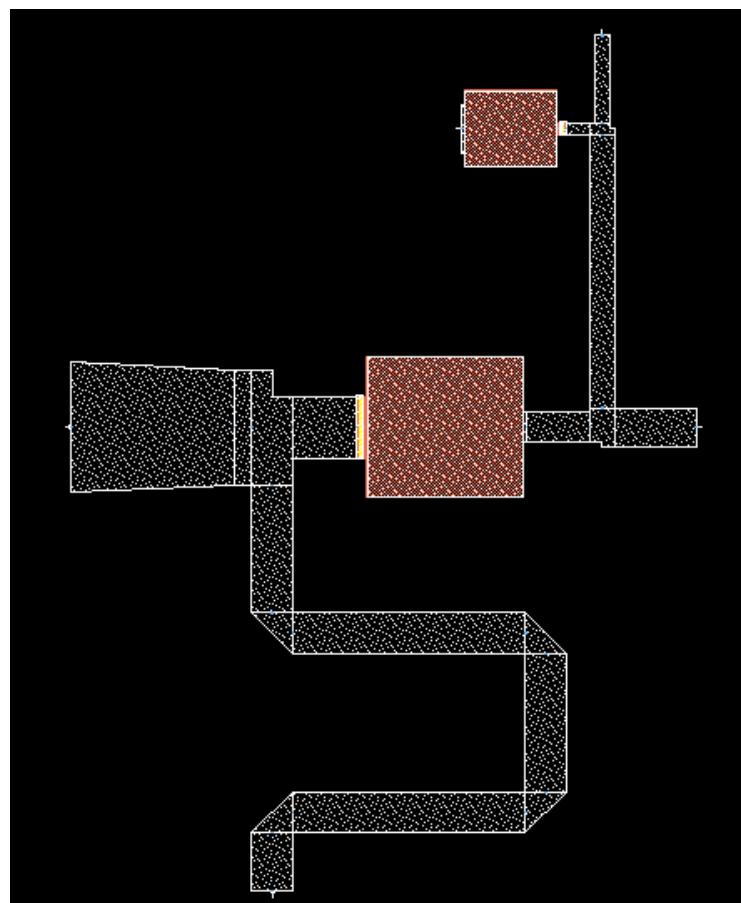

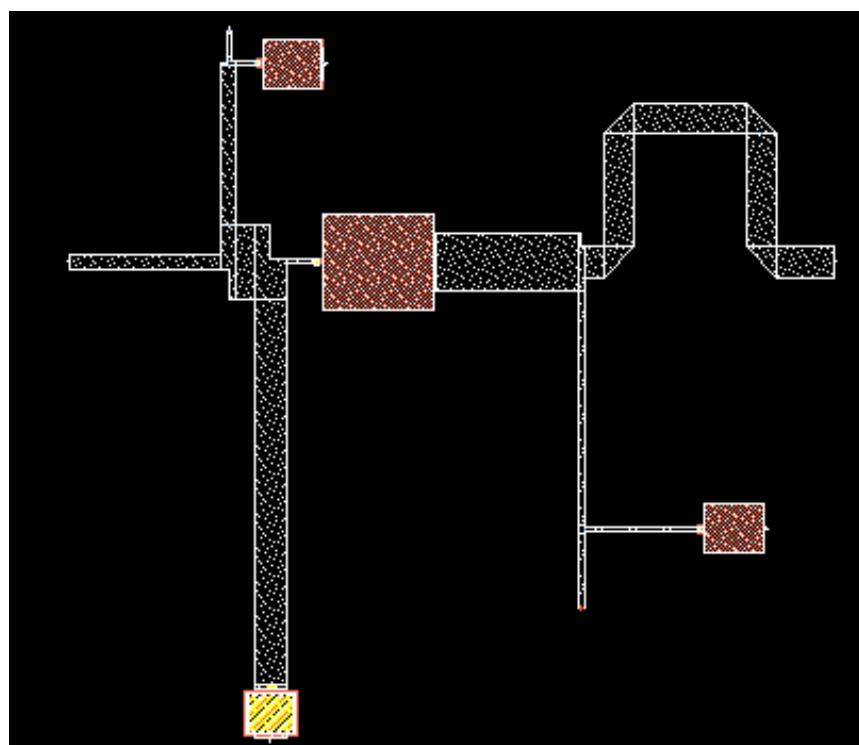

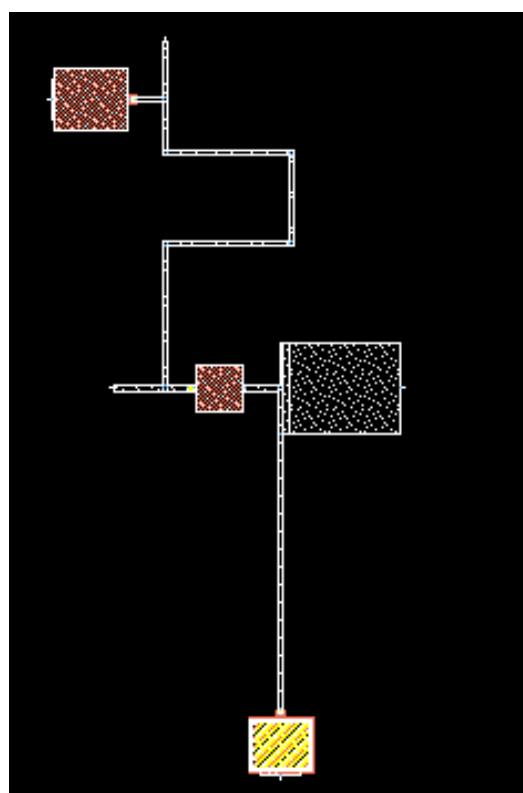

Teniendo en cuenta todos estos aspectos se obtiene el siguiente layout Figura 62:

Figura 62. Layout del amplificador de bajo ruido (LNA)

#### 4.5.8 Valoración del diseño electromagnético.

Una vez realizado la simulación electromagnética de las redes del LNA, se comprueba que su comportamiento sigue siendo igual de bueno que el que se tenía en el diseño en esquemático.

El primer parámetro a analizar es la estabilidad del circuito Figura 65, este parámetro es crítico puesto que si el LNA es inestable, se pueden producir realimentaciones de señales a frecuencias normalmente bajas que perturban el comportamiento del LNA. Sin embargo en nuestro diseño el factor de estabilidad  $\mu$  es siempre mayor que 1 en un amplio rango de frecuencias (desde 1-100 GHz) de modo que nuestro amplificador de bajo ruido es incondicionalmente estable.

El segundo parámetro a analizar es la figura de ruido del LNA Figura 60 (rojo), en las especificaciones se marcó como objetivo una figura de ruido menor de 2.8 dB, y se cumple con valor sensiblemente menor. El valor medio de la figura de ruido es 1.38 dB, con un valor máximo en la banda de trabajo de 1.69dB.