### Departamento de Tecnología Electrónica Ingeniería de Sistemas y Automática

TESIS DOCTORAL

### Corrección de Factor de Potencia basada en la estimación digital de la corriente de línea Aplicación en el Convertidor Boost en modo de conducción continua

Víctor Manuel López Martín

2013

Escuela Técnica Superior de Ingenieros Industriales y de Telecomunicación

## Digital power factor correction based on line-current estimation CCM Boost converter appplication

PhD Thesis

For obtaining the PhD degree

Víctor Manuel López Martín

2013

Escuela Técnica Superior de Ingenieros Industriales y de Telecomunicación

### Universidad de Cantabria Department Of Tecnología Electrónica, Ingeniería de Sistemas y Automática

The undersigned hereby certify that they have read and recommend to the Escuela Técnica Superior de Ingenieros Industriales y de Telecomunicación for acceptance a thesis entitled "Digital power factor correction based on line-current estimation" by Víctor Manuel López Martín in partial fulfillment of the requirements for the degree of PhD Thesis.

Dated: <u>2013</u>

| Advisor:                |                                |

|-------------------------|--------------------------------|

|                         | Professor Francisco J. Azcondo |

|                         |                                |

| Dissertation Committee: |                                |

| Chair                   |                                |

|                         | Professor Paolo Matavelli      |

|                         |                                |

| Reader:                 |                                |

Professor Javier Sebastian

Professor Alberto Pigazo

Reader:

A mis padres, Marisa y Pedro

${\cal A}$ Inés

## Agradecimientos/Acknowledgements

En este documento se muestra una parte importante del trabajo realizado desde Octubre del año 2008, en el que comencé mi proyecto fin de carrera, y que desembocaría posteriormente en esta Tesis. Durante este tiempo han sido muchas personas las que me han ayudado y que merecen un agradecimiento especial:

Paco Azcondo, tutor de esta Tesis, que me ha mostrado su apoyo, confianza y paciencia; y que me ha sabido ilustrar y enseñar la luz siempre que me han surgido dudas.

A Charo, Christian y Javi por ayudarme siempre que lo he necesitado.

Alejandro, mi grandísimo amigo y compañero. Hemos compartido una cantidad ingente de horas juntos en el Laboratorio, con las que he disfrutado y aprendido cómo nunca habría imaginado. Una parte de esta Tesis es gracias a tí, ya lo sabes.

Regan Zane, many thanks for your support during my time with you in Boulder and Logan. All your comments have helped me to improve my knowledge about Power Electronics.

Mi familia, con mis padres a la cabeza, por ayudarme a llegar aquí sin ninguna preocupación más allá que mi propio trabajo.

Inés, tu apoyo y comprensión infinita desde el primer día han sido una bocanada de oxígeno en la consecución de esta Tesis. Todo lo que pueda decir es poco.

Y a mis amigos, que han entendido mis ausencias por las horas invertidas en esta Tesis.

Santander, Cantabria, Spain 2013

Víctor Manuel López Martín

## Abstract

Continuous conduction mode (CCM) power factor correction (PFC) without input current measurement is a step forward with respect to previously proposed PFC digital controllers. Inductor volt-second  $(vs_L)$  measurement in each switching period enables the digital estimation of the input current, used in the inner current loop. However, an accurate compensation of the small inaccuracies in the measured  $vs_L$  is required in the estimation, to match the actual current. Otherwise, these errors are accumulated every switching period over the half line cycle, leading to an appreciable current distortion.

A  $vs_L$  estimation method is proposed in this Thesis, measuring the input  $(v_g)$  and the output voltage  $(v_o)$ . Discontinuous conduction mode (DCM) occurs near input line zero crossings, and is also detected by measuring the drain-to-source MOSFET voltage,  $v_{ds}$ . Parasitic elements also cause a small difference between the estimated voltage across the inductor, based on input and output voltage measurements, and the actual one, which must be taken into account to estimate the input current in the proposed sensorless PFC digital controller.

This Thesis analyzes deeply the current estimation inaccuracies caused by errors in the ONtime estimation, voltage measurements, and the parasitic elements. A new digital feedback control with high resolution is also proposed to cancel the difference between DCM operation time of the real input current  $T_{DCM}^g$ , and the estimated DCM time  $T_{DCM}^{reb}$ . Therefore, the current estimation is calibrated using digital signals during operation in DCM.

A fast feedforward coarse time error compensation is carried out with the measured delay of the drive signal, and then a fine compensation is achieved with the feedback loop that matches the estimated and real DCM times. With this contribution, an universal controller is proposed. The digital controller can be used in universal applications due to the ability of the DCM time feedback loop to autotune based on the operation conditions (power level, input voltage, output voltage...), which improves the operation range in comparison with previous solutions.

Furthermore, an additional improvement is presented in this controller in which the current

demanded by the Sensorless PFC rectifier is pure sinusoidal despite the non-sinusoidal input voltage of the grid. This contribution is really interesting in applications where the harmonics limits are stricter (like in aircraft systems) and must be fulfilled independently on the voltage waveshape. This modification is totally done into the digital controller without any need of extra analog components.

Experimental results are shown for a 1 kW boost PFC converter over a wide power and voltage range. The digital controller is implemented in a *field programmable gate array* (FPGA) with a very simple analog circuitry to adapt the signals needed by the controller. The behavior of the controller, applied in lighting systems is also shown.

# Contents

| A             | grade                           | ecimientos/Acknowledgements vii                                                                                                                                                                                                                                                               |

|---------------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A             | bstra                           | viii                                                                                                                                                                                                                                                                                          |

| $\mathbf{Li}$ | st of                           | Figures xxii                                                                                                                                                                                                                                                                                  |

| $\mathbf{Li}$ | st of                           | Tables     xxiii                                                                                                                                                                                                                                                                              |

| N             | omer                            | nclature xxv                                                                                                                                                                                                                                                                                  |

| 0             | Intr                            | roducción 1                                                                                                                                                                                                                                                                                   |

| 1             | Intr                            | roduction 9                                                                                                                                                                                                                                                                                   |

| 2             | Bac<br>2.1<br>2.2<br>2.3<br>2.4 | Ekground17Power factor correction17Standards about line current harmonics and power factor value19Digital control of Switched Mode Power Supplies21PFC converters262.4.1 Boost converter. Fundamentals282.4.2 Analog Control in PFC converters312.4.3 Digital control in PFC converters34     |

|               | 2.5                             | Current Sensing in Switched Mode Power Supplies352.5.1Current sensor362.5.2 $R_{on}$ sensing372.5.3Filter-sense the Inductor392.5.4Current transformer sensor402.5.5Current-average technique412.5.6Hall-effect sensor422.5.7Case study: Losses in a PFC stage with resistor current sensor42 |

|               | 2.6                             | Digital power factor correction controllers with current sensor                                                                                                                                                                                                                               |

|               | 2.7                             | Digital power factor correction controllers without current sensor                                                                                                                                                                                                                            |

|               | 2.8                             | Thesis Approach                                                                                                                                                                                                                                                                               |

| 3        | Cur       | rrent estimation. Current control algorithm and errors                                                                                                               | 51                                      |

|----------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

|          | 3.1       | Current rebuilding. Theoretical concept.                                                                                                                             | 51                                      |

|          | 3.2       | Power factor correction algorithm. Non-linear carrier (NLC) control $\ldots$ .                                                                                       | 54                                      |

|          | 3.3       | Current estimation errors. Boost Converter                                                                                                                           | 59<br>61                                |

|          |           | device, and the voltage across the inductor                                                                                                                          | $\begin{array}{c} 61 \\ 67 \end{array}$ |

|          |           | 3.3.2Effect of errors in data capture of voltage across the inductor3.3.3Errors due to difference between real inductance $L$ and the estimated inductance $L_{est}$ | 07<br>73                                |

|          | 3.4       | Chapter conclusion                                                                                                                                                   | 74                                      |

| 4        | Infl      | uence of the converter parasitics in the current estimation                                                                                                          | 77                                      |

|          | 4.1       | Modeling the parasitic elements effect with the Equivalent Parasitic Element<br>in series with the input voltage $(EPE_g)$                                           | 81                                      |

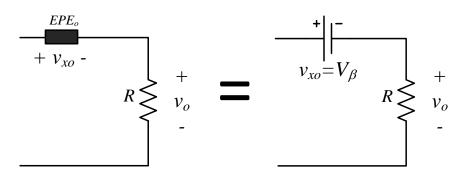

|          | 4.2       | Modeling the parasitic elements effect with the Equivalent Parasitic Element<br>in series with the output voltage $(EPE_o)$                                          | 84                                      |

|          | 4.3       | Chapter conclusion                                                                                                                                                   | 87                                      |

| <b>5</b> | Dig       | ital controller implementation                                                                                                                                       | 89                                      |

|          | 5.1       | Current rebuilding. Digital implementation and quantization effects                                                                                                  | 89                                      |

|          | 5.2       | Drive signal delays compensation. Feedforward compensation in terms of time (clock cycles)                                                                           | 94                                      |

|          | 5.3       | Discontinuous Conduction Auxiliary Detection Circuit                                                                                                                 | 96                                      |

|          | 5.4       | Feedback compensation of the DCM time discrepancy $\ldots \ldots \ldots \ldots \ldots$                                                                               | 98                                      |

|          | 5.5       | Chapter conclusion                                                                                                                                                   | 103                                     |

| 6        | Mo<br>ban | del of the high-resolution error compensator. Steady-state gain and low<br>dwidth model                                                                              | ,<br>105                                |

|          | 6.1       | Steady state model. DC analysis                                                                                                                                      | 105                                     |

|          | 6.2       | Small-signal AC model. Low bandwidth loop                                                                                                                            | 111                                     |

|          | 6.3       | Chapter conclusion                                                                                                                                                   | 113                                     |

| 7        | Low       |                                                                                                                                                                      | 115                                     |

|          | 7.1       | Introduction to distorted grids                                                                                                                                      | 115                                     |

|          | 7.2       | Definitions of Electric Power Quantities                                                                                                                             | 117                                     |

|          | 7.3       | Low THDi controller under distorted voltages                                                                                                                         | 119                                     |

|          | 7.4       | Chapter conclusion                                                                                                                                                   | 123                                     |

| 8        | Exp       | perimental validation                                                                                                                                                | 125                                     |

|          | 8.1       | Boost converter prototype                                                                                                                                            | 125                                     |

|          | 8.2       | Operation in Steady state                                                                                                                                            | 129                                     |

|          | 8.3       | Time evolution under different conditions                                                                                                                            | 138                                     |

|          | 8.4       | Operation under distorted voltage. Resistance or pure sinusoidal current behavior                                                                                    | 150                                     |

|          | 8.5       | Chapter conclusion                                                                                                                                                   | 152                                     |

| 9            |        | mple of application: Digital PFC controllers for HID lamps electroni<br>ast applications                                                                               | с<br>153 |

|--------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|              | 9.1    | Introduction                                                                                                                                                           | 153      |

|              | 9.2    | Outer voltage loop in the digital PFC controller                                                                                                                       | 155      |

|              | 9.3    | Input voltage fluctuations detection algorithm                                                                                                                         | 157      |

|              | 9.4    | Experimental results                                                                                                                                                   | 159      |

|              | 9.5    | Chapter conclusion                                                                                                                                                     | 162      |

| 10           | Con    | clusions                                                                                                                                                               | 167      |

|              | 10.1   | Summary of contributions                                                                                                                                               | 168      |

|              | 10.2   | Future works                                                                                                                                                           | 169      |

| 11           | Pub    | lished papers                                                                                                                                                          | 171      |

|              | 11.1   | Journals                                                                                                                                                               | 171      |

|              |        | 11.1.1 In review                                                                                                                                                       | 171      |

|              | 11.2   | International Conferences                                                                                                                                              | 171      |

|              | 11.3   | Spanish Conferences                                                                                                                                                    | 173      |

| Re           | eferei | nces                                                                                                                                                                   | 175      |

| $\mathbf{A}$ | Defi   | nition of the rebuilt input current RMS value $I_{reb}$                                                                                                                | 191      |

|              | A.1    | Linearization of the expression $\ldots \ldots \ldots$ | 191      |

# **List of Figures**

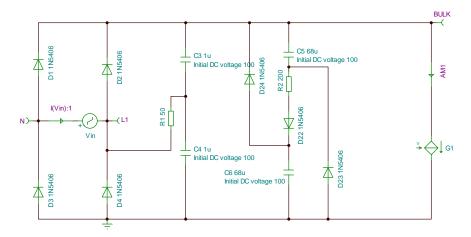

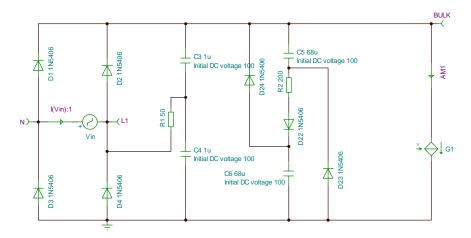

| 1   | Circuito Valley-fill.                                                                                                                                                                                                        | 2  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

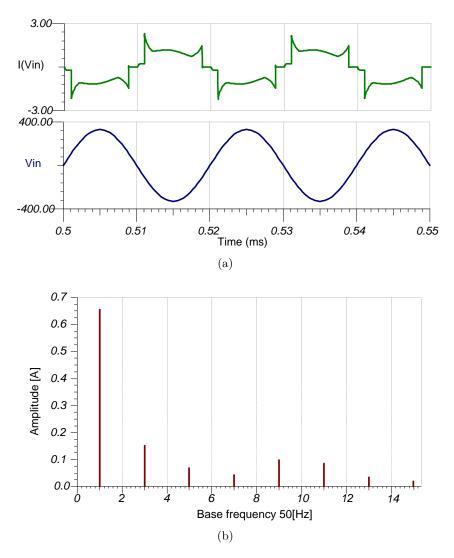

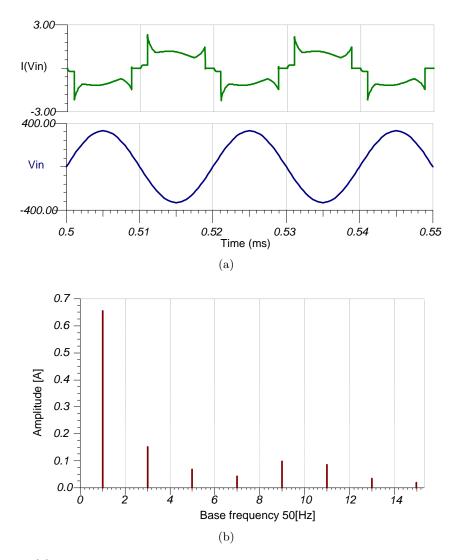

| 2   | (a) Formas de onda del circuito <i>Valley-fill</i> . Arriba: Corriente de entrada. Abajo:<br>Tensión de entrada. (b) Contenido armónico de la corriente de línea.                                                            | 3  |

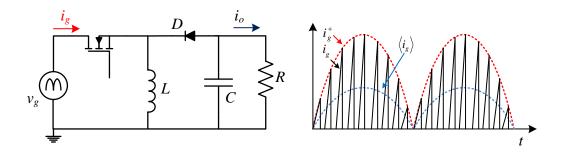

| 3   | Convertidor Buck-boost trabajandor como resistencia en modo natural. $\ .$ .                                                                                                                                                 | 3  |

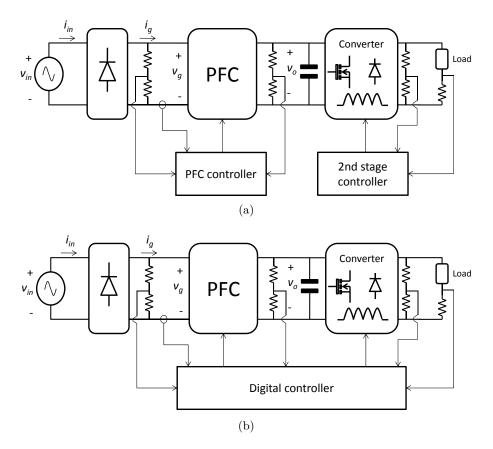

| 4   | Esquemas de sistemas de alimentación: (a) Esquema tradicional con etapa PFC con control analógico y dispositivo digital controlando el convertidor posterior. (b) Integración digital completa del control de las dos etapas | 5  |

| 5   | Esquema típico de rectificador PFC con control digital y circuito de sensado de corriente.                                                                                                                                   | 6  |

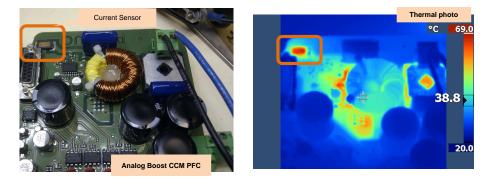

| 6   | Izq: Imagen de un convertidor Boost PFC con control analógico, usando el controlador comercial UC3854 de Unitrode. Der: Foto térmica del convertidor trabajando a plena carga.                                               | 6  |

| 1.1 | Valley-fill circuit.                                                                                                                                                                                                         | 10 |

| 1.2 | (a) Valley-fill waveforms. Upper trace: Input current. Lower trace: Input voltage. (b) Harmonics of the line current.                                                                                                        | 11 |

| 1.3 | Buck-boost converter working as a PFC rectifier                                                                                                                                                                              | 11 |

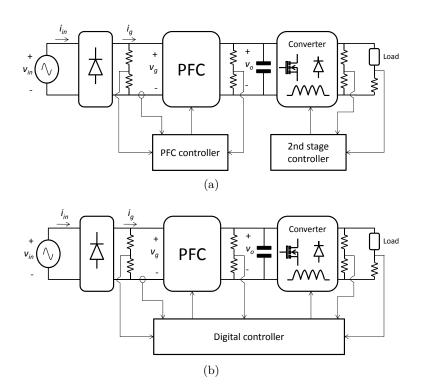

| 1.4 | Switched mode power supply scheme. (a) Traditional approach with a PFC stage with analog control and a digital device for the second stage. (b) Complete digital implementation of the two stages control.                   | 13 |

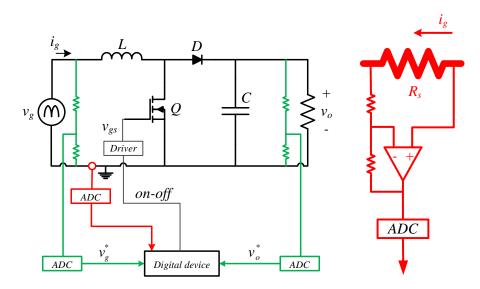

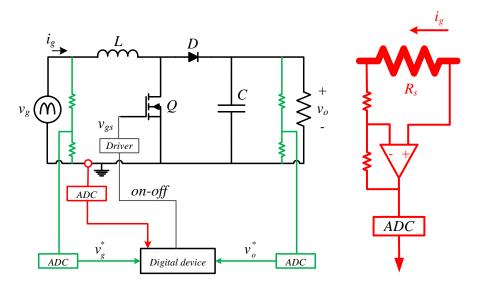

| 1.5 | Typical scheme of a digitally controlled PFC converter with the current sensor circuit.                                                                                                                                      | 14 |

| 1.6 | Left: Picture of a PFC Boost analog converter controlled by the UC3854 of Unitrode. Right: Thermal picture of the converter at nominal power.                                                                                | 14 |

| 2.1 | Line current (blue) in the Power Electronics Lab of the University of Cantabria at Santander (Spain) in June 2012. In red is plotted the sinusoidal waveform whose RMS values is equal to the line current.                  | 20 |

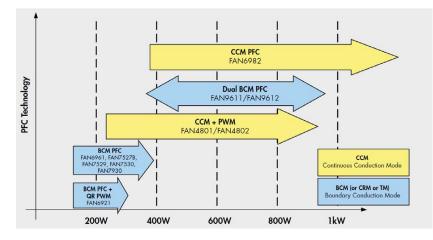

| 2.2 | Fairchild PFC technology portfolio                                                                                                                                                                                           | 27 |

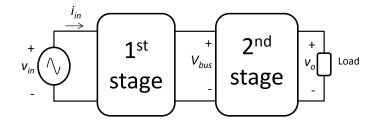

| 2.3 | Typical power supply block diagram                                                                                                                                                                                           | 28 |

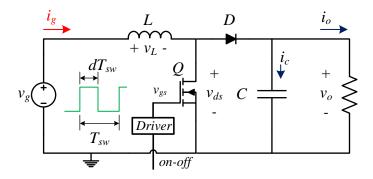

| 2.4 | DC-DC boost converter                                                                                                                                                                                                        | 29 |

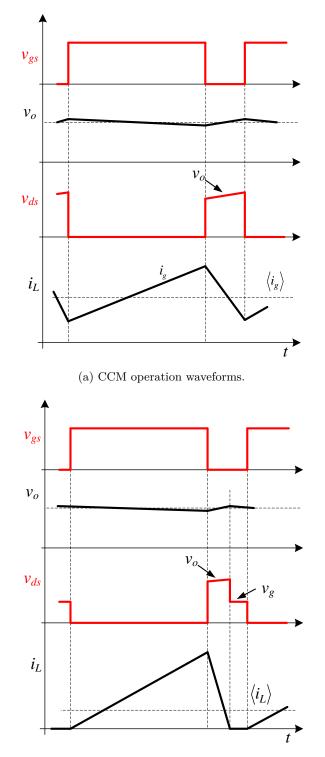

| 2.5 | Boost converter waveforms in CCM (a) and DCM (b). MOSFET gate signal $(v_{gs})$ , inductor current $(i_L)$ , MOSFET drain-to-source voltage $(v_{ds})$ and output voltage $(v_o)$ .                                          | 30 |

| 2.6  | Block diagram of the average current mode control in a Boost converter                                                                                                                                                                                                                                        |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.7  | Waveforms of critical conduction mode control in the boost converter                                                                                                                                                                                                                                          |

| 2.8  | Left: Block diagram of nonlinear carrier control (boost example). Right:<br>Waveforms of nonlinear carrier control (boost example) [15]                                                                                                                                                                       |

| 2.9  | Current sensing options in a power converter                                                                                                                                                                                                                                                                  |

| 2.10 | Resistor inductance combined with high $di/dt$ can cause voltage spikes in the current measurement.                                                                                                                                                                                                           |

| 2.11 | (a) MOSFET $R_{on}$ Current Sensing scheme and (b) Normalized drain-to-source ON-resistance $R_{on}$ , vs Junction Temperature for the IRF840 Power MOSFET of Fairchild.                                                                                                                                      |

| 2.12 | Sensing the inductor current by measuring the inductor voltage with a RC filter in a boost converter.                                                                                                                                                                                                         |

| 2.13 | Current transformer equivalent circuit                                                                                                                                                                                                                                                                        |

| 2.14 | Averaging the inductor voltage to sense the current.                                                                                                                                                                                                                                                          |

| 2.15 | Boost PFC converter scheme considering losses                                                                                                                                                                                                                                                                 |

| 2.16 | Average current sensor scheme                                                                                                                                                                                                                                                                                 |

| 2.17 | Operating waveforms of the average current sensor.                                                                                                                                                                                                                                                            |

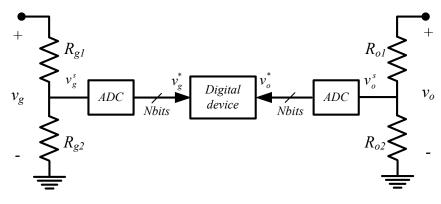

| 2.18 | Voltage sensor approach used to obtain the digital data of the input and output voltages. Scheme for the input voltage.                                                                                                                                                                                       |

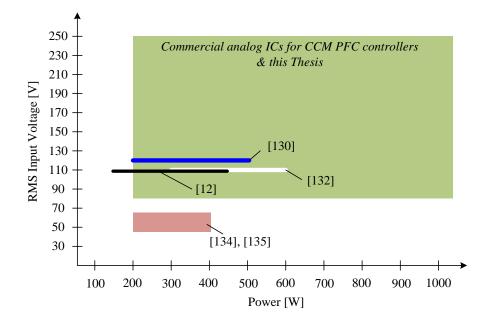

| 2.19 | Input voltage and power range of the recent works in sensorless PFC con-<br>trollers. The green area represents the goal of this Thesis.                                                                                                                                                                      |

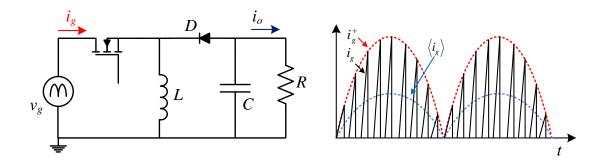

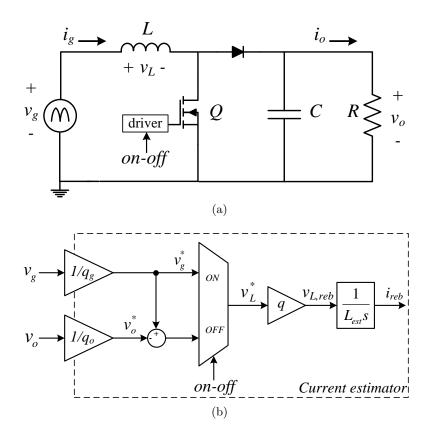

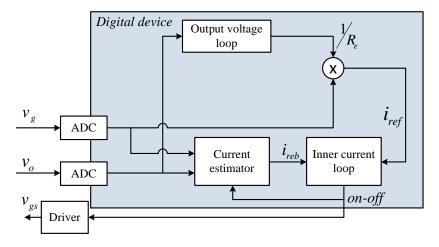

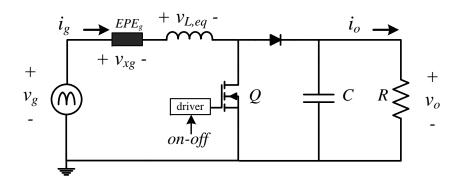

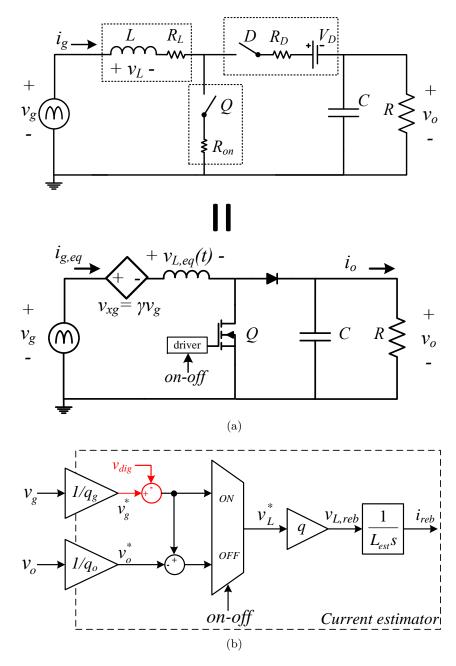

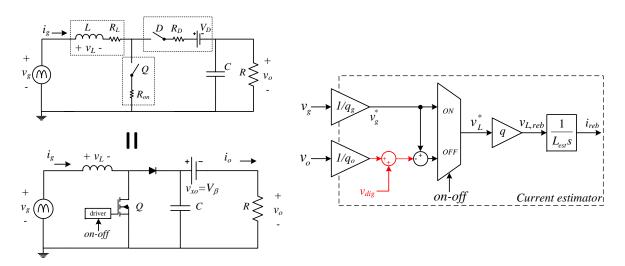

| 3.1  | (a) Boost converter basic scheme and (b) basic simulation model of the sensorless Boost PFC converter current estimator.                                                                                                                                                                                      |

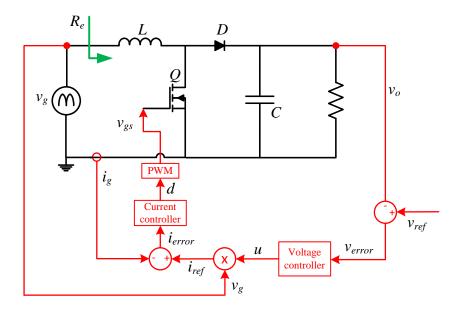

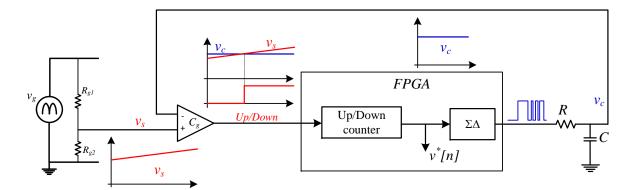

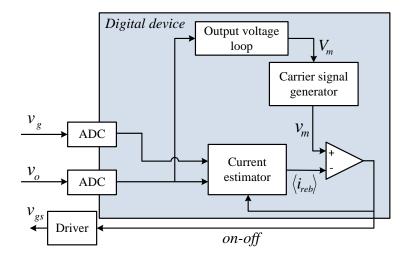

| 3.2  | Schematic of the sensorless current controller                                                                                                                                                                                                                                                                |

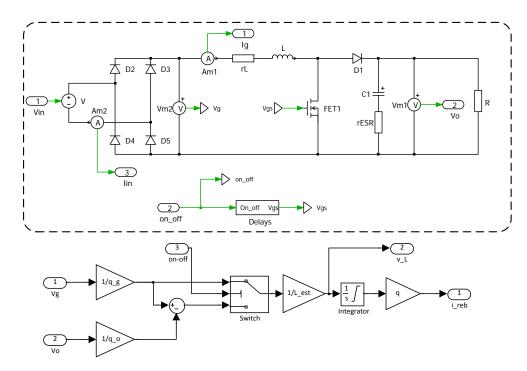

| 3.3  | Simulations Blocks in Simulink® with PLECS® toolbox. Top: PLECS® sub-<br>circuit in Simulink® with the switching delays (explained in Section 3.3.1).<br>Bottom: Current estimator Simulink blocks.                                                                                                           |

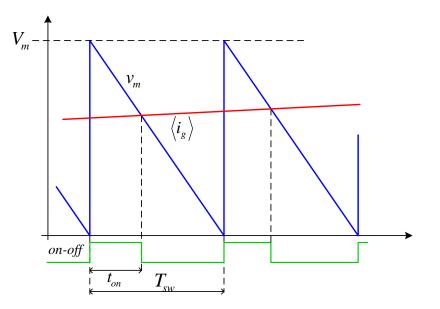

| 3.4  | NLC control waveforms.                                                                                                                                                                                                                                                                                        |

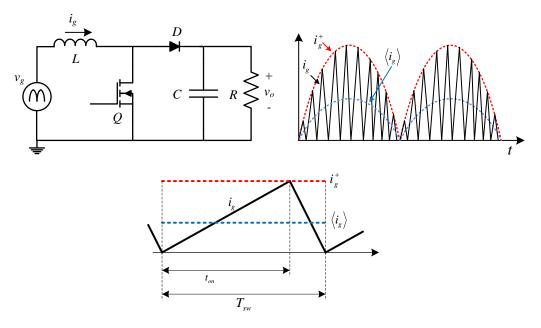

| 3.5  | Schematic of the sensorless current controller with a NLC control                                                                                                                                                                                                                                             |

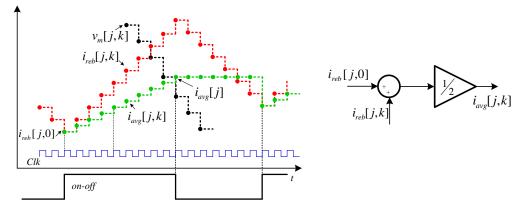

| 3.6  | Left: Digital waveforms of the NLC control with estimation of the average rebuilt current. Right: Hardware implementation blocks of the average rebuilt current estimation.                                                                                                                                   |

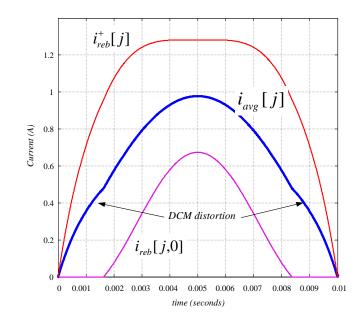

| 3.7  | Half cycle of the input rebuilt current with distortion due to DCM operation around line zero crossings.                                                                                                                                                                                                      |

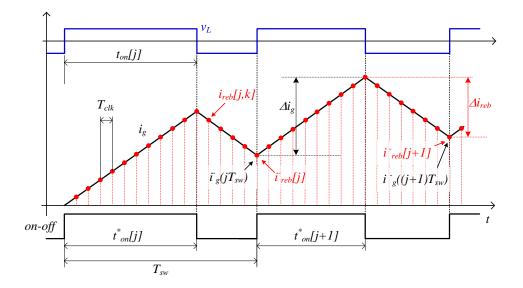

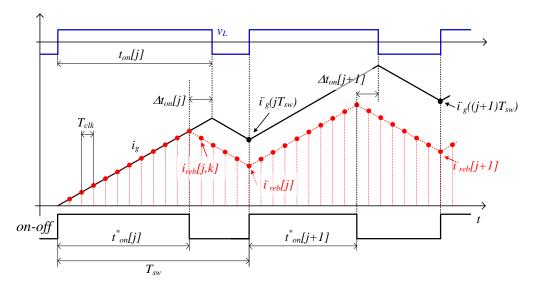

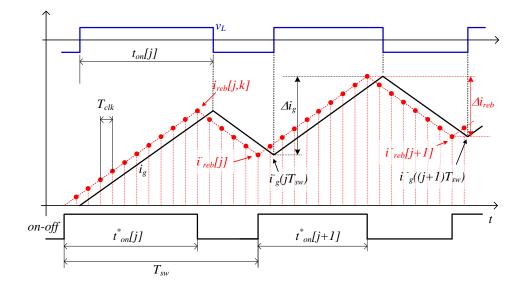

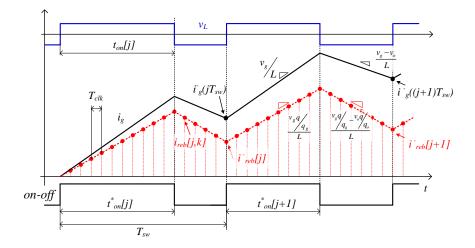

| 3.8  | Digital signal $i_{reb}[j,k]$ , compared with the analog real input current $i_g$ , under ideal conditions. The $on - off$ signal is the output of the digital device and $v_L$ the analog inductor voltage.                                                                                                  |

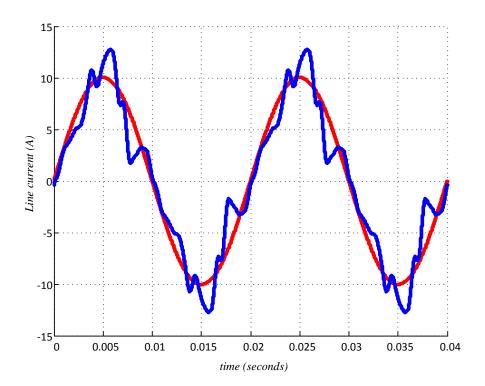

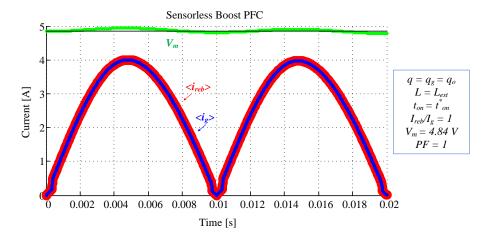

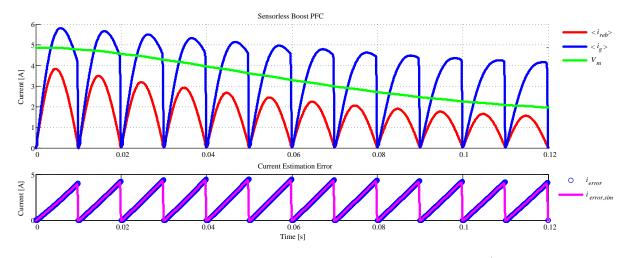

| 3.9  | Simulated waveforms under ideal conditions obtained with the Simulink model<br>of the system with $V_g = 230 V_{rms}$ , $V_o = 400 V_{dc}$ , $P_g \simeq P_o = 640 W$ ( $R = 250 \Omega$ ),<br>$f_{sw} = 100 \ kHz$ and reactive components $L = 1 \ mH$ , and $C = 220 \ \mu F$ , under<br>ideal conditions. |

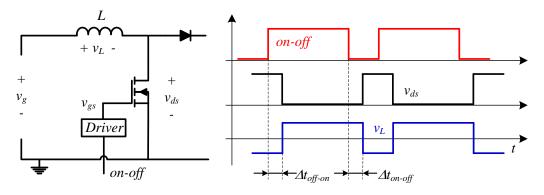

| 3.10 | Boost converter circuit and gate drive signal vs MOSFET $v_{ds}$ and inductor voltage to show the switching delays.                                                                                                                                                                                           |

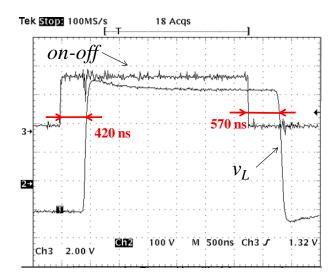

| 3.11 | Experimental time switch transitions $(v_L)$ compared with the output drive signal of the digital device $(on - off)$ .                                                                                                                                                                                       |

| 3.12 | Digital estimated current $i_{reb}[j,k]$ compared with the analog real input current $i_g$ , when the drive signal's delays $\Delta t_{on-off} \neq \Delta t_{off-on}$ . The $on - off$ signal is the output of the digital device, and $v_L$ the inductance voltage                                          |

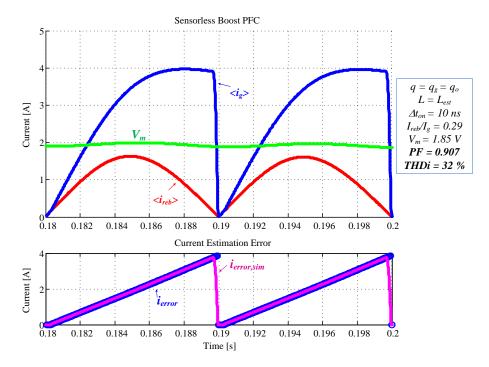

| 3.13 | Transient state simulated waveforms obtained with the Simulink/PLECs system model with $V_g = 230 V_{rms}$ , $V_o = 400 V_{dc}$ , $P_g \simeq P_o = 640 W (R = 250 \Omega)$ , $f_{sw} = 100 kHz$ and reactive components $L = 1 mH$ , and $C = 220 \mu F$ , when $\Delta t_{on} = 10$ ns.                                                    | 65         |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 3.14 | Steady state simulated waveforms with the Simulink/PLECs system model of<br>the system with $V_g = 230 V_{rms}$ , $V_o = 400 V_{dc}$ , $P_g \simeq P_o = 640 W$ ( $R = 250 \Omega$ ),<br>$f_{sw} = 100 kHz$ and reactive components $L = 1 mH$ , and $C = 220 \mu F$ , when<br>$\Delta t_{on} = 10 \text{ ns.}$                              | 66         |

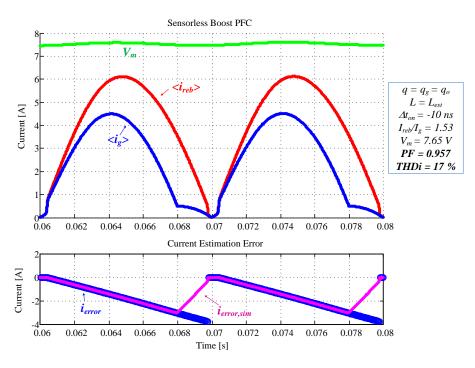

| 3.15 | Steady state simulated waveforms with the Simulink/PLECs system model of the system with $V_g = 230 V_{rms}$ , $V_o = 400 V_{dc}$ , $P_g \simeq P_o = 640 W$ ( $R = 250 \Omega$ ), $f_{sw} = 100 kHz$ and reactive components $L = 1 mH$ , and $C = 220 \mu F$ , when $\Delta t_{on} = -10$ ns                                               | 66         |

| 3.16 | Digital estimated current $i_{reb}[j,k]$ compared with the analog real input current $i_g$ with the drive signal's delays supposing $\Delta t_{on-off} = \Delta t_{off-on}$ . The $on-off$ signal is the output of the digital device, and $v_L$ the inductance voltage                                                                      | 68         |

| 3.17 | Digital estimated current $i_{reb}$ compared with the analog real input current $i_g$ with the drive signal's delays supposing $\Delta t_{on-off} = \Delta t_{off-on}$ . The $on - off$ signal is the output of the digital device, and $v_L$ the inductance voltage                                                                         | 68         |

| 3.18 | Voltage data acquisition scheme.                                                                                                                                                                                                                                                                                                             | 69         |

| 3.19 | Digital estimated current $i_{reb}[j, k]$ , compared with the analog real input current $i_g$ , under errors in data capture voltage across the inductance when $q_g \neq q_o \neq q$ .<br>The $on - off$ signal is the output of the digital device and $v_L$ the analog inductance voltage.                                                | 70         |

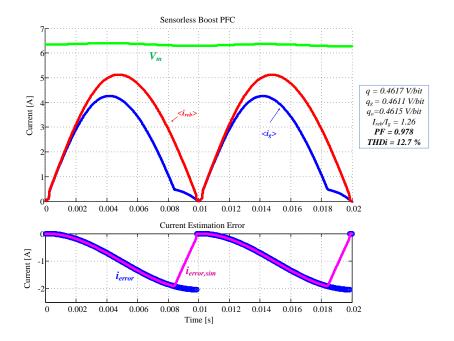

| 3.20 | Steady state simulated waveforms with the Simulink/PLECs system model of the system with $V_g = 230 V_{rms}$ , $V_o = 400 V_{dc}$ , $P_g \simeq P_o = 640 W$ ( $R = 250 \Omega$ ), $f_{sw} = 100 kHz$ and reactive components $L = 1 mH$ , and $C = 220 \mu F$ , when $q = 0.4617 V/bit$ , $q_g = 0.4611 V/bit$ , and $q_o = 0.4615 V/bit$ . | 72         |

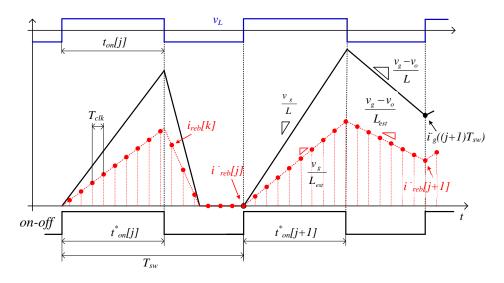

| 3.21 | Digital estimated current $i_{reb}[k]$ compared with the analog real input current $i_g$ when the estimated inductance value $(L_{est})$ is higher than the real $(L)$ . The $on-off$ signal is the output of the digital device, and $v_L$ the inductance voltage.                                                                          | 74         |

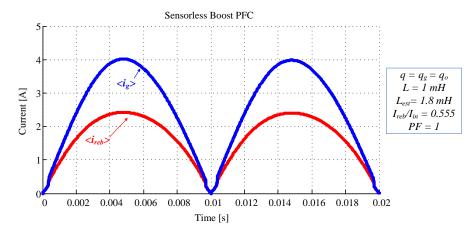

| 3.22 | Steady state simulated waveforms with the Simulink/PLECs system model of the system with $V_g = 230 V_{rms}$ , $V_o = 400 V_{dc}$ , $P_g \simeq P_o = 640 W$ ( $R = 250 \Omega$ ), $f_{sw} = 100 kHz$ and reactive components $L = 1 mH$ , and $C = 220 \mu F$ and $L_{est} = 1.8 mH$ .                                                      | 75         |

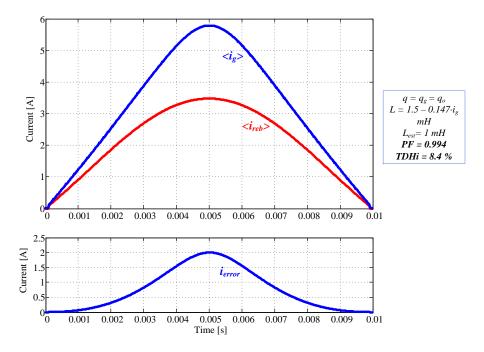

| 3.23 | Simulated current waveforms when the real inductance value $L$ is a function of the current $L(i_L) = 1.5 - 0.174i_L [mH]$ and $L_{est} = 1.5 mH$ . Top: Input current $i_g$ , and rebuilt current $i_{reb}$ . Bottom: Current estimation error $i_{error}$ .                                                                                | 75         |

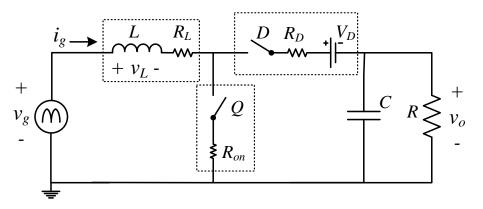

| 4.1  | Boost converter diagram with parasitic elements.                                                                                                                                                                                                                                                                                             | 77         |

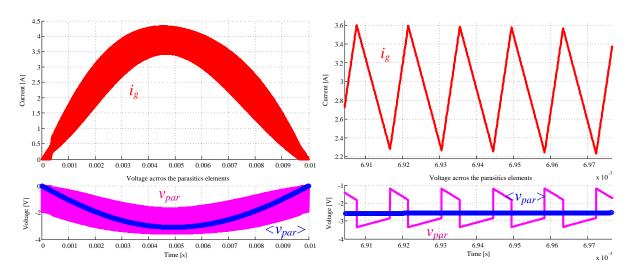

| 4.2  | Input current waveform $i_g$ , instantaneous $v_{par}$ and average voltage drop over<br>the switching cycle in the parasitic elements, $\langle v_{par} \rangle$ . Left: waveforms over the<br>half line cycle. Right: Switching waveforms.                                                                                                  | 79         |

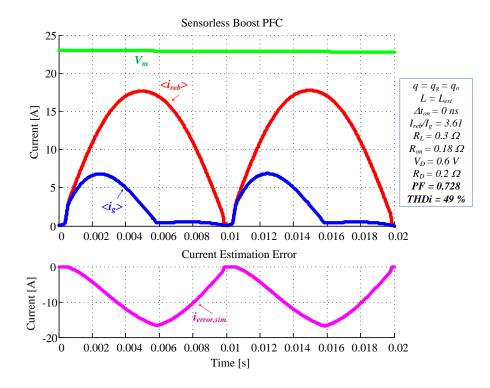

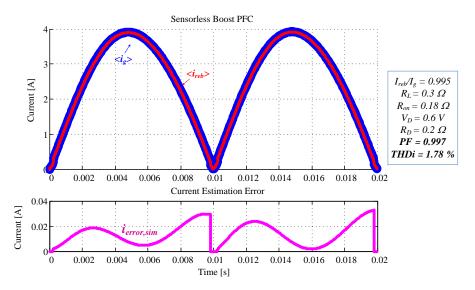

| 4.3  | Simulated current waveforms without consideration of the parasitic elements influence. Top: Real and rebuilt input current. Bottom: Simulated current estimation error.                                                                                                                                                                      | 80         |

| 4.4  | Equivalent boost converter circuit with the EPE connected in series with the                                                                                                                                                                                                                                                                 | <b>Q</b> 1 |

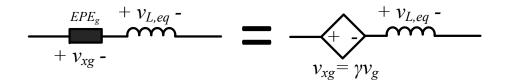

| 4.5  | Inductor                                                                                                                                                                                                                                                                                                                                     | 81<br>82   |

| 4.6  | (a) Equivalent boost converter with the EPE represented by a dependent vol-<br>tage source. (b) Modification of the current estimation block with the com-<br>pensation in the input voltage data.                                                                                                                                           | 83         |

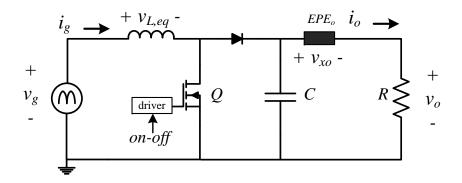

| 4.7  | Equivalent boost converter circuit with the $EPE_o$ connected in series with the output.                                                                                                                                                                                                                                                                                       | 84  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.8  | Equivalence between the Equivalent Parasitic Element and a constant voltage source.                                                                                                                                                                                                                                                                                            | 85  |

| 4.9  | Left: Model of the Boost converter with the influence of the parasitic elements<br>placed in series with the output voltage. Right: Behavioral model of the<br>current estimator block with the digital compensation in the output voltage.                                                                                                                                    | 86  |

| 4.10 | Simulated waveform for the Boost converter sensorless PFC controller when $qv_{dig} = V_{\beta}$ .                                                                                                                                                                                                                                                                             | 87  |

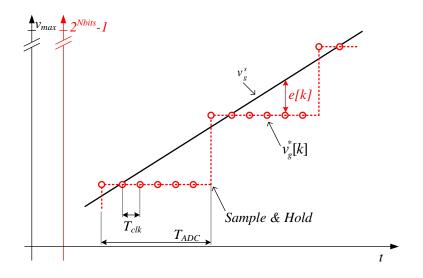

| 5.1  | Representation of the analog-to-digital conversion of the input voltage                                                                                                                                                                                                                                                                                                        | 90  |

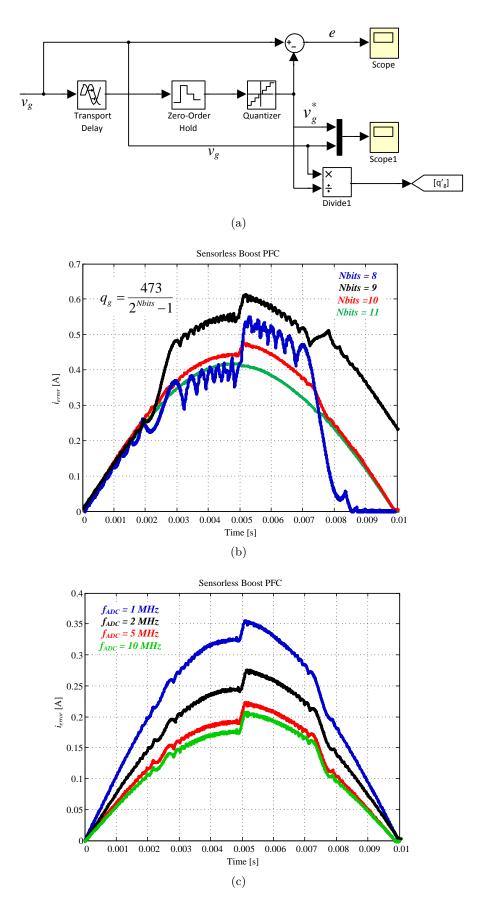

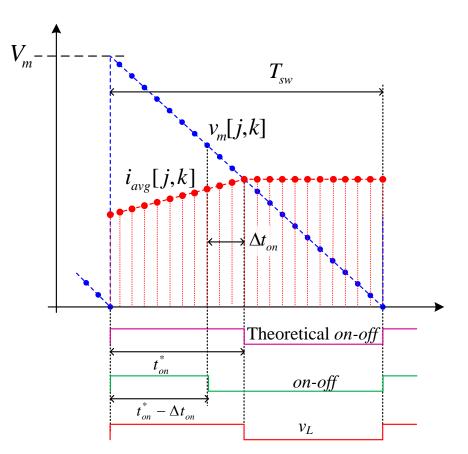

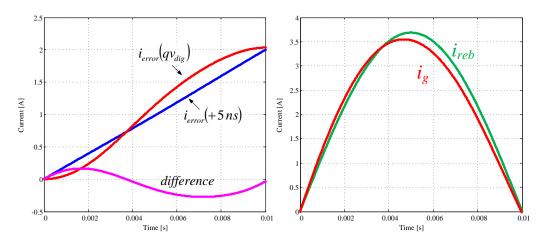

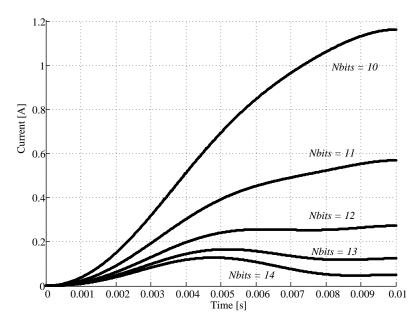

| 5.2  | (a) Simulink model of the input voltage ADC, (b) $i_{error}$ waveform over half utility period for different bits of resolution in the ADCs with a constant ADC sample frequency of $f_{ADC} = 1$ MHz, and (c) for different ADC sampling frequencies and a constant $Nbits = 10. \dots \dots \dots \dots \dots \dots \dots \dots \dots \dots$                                 | 92  |

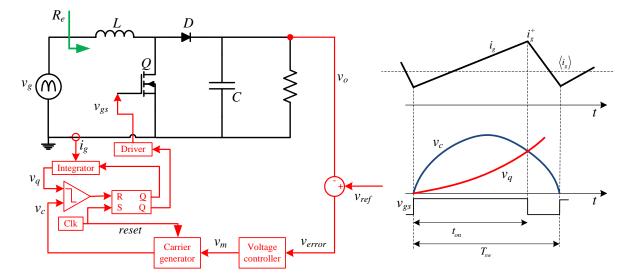

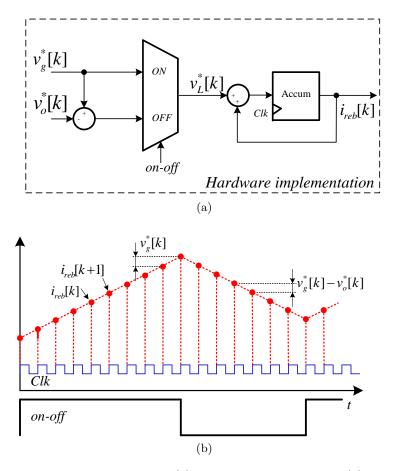

| 5.3  | Current rebuilding concept. (a) Hardware architecture and (b) digital waveforms.                                                                                                                                                                                                                                                                                               | 93  |

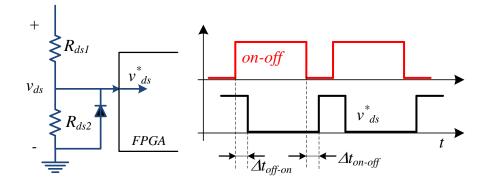

| 5.4  | Auxiliary circuit to adapt the drain-to-source voltage as a digital signal. Com-<br>parison with the $on - off$ signal and the drive signal's delays $\Delta t_{on-off}$ and $\Delta t_{off-on}$ .                                                                                                                                                                             | 94  |

| 5.5  | Compensated NLC control algorithm.                                                                                                                                                                                                                                                                                                                                             | 95  |

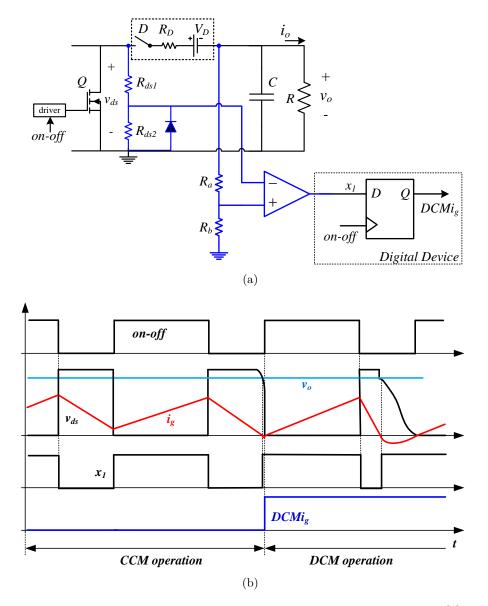

| 5.6  | DCM condition detection auxiliary circuit for the real input current $i_g$ . (a)<br>Hardware architecture. (b) Circuit waveforms                                                                                                                                                                                                                                               | 97  |

| 5.7  | DCM condition digital detection for the rebuilt input current $i_{reb}$ . Left: digital signals and, right: hardware architecture in the digital device.                                                                                                                                                                                                                       | 98  |

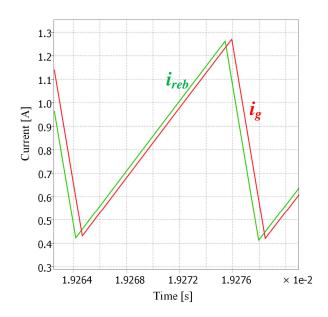

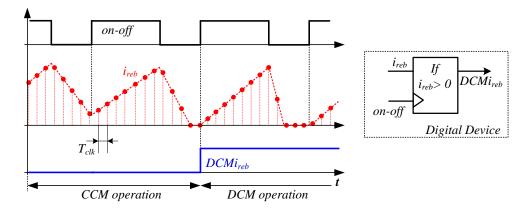

| 5.8  | Left: Current estimation error generated by $+ 5$ ns (with $T_{clk} = 10$ ns) of time<br>error compensation (in blue) and due to a $qv_{dig}$ value that cause the same<br>estimation error at the end of the half line period (in red). In magenta is<br>plotted the difference between the two current estimation errors. Right: $i_{reb}$<br>and $i_g$ current in this case | 99  |

| 5.9  | Minimum current estimation error due to the resolution of $\pm 0.5 LSB$ in the digital control signal $v_{dig}$ .                                                                                                                                                                                                                                                              | 100 |

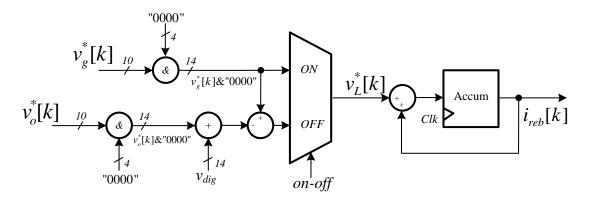

| 5.10 | Current estimator hardware implementation with higher resolution                                                                                                                                                                                                                                                                                                               | 100 |

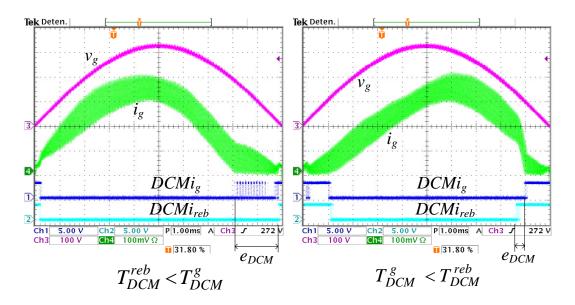

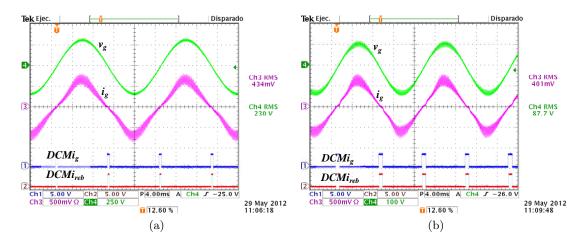

| 5.11 | Real waveforms. Input voltage $v_g$ , real input current $i_g$ , waveforms and digital signals $DCMi_g$ and $DCMi_{reb}$ for: Left: $e_{DCM} < 0$ , and then $i_{reb} > i_g$ . Right: $e_{DCM} > 0$ and $i_{reb} < i_g$ .                                                                                                                                                      | 102 |

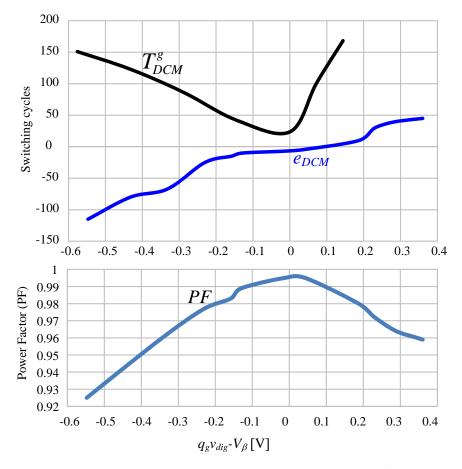

| 5.12 | Experimental results. Top: DCM time of the input current $T_{DCM}^g$ , and DCM time error $e_{DCM}$ vs $q_g v_{dig} - V_{\beta}$ . Bottom: PF vs $q_g v_{dig} - V_{\beta}$                                                                                                                                                                                                     | 102 |

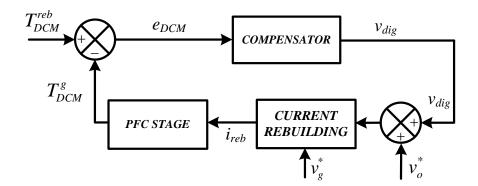

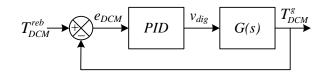

| 5.13 | Block diagram of the DCM times compensation controller.                                                                                                                                                                                                                                                                                                                        | 103 |

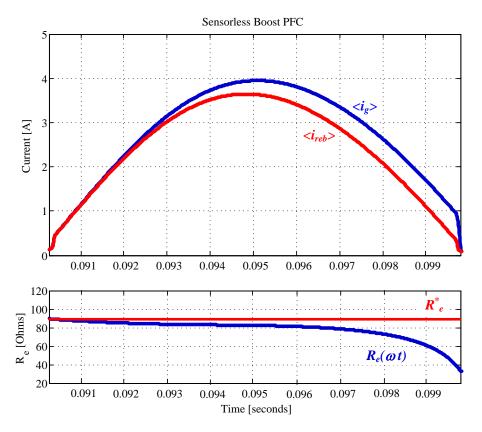

| 6.1  | Current waveforms with current error estimation (top) and emulated resis-<br>tances (real and digital) under this condition (bottom), over the half line cycle.                                                                                                                                                                                                                | 106 |

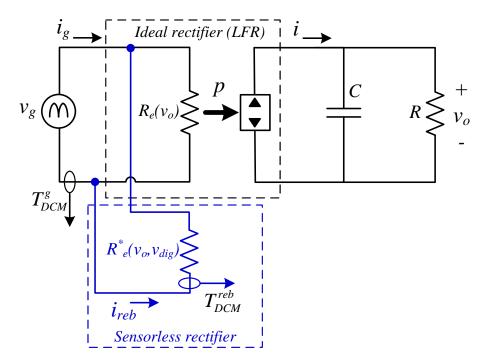

| 6.2  | Low frequency equivalent circuit of the sensorless PFC controller                                                                                                                                                                                                                                                                                                              | 108 |

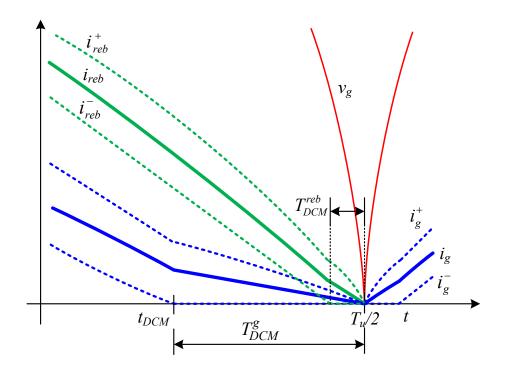

| 6.3  | Waveforms around the AC line zero-crossings.                                                                                                                                                                                                                                                                                                                                   | 109 |

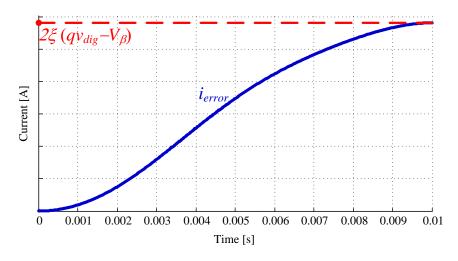

| 6.4  | Current error waveform $i_{error}$ , and its linear approximation                                                                                                                                                                                                                                                                                                              | 110 |

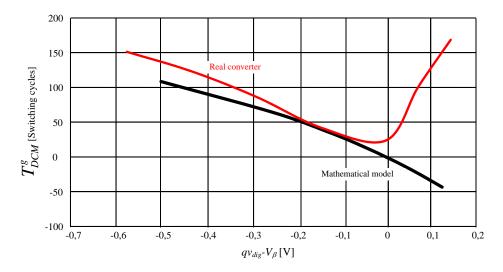

| 6.5  | Operation time in DCM of the real input current $T_{DCM}^g$ , in terms of switching periods, of the real converter and the mathematical model.                                                                                                                                                                                                                                 | 111 |

| 6.6  | Block diagram system representation.                                                                                                                                                                                                                                                                                                                                           | 112 |

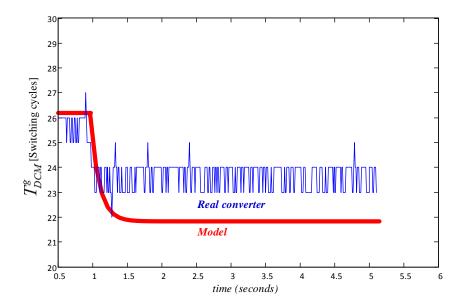

| 6.7  | Actual vs theoretical response time of the plant under a 2-bit $v_{dig}$ step-up.<br>$V_g = 230 V_{rms}, V_o = 400 V, f_{sw} = 96 kHz P_g = 460.9 W$ with $q = 435/(2^{14} - 1)$<br>V/bit                                                                                                                                                                                      | 113 |

|      |                                                                                                                                                                                                                                                                                                                                                                                |     |

| 7.1  | Grid voltage in the Power Electronics Laboratory, on March 13th of 2013                                                                                                                                                                                                                                                                                                                                                                                                                              | 116 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

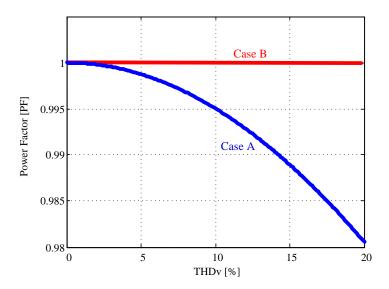

| 7.2  | Value of the power factor as function of the voltage harmonic distortion for Case A and Case B.                                                                                                                                                                                                                                                                                                                                                                                                      | 119 |

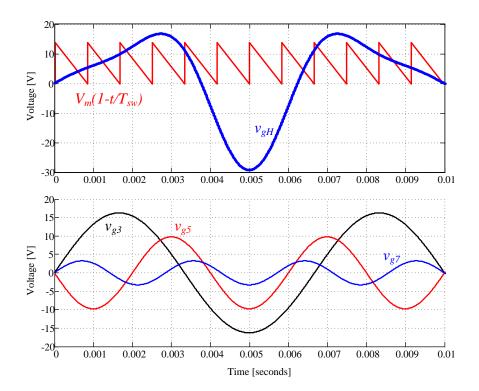

| 7.3  | Top: First term of the carrier signal (red) and the harmonic voltage (blue) waveforms. Bottom: Voltage harmonics in an example of input voltage with $THDv = 6\%$ .                                                                                                                                                                                                                                                                                                                                  | 121 |

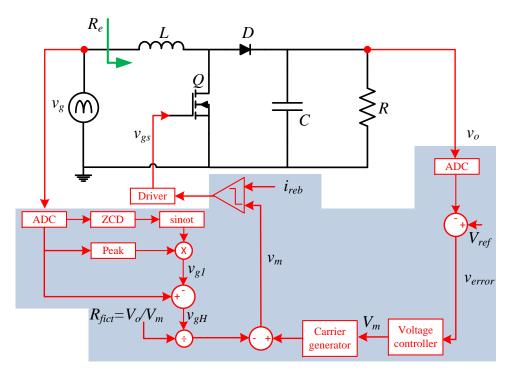

| 7.4  | Block diagram of the low THDi controller with the boost converter.                                                                                                                                                                                                                                                                                                                                                                                                                                   | 122 |

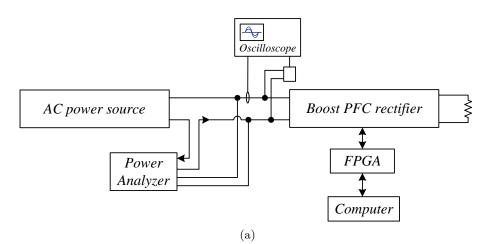

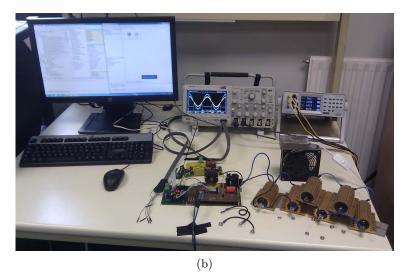

| 8.1  | (a) Block diagram and (b) picture of the of the Laboratory Test bench $\ . \ . \ .$                                                                                                                                                                                                                                                                                                                                                                                                                  | 126 |

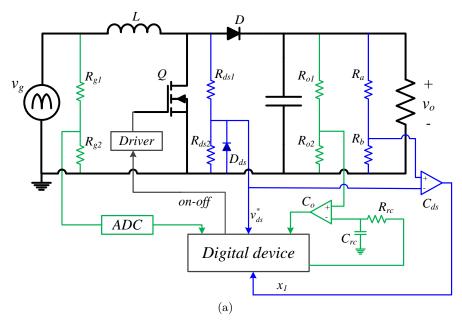

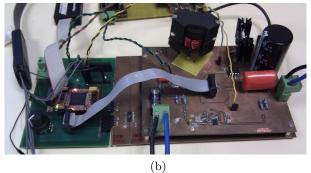

| 8.2  | (a) Circuit scheme of the proposed digital controller. (b) Picture of the boost converter prototype and the FPGA.                                                                                                                                                                                                                                                                                                                                                                                    | 127 |

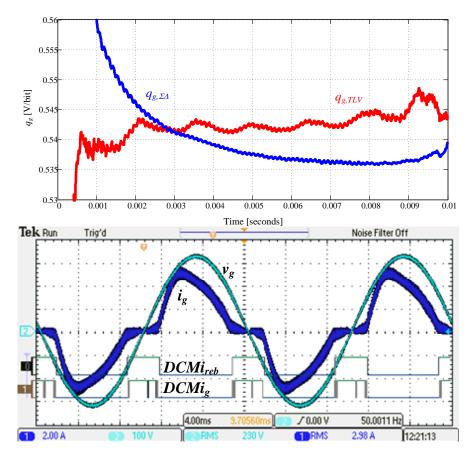

| 8.3  | Top: Measured value of $q_g$ over the half line cycle, for two different input voltages ADCs, under 230 $V_{rms}$ (50 Hz). In red it is plotted the measured value using the TLV1572 commercial ADC. In blue is plotted the $q_g$ value using the $\Sigma \triangle$ ADC used in the output voltage measurement, that leads to the $i_g$ current waveform at 648 W. Bottom: Experimental waveforms when the $\Sigma \triangle$ ADC is used in the output, and also in the input voltage measurement. | 128 |

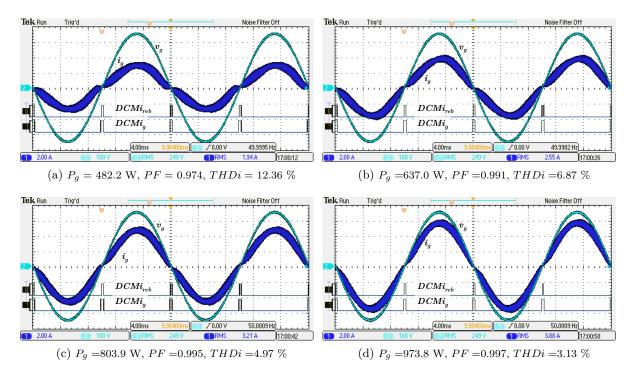

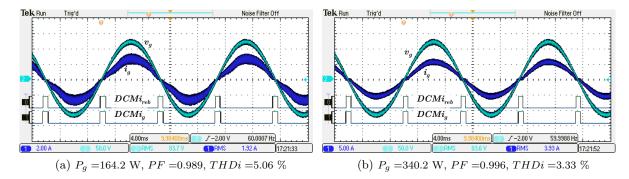

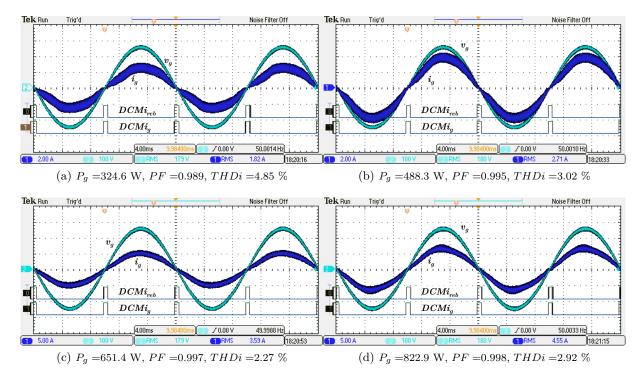

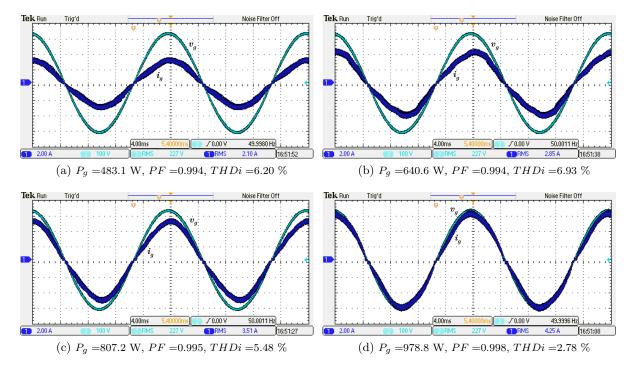

| 8.4  | Experimental results: input voltage $(v_g)$ and current $(i_g)$ along with the DCM signal of the rebuilt input current $(DCMi_{reb})$ and the real input current $(DCMi_g)$ . Waveforms under $V_g = 250 V_{rms}$ - 50 Hz, at 72 kHz switching frequency for different power levels.                                                                                                                                                                                                                 | 131 |

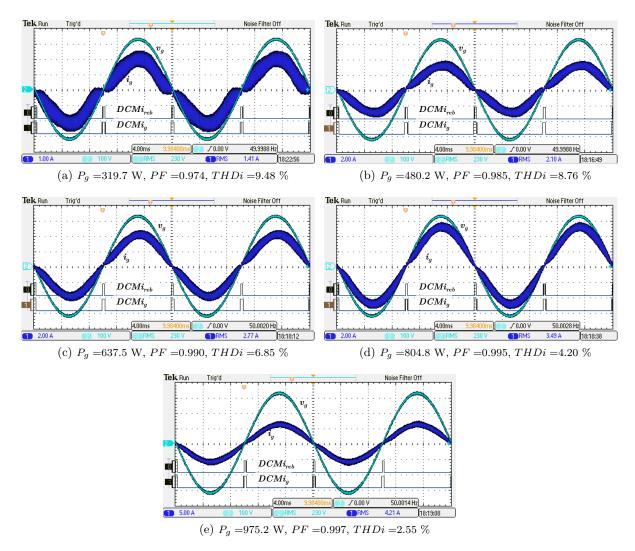

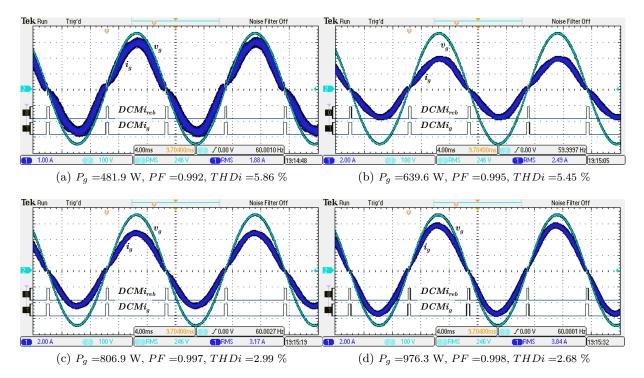

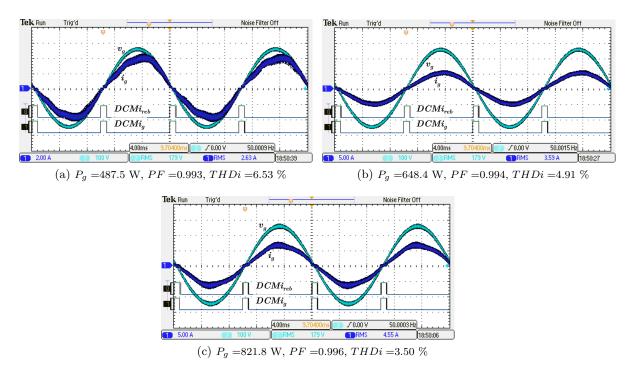

| 8.5  | Experimental results: input voltage $(v_g)$ and current $(i_g)$ along with the DCM signal of the rebuilt input current $(DCMi_{reb})$ and the real input current $(DCMi_g)$ . Waveforms under $V_g = 230 V_{rms} - 50$ Hz, at 72 kHz switching frequency for different power levels.                                                                                                                                                                                                                 | 132 |

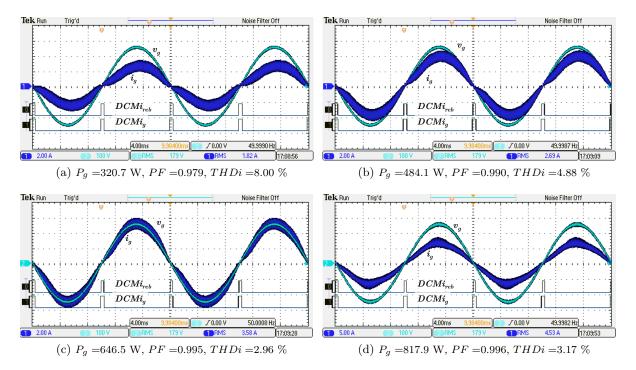

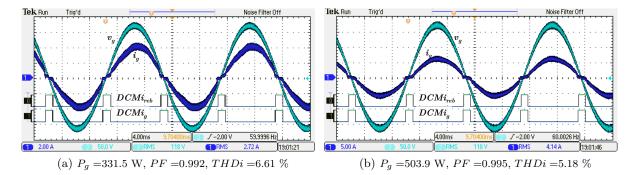

| 8.6  | Experimental results: input voltage $(v_g)$ and current $(i_g)$ along with the DCM signal of the rebuilt input current $(DCMi_{reb})$ and the real input current $(DCMi_g)$ . Waveforms under $V_g = 180 V_{rms} - 50$ Hz, at 72 kHz switching frequency for different power levels.                                                                                                                                                                                                                 | 133 |

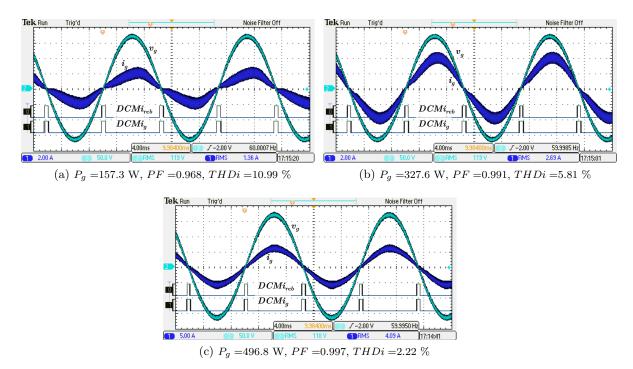

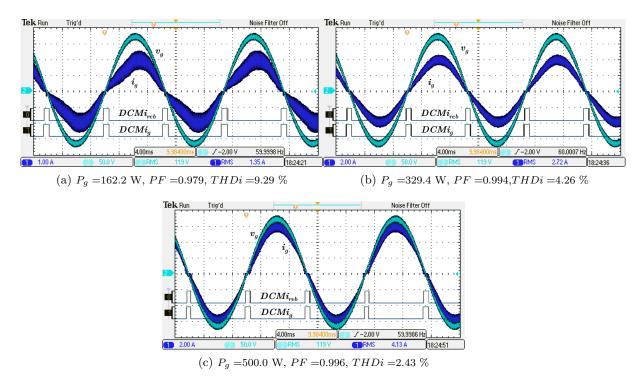

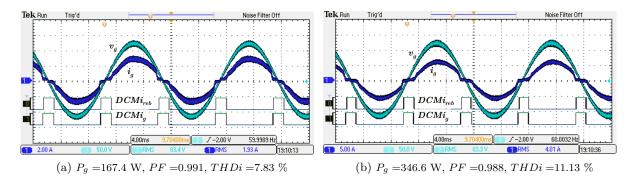

| 8.7  | Experimental results: input voltage $(v_g)$ and current $(i_g)$ along with the DCM signal of the rebuilt input current $(DCMi_{reb})$ and the real input current $(DCMi_g)$ . Waveforms under $V_g = 120 V_{rms} - 60$ Hz, at 72 kHz switching frequency for different power levels.                                                                                                                                                                                                                 | 133 |

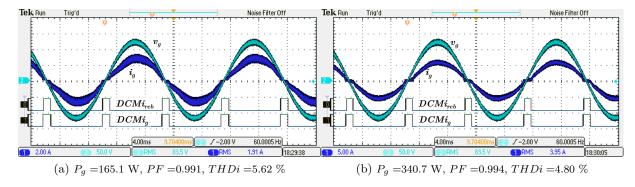

| 8.8  | Experimental results: input voltage $(v_g)$ and current $(i_g)$ along with the DCM signal of the rebuilt input current $(DCMi_{reb})$ and the real input current $(DCMi_g)$ . Waveforms under $V_g = 85 V_{rms}$ , at 72 kHz switching frequency for different power levels.                                                                                                                                                                                                                         | 134 |

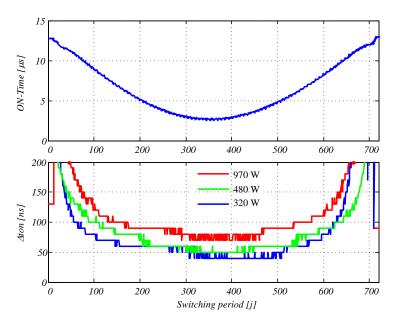

| 8.9  | Experimental results: Value of the duty cycle modification $(\Delta t_{on})$ due to the drive signal delays over the half line cycle.                                                                                                                                                                                                                                                                                                                                                                | 134 |

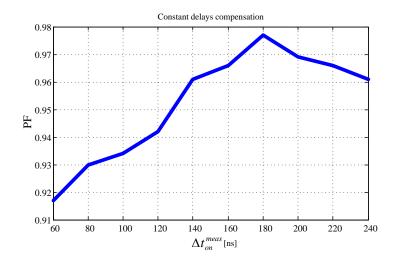

| 8.10 | Power factor value for different delays used in the feedforward compensation when they are considered constant over the half line cycle                                                                                                                                                                                                                                                                                                                                                              | 135 |

| 8.11 | Input current and voltage waveforms if the feedforward is done considering constant drive signal delays. (a) $\triangle t_{on}^{meas} = 100$ ns and (b) $\triangle t_{on}^{meas} = 220$ ns                                                                                                                                                                                                                                                                                                           | 135 |

| 8.12 | Experimental results for the DCM condition detection circuit for the real input current.                                                                                                                                                                                                                                                                                                                                                                                                             | 136 |

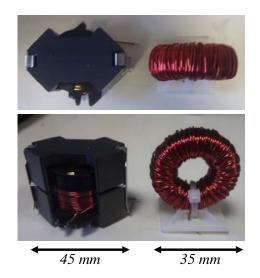

| 8.13 | Inductors used in the experimental results. Left: $L = 1  mH$ (RM12-3C90 core<br>with $R_L = 0.25 \Omega$ ). Right: $L_2 = 1.5  mH$ (soft saturation Kool m $\mu$ core with<br>$R_{L2} = 0.35 \Omega$ )                                                                                                                                                                                                                                                                                              | 137 |

| 8.14 | Experimental results: input voltage $(v_g)$ and current $(i_g)$ along with the DCM signal of the rebuilt input current $(DCMi_{reb})$ and the real input current $(DCMi_g)$ . $V_o = 400 V_{dc}$ and $L_2 = 1.5mH$ $(R_{L2} = 0.35 W)$ . (a): $V_g = 230 V_{rms}(50Hz)$ , $P_g = 970 W$ . (b): $V_g = 85 V_{rms}(60Hz)$ , $P_g = 320 W$                                                                                                                                                              | 137 |

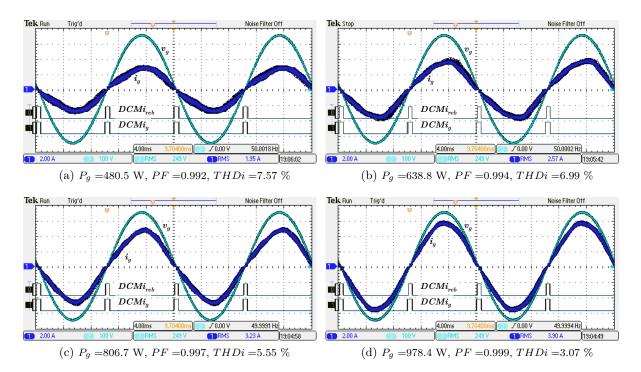

| 8.15 | Experimental results: input voltage $(v_g)$ and current $(i_g)$ along with the DCM signal of the rebuilt input current $(DCMi_{reb})$ and the real input current $(DCMi_g)$ . Waveforms under $V_g = 250 V_{rms} - 50$ Hz, at 96 kHz switching frequency for different power levels.  | 139   |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 8.16 | Experimental results: input voltage $(v_g)$ and current $(i_g)$ along with the DCM signal of the rebuilt input current $(DCMi_{reb})$ and the real input current $(DCMi_g)$ . Waveforms under $V_g = 230 V_{rms} - 50$ Hz, at 96 kHz switching frequency for different power levels.  | 139   |

| 8.17 | Experimental results: input voltage $(v_g)$ and current $(i_g)$ along with the DCM signal of the rebuilt input current $(DCMi_{reb})$ and the real input current $(DCMi_g)$ . Waveforms under $V_g = 180 V_{rms} - 50$ Hz, at 96 kHz switching frequency for different power levels.  | 140   |

| 8.18 | Experimental results: input voltage $(v_g)$ and current $(i_g)$ along with the DCM signal of the rebuilt input current $(DCMi_{reb})$ and the real input current $(DCMi_g)$ . Waveforms under $V_g = 120 V_{rms} - 60$ Hz, at 96 kHz switching frequency for different power levels.  | 140   |

| 8.19 | Experimental results: input voltage $(v_g)$ and current $(i_g)$ along with the DCM signal of the rebuilt input current $(DCMi_{reb})$ and the real input current $(DCMi_g)$ . Waveforms under $V_g = 85 V_{rms}$ , at 96 kHz switching frequency for different power levels.          | 141   |

| 8.20 | Experimental results: input voltage $(v_g)$ and current $(i_g)$ along with the DCM signal of the rebuilt input current $(DCMi_{reb})$ and the real input current $(DCMi_g)$ . Waveforms under $V_g = 250 V_{rms} - 50$ Hz, at 144 kHz switching frequency for different power levels. | 141   |

| 8.21 | Experimental results: input voltage $(v_g)$ and current $(i_g)$ along with the DCM signal of the rebuilt input current $(DCMi_{reb})$ and the real input current $(DCMi_g)$ . Waveforms under $V_g = 230 V_{rms} - 50$ Hz, at 144 kHz switching frequency for different power levels. | 143   |

| 8.22 | Experimental results: input voltage $(v_g)$ and current $(i_g)$ along with the DCM signal of the rebuilt input current $(DCMi_{reb})$ and the real input current $(DCMi_g)$ . Waveforms under $V_g = 180 V_{rms} - 50$ Hz, at 144 kHz switching frequency for different power levels. | 143   |

| 8.23 | Experimental results: input voltage $(v_g)$ and current $(i_g)$ along with the DCM signal of the rebuilt input current $(DCMi_{reb})$ and the real input current $(DCMi_g)$ . Waveforms under $V_g = 120 V_{rms} - 60$ Hz, at 144 kHz switching frequency for different power levels. | 144   |

| 8.24 | Experimental results: input voltage $(v_g)$ and current $(i_g)$ along with the DCM signal of the rebuilt input current $(DCMi_{reb})$ and the real input current $(DCMi_g)$ . Waveforms under $V_g = 85 V_{rms}$ , at 144 kHz switching frequency for different power levels.         | 144   |

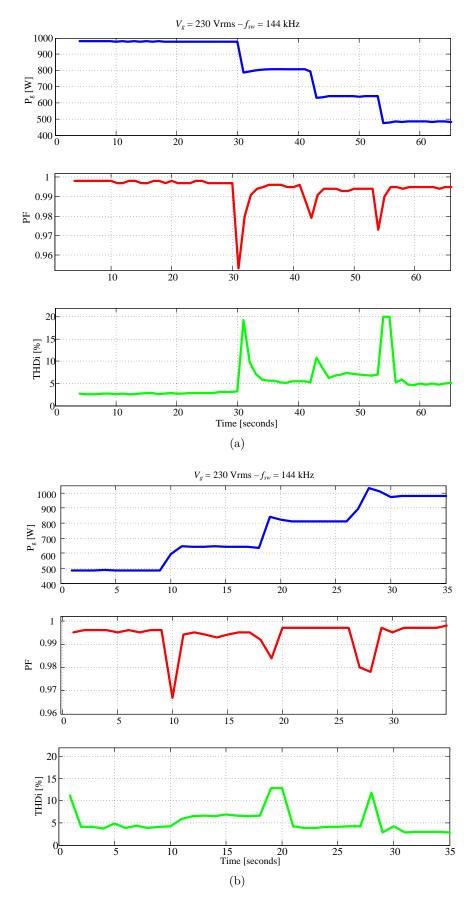

| 8.25 | Power factor and Total harmonic distortion value time evolution under different load steps. $V_o = 400 V_{dc} V_g = 230 V_{rms}(50Hz), f_{sw} = 144 kHz$ . (a) Load steps-down. (a) Load steps-up.                                                                                    | 147   |

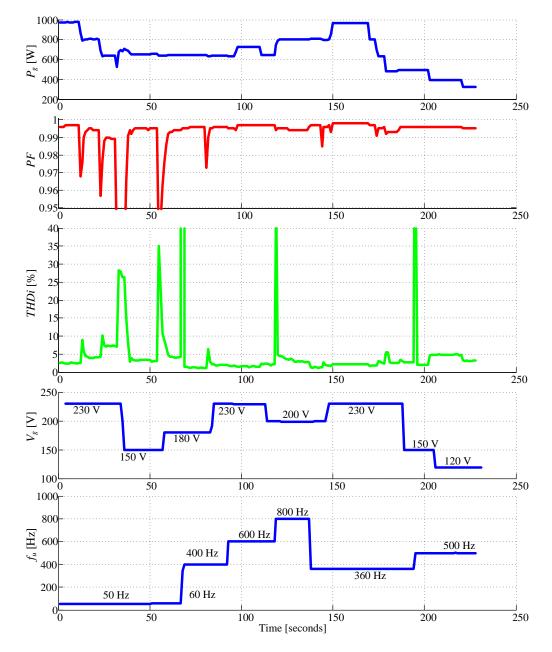

| 8.26 | Time evolution of the different electrical variables with $V_o = 400 V_{dc}$ , $f_{sw} = 72 kHz$ under different load, grid voltage and grid frequency arbitrary condition                                                                                                            | s.148 |

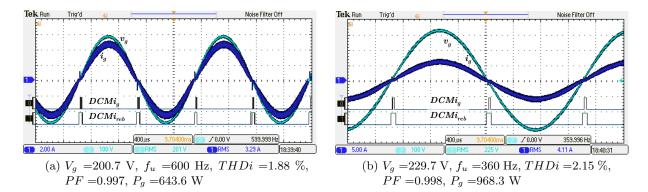

| 8.27 | Experimental results under high-frequency grids of two instants of the results presented in Fig. 8.26. Input voltage $(v_g)$ and current $(i_g)$ along with the DCM signal of the rebuilt input current $(DCMi_{reb})$ and the real input current $(DCMi_g)$ .                        | 149   |

| 8.28 | Experimental results under high-frequency grids of two instants of the results presented in Fig. 8.26.                                                                                                                                                                                | 149   |

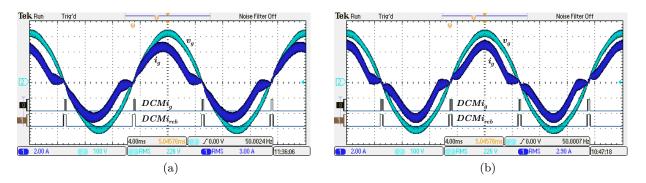

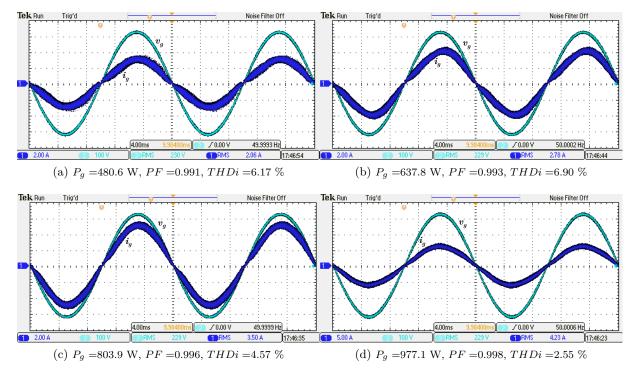

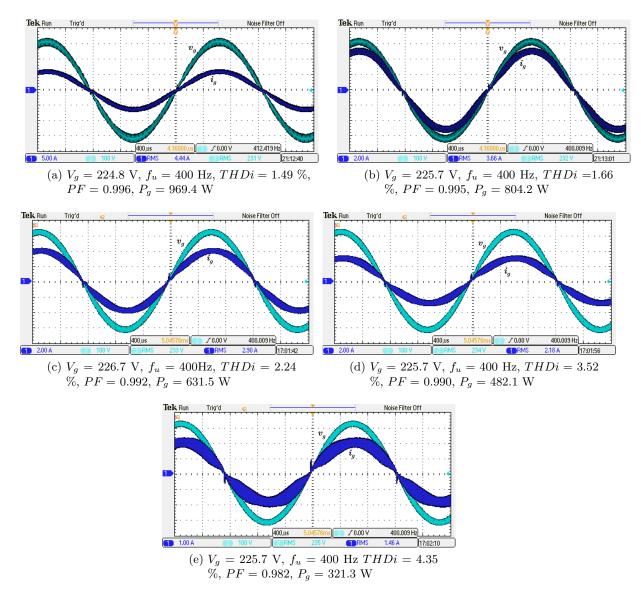

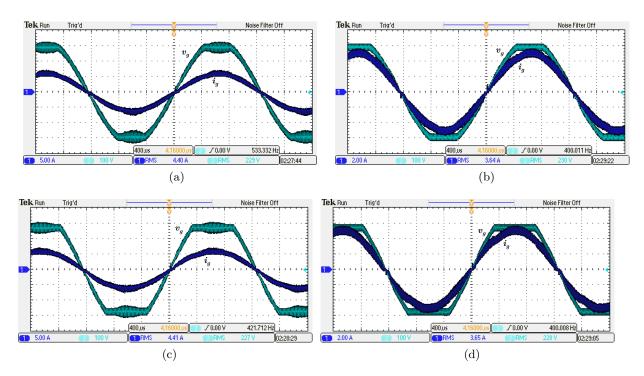

| 8.29 | Pure sinusoidal behavior under different power levels and input voltage distortions. Input voltage $(v_g)$ and current $(i_g)$ along with the DCM signal of the rebuilt input current $(DCMi_{reb})$ and the real input current $(DCMi_g)$ .<br>$V_g = 230 V$ , $f_{sw} = 96 \ kHz$ . With $THDv = 5 \ \%$ at (a) $P_g = 964.9 \ W$ and (b) $P_g = 799.5 \ W$ . With $THDv = 12 \ \%$ at (c) $P_g = 963.1 \ W$ and (d) $P_g = 800.4 \ W$ .                                           | 151        |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

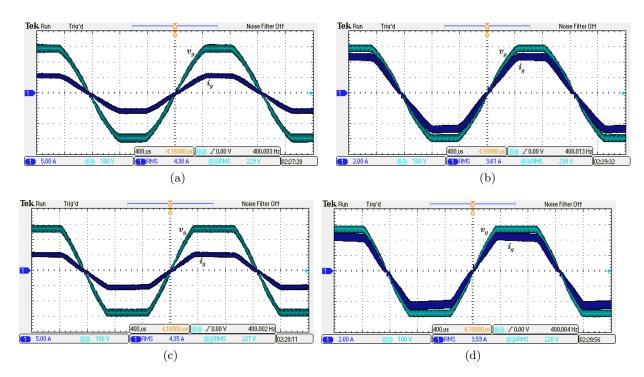

| 8.30 | Resistance behavior under different power levels and input voltage distortions.<br>Input voltage $(v_g)$ and current $(i_g)$ along with the DCM signal of the rebuilt<br>input current $(DCMi_{reb})$ and the real input current $(DCMi_g).V_g = 230 V$ ,<br>$f_{sw} = 96  kHz$ . With $THDv = 5 \%$ at (a) $P_g = 966.7$ W and (b) $P_g = 800.6$ W.<br>With $THDv = 12 \%$ at (c) $P_g = 965.1$ W and (d) $P_g = 800.9$ W                                                           | 151        |

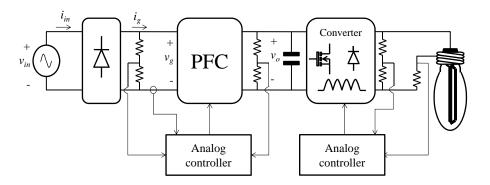

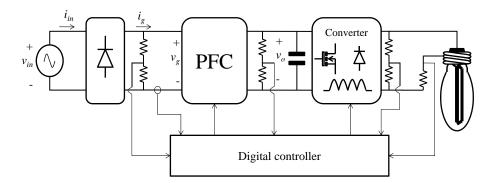

| 9.1  | Two power stages ballast circuit with a analog PFC and inverter controllers.                                                                                                                                                                                                                                                                                                                                                                                                         | 154        |

| 9.2  | Two power stages ballast circuit with digital controllers integrated in a single device.                                                                                                                                                                                                                                                                                                                                                                                             | 154        |

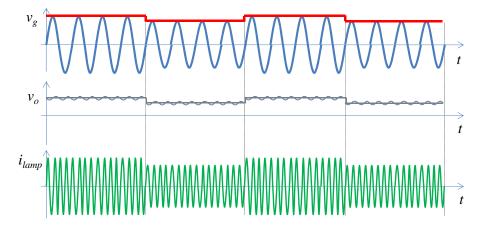

| 9.3  | Waveforms under voltage fluctuations situation: Utility voltage, $vg$ , PFC stage output voltage, $v_o$ , and lamp current, $i_{lamp}$ .                                                                                                                                                                                                                                                                                                                                             | 154<br>156 |

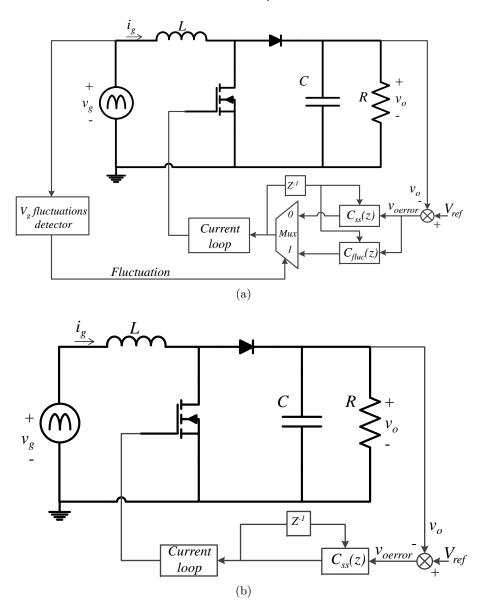

| 9.4  | PFC stage and digital controller implementation. (a) Traditional digital vol-<br>tage control loop. (b) Digital control loop proposed                                                                                                                                                                                                                                                                                                                                                | 156        |

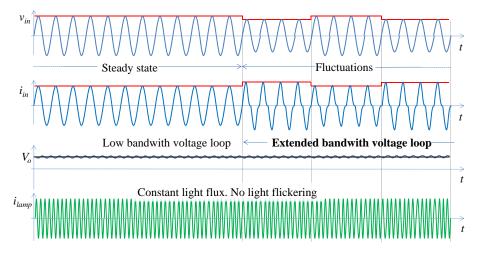

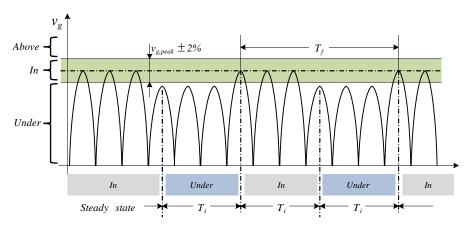

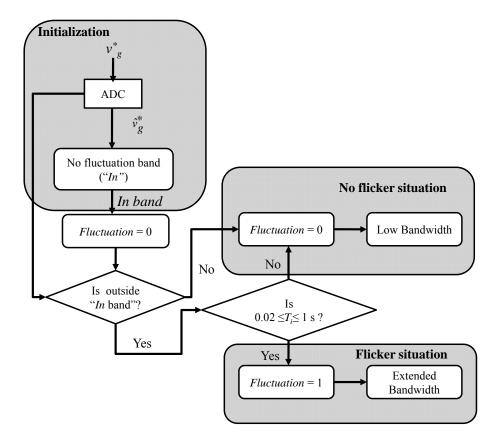

| 9.5  | Sketches of the utility voltage, utility current, dc voltage and lamp current changing the voltage loop: Low bandwidth loop during steady state and extended bandwidth loop under utility voltage fluctuation.                                                                                                                                                                                                                                                                       | 157        |

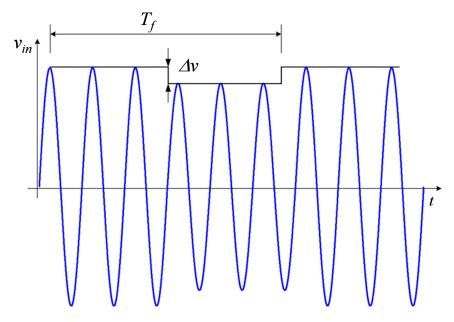

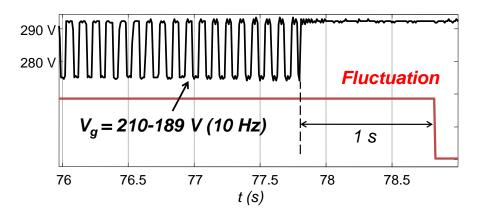

| 9.6  | Low frequency voltage fluctuation.                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 158        |

| 9.7  | Voltage range defined to detect the utility voltage fluctuations                                                                                                                                                                                                                                                                                                                                                                                                                     | 158        |

| 9.8  | Input voltage fluctuation detection algorithm flowchart.                                                                                                                                                                                                                                                                                                                                                                                                                             | 159        |

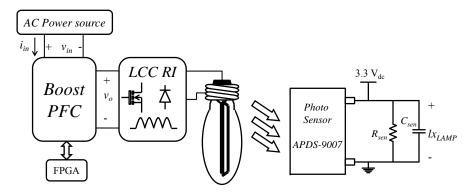

| 9.9  | Block diagram of the laboratory test setup.                                                                                                                                                                                                                                                                                                                                                                                                                                          | 160        |

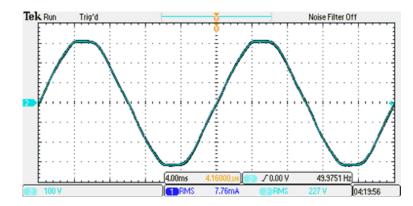

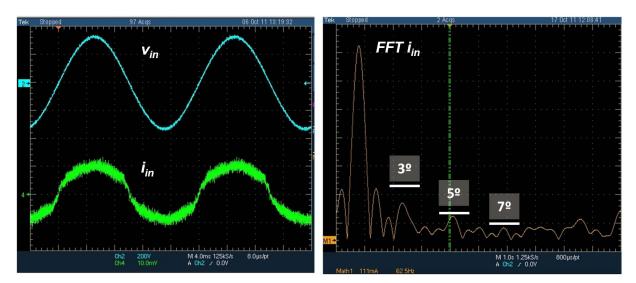

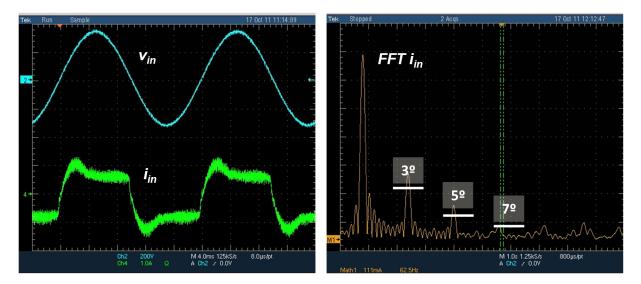

| 9.10 | PFC stage input waveforms and power. Low bandwidth outer loop. (a) Input voltage $v_{in}$ , and input current $i_{in}$ . $V_{in} = 230 V_{rms}$ , 50 Hz. Ch2 input voltage, 200 V/div, Ch4 input current, 10 mV/A and 10 mV/div. (b) Input current Fast Fourier Transform (FFT $i_{in}$ ) and IEC 61000-3-2 class C limits with $I_1 = 0.680$ A and $PF = 0.991$ . Math1. Vertical scale 111 mA/div, horizontal scale 62.5 Hz/div                                                    | 160        |

| 9.11 | PFC stage input waveforms and power. Wide bandwidth outer loop. (a)<br>Input voltage $v_{in}$ , and input current $i_{in}$ . $V_{in} = 230 V_{rms}$ , 50 Hz. Ch2 input<br>voltage, 200 V/div, Ch4 input current, 10 A/div. (b) Input current Fast<br>Fourier Transform (FFT $i_{in}$ ) and IEC 61000-3-2 class C limits with $I_1 = 0.680$<br>A and $PF = 0.91$ . Math1. Vertical scale 111 mA/div, horizontal scale 62.5<br>Hz/div.                                                 | 161        |

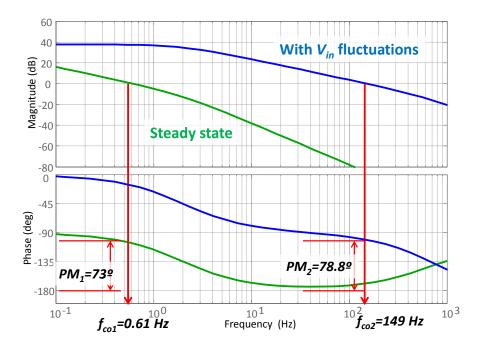

| 9.12 | Bode plots for the different voltage loops. Green: Bode plot for steady-state conditions with reduced bandwidth. Blue: Bode plot for transient state during input voltage fluctuation with wide bandwidth.                                                                                                                                                                                                                                                                           | 162        |

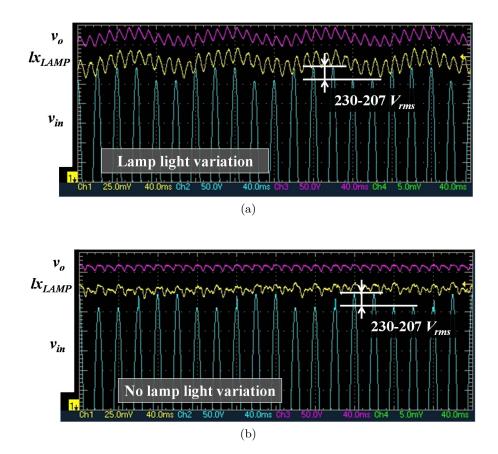

| 9.13 | The PFC stage output voltage $(v_o)$ , the lamp light lux level measured by the photo sensor $(lx_{LAMP})$ and input voltage $(v_{in})$ under 10% $V_{inRMS}$ and 10 Hz fluctuation. $V_{in} = 230-207 V_{rms}$ , 50Hz, $V_o = 420$ Vdc, $P_g = 150$ W and C=68 $\mu$ F output capacitor. (a) With a reduced voltage loop bandwidth and (b) With a wide voltage loop bandwidth. Ch2 input voltage, 50 V/div, Ch1 lamp light flux. Ch3 output voltage 50 V/div. Time scale: 40 ms/div | 163        |

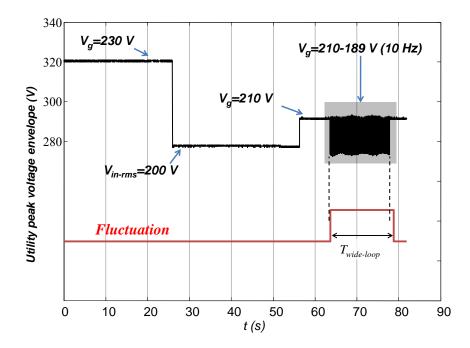

| 9.14 | Behavior of the input voltage fluctuation algorithm under different utility vol-<br>tage conditions. Utility peak voltage envelope (blue) and "Fluctuation" signal<br>that indicates if a fluctuation is detected (red).                                                                                                                                                                                                                                                             | 164        |

| 9.15 | Time necessary by the algorithm to determinate the steady state condition at the end of the utility voltage fluctuation.                                                                                                                                                                                                                                                                                                                                                             | 164        |

| 9.16 | Lucalox 150 W HPS lamp used to verify the proposal                                                                                       | 164 |

|------|------------------------------------------------------------------------------------------------------------------------------------------|-----|

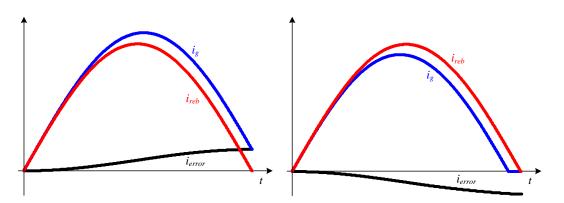

| A.1  | System waveforms for a given $I_{reb}$ and $qv_{dig} - V_{\beta}$ values. Left: $qv_{dig} > V_{\beta}$ and right: $qv_{dig} < V_{\beta}$ | 192 |

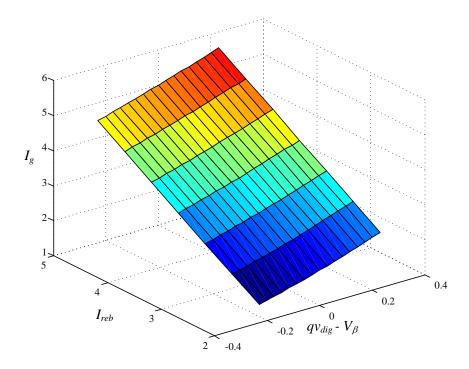

| A.2  | Surface of $I_g$ values obtained for different combinations of given $I_{reb}$ and $qv_{dig} - V_\beta$ values.                          |     |

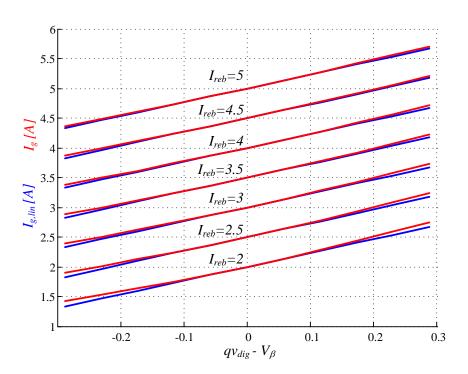

| A.3  | Comparison of $I_g$ values obtained by (A.7) (represented in red), and by the                                                            |     |

linear approximation defined by (A.9), labeled as  $I_{g,lin}$  and plotted in blue. 194

# **List of Tables**

| 2.1 | IEC 61000-3-2 harmonic current limits                                                                                                                                                                                                                          | 21  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.2 | IEEE Std 519 Maximum odd harmonic current limits for general distribution systems, 120 V to 69 kV                                                                                                                                                              | 21  |

| 2.3 | CCM-DCM mode boundaries for the Boost converter.                                                                                                                                                                                                               | 31  |

| 2.4 | Theoretical power losses for different switching frequencies. Efficiencies with $(\eta)$ and without $(\eta_{ssles})$ current sensor. And ratio between the current sensor losses $(P_S)$ , the conduction losses $(P_{cond})$ and total losses $(P_{loss})$ . | 44  |

| 3.1 | (a) List of correspondence between of the analog variables and the digital. (b) Expressions that define the variation of the real and rebuilt input current in a switching period                                                                              | 60  |

| 7.1 | DO-160 Harmonic Current Limits                                                                                                                                                                                                                                 | 115 |

| 7.2 | Voltage harmonics in the line voltage shown in Fig. 7.1                                                                                                                                                                                                        | 117 |

| 8.1 | Parameters of the components used in the Boost prototype                                                                                                                                                                                                       | 126 |

| 8.2 | Experimental results in steady state with a switching frequency $f_{sw} = 72$ kHz                                                                                                                                                                              | 130 |

| 8.3 | Power Factor and $THDi$ values under different conditions                                                                                                                                                                                                      | 138 |

| 8.4 | Experimental results with a switching frequency of 96 kHz                                                                                                                                                                                                      | 142 |

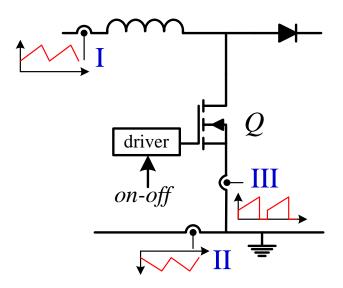

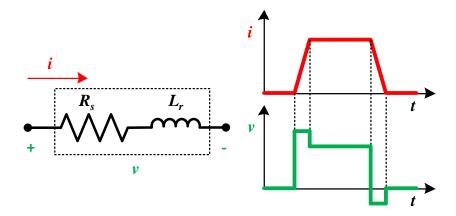

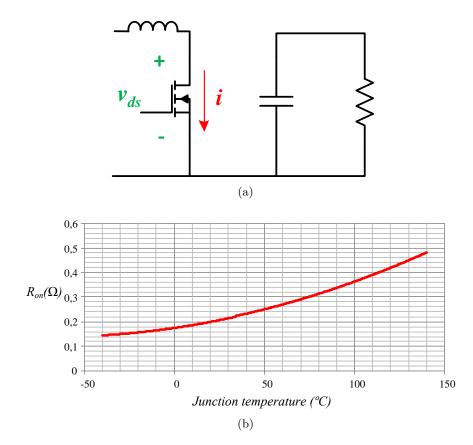

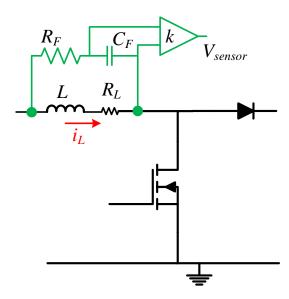

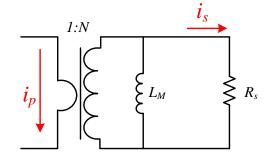

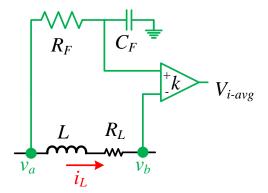

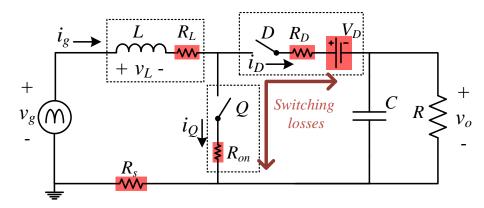

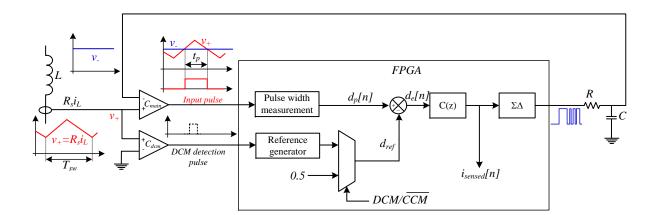

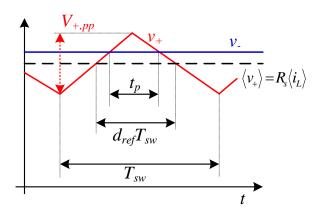

| 8.5 | Experimental results at 144 kHz of switching frequency                                                                                                                                                                                                         | 145 |