## ESCUELA TÉCNICA SUPERIOR DE INGENIEROS INDUSTRIALES Y DE TELECOMUNICACIÓN

#### UNIVERSIDAD DE CANTABRIA

### Proyecto Fin de Carrera

## CONVERTIDOR RESONANTE CLASE E<sup>2</sup> EN RF SOBRE TECNOLOGÍA GAN HEMT

(RF Clase E<sup>2</sup> Resonant Converter on GaN HEMTs)

Para acceder al Titulo de

INGENIERO DE TELECOMUNICACIÓN

Autor: Patricia Ma Martínez Mediavilla

**Octubre - 2013**

#### INGENIERÍA DE TELECOMUNICACIÓN

#### CALIFICACIÓN DEL PROYECTO FIN DE CARRERA

Realizado por: Patricia Mª Martínez Mediavilla Director del PFC: José Ángel García García

Título: "Convertidor Resonante Clase E<sup>2</sup> en RF sobre tecnología GaN

HEMT"

Title: "RF Clase Resonant Converter E2 using GaN HEMTs"

Presentado a examen el día: de Octubre de 2013

para acceder al Título de

#### INGENIERO DE TELECOMUNICACIÓN

# Composición del Tribunal: Presidente (Apellidos, Nombre): Fernández Ibáñez, Tomás Secretario (Apellidos, Nombre): García García, José Ángel Vocal (Apellidos, Nombre): Sancho Lucio, Sergio

Este Tribunal ha resuelto otorgar la calificación de: .....

Fdo.: El Presidente Fdo.: El Secretario

Fdo.: El Vocal Fdo.: El Director del PFC

(sólo si es distinto del Secretario)

V° B° del Subdirector Proyecto Fin de Carrera N°

(a asignar por Secretaría)

### **Agradecimientos**

Probablemente esta es una de las partes más complicadas del proyecto, ya que es difícil expresar en unas pocas líneas el trabajo de tantos años y agradecérselo a todos aquellos que han aportado algo en este largo camino.

En primer lugar, y como no podía ser de otra manera, me gustaría darles las gracias a mis padres por su dedicación, su apoyo constante y sus consejos. Y a mi hermana, por ser mi modelo a seguir y por la paciencia que tiene conmigo. Así como al resto de mi familia, en especial a mi abuela y a mis tíos, Ángel y Blanca, por sus llamadas y sus ánimos.

Otro apoyo muy importante ha sido el que he recibido y recibo de Edu, siempre dispuesto a ayudarme en todo y al que le debo mucho.

También me gustaría mencionar a mis compañeros de teleco, quienes han hecho más llevaderas las horas de estudio y los periodos de exámenes; y que han acabado convirtiéndose en amigos. Pablo, Sergio y Claudia. Y Dani, Epi, Miguel, Jorge y Menezo.

Por último, y no menos importantes, agradecerles a todas las personas que han hecho posible este proyecto. A José Ángel, mi tutor, por permitirme "cacharrear" y entrar en un laboratorio real de medias, por todas las horas que ha dedicado a este proyecto, a pesar de tener que hacer siempre mil cosas, y por todo lo que he aprendido. A Nieves, por su ayuda tanto en el laboratorio como en la parte del diseño, siempre respondiendo a todas las preguntas que la hacía. A Leysi y a Reinel, que aunque el tiempo que estuvieron por el laboratorio fue corto, se les agradece porque no formaba parte de su trabajo. A Sandra, ya que sin ella este proyecto se hubiera quedado en la parte de diseño y por la paciencia que ha tenido cada vez que la llevábamos algún problema nuevo. Y al Ministerio de Economía y Competitividad, por financiar este proyecto, TEC2011-29126-C03-01, que se encuentra dentro del Plan Nacional de I+D+i.

Me ha quedado mucha gente en el tintero, porque como ya dije antes, es complicado mencionar a todas aquellas personas que me han aportado algo de una forma u otra. Muchas gracias a todos.

## Índice de contenidos

| Sección I. Introducción                                                         | 1    |

|---------------------------------------------------------------------------------|------|

| 1. Escenario                                                                    | 1    |

| 2. Objetivos                                                                    | 2    |

| 3. Estructura de la memoria                                                     | 2    |

| 4. Referencias                                                                  | 3    |

| Sección II. Arquitecturas de Transmisión de Alta Eficiencia                     | 4    |

| 1. Limitaciones transmisores inalámbricos actuales, Transmisor Cartesiano o I/Q | 4    |

| 2. Soluciones para el modulado de envolvente                                    | 5    |

| 2.1. EER (Envelope Elimination and Restoration) / Transmisor Polar              | 5    |

| 2.1.1. Transmisor EER original:                                                 | 5    |

| 2.1.2. Transmisor Polar:                                                        | 6    |

| 2.2. ET (Envelope Tracking) seguimiento de la envolvente                        | 8    |

| 3. Técnicas para mejorar la eficiencia del transmisor polar                     | 9    |

| 3.1. Uso de un amplificador de envolvente de alta eficiencia                    | 9    |

| 3.2. Uso de transistores GaN HEMT                                               | . 11 |

| 4. Técnicas de modulación de la impedancia de carga                             | . 12 |

| 5. Referencias                                                                  | . 14 |

| Sección III. Amplificadores de Potencia                                         | . 15 |

| Características de los amplificadores de potencia                               | . 15 |

| 1.1. Parámetros significativos del amplificador de potencia                     | . 16 |

| 1.1.1. Eficiencia                                                               | . 16 |

| 1.1.2. Linealidad                                                               | . 17 |

| 1.2. Comportamiento no lineal del amplificador                                  | . 18 |

| 2. Clases de amplificadores de potencia                                         | . 19 |

| 3. Amplificador clase E                                                         | . 21 |

| 2.1. Análisis del amplificador de potencia clase E                              | . 22 |

| 4. Referencias                                                                  | . 30 |

| Sección IV. Diseño de un Convertidor Clase E <sup>2</sup>                       | .31  |

| 1. Introducción teórica del convertidor resonante de potencia                   | .31  |

| 1.1. Elección de una topología para el convertidor         | 32 |

|------------------------------------------------------------|----|

| 1.1.1. Inversor clase E                                    | 32 |

| 1.1.2. Rectificador clase E                                | 33 |

| 1.1.3. Convertidor resonante clase E <sup>2</sup>          | 33 |

| 2. Diseño de un convertidor DC/DC                          | 34 |

| 2.1. Caracterización del transistor                        | 35 |

| 2.2. Diseño de la red de interconexión [6]                 | 38 |

| 2.3. Diseño de la red de polarización                      | 39 |

| 2.3.1. Polarización del drenador                           | 39 |

| 2.3.1. Polarización de la puerta                           | 41 |

| 2.4. Diseño de la red de adaptación de entrada             | 41 |

| 3. Referencias                                             | 42 |

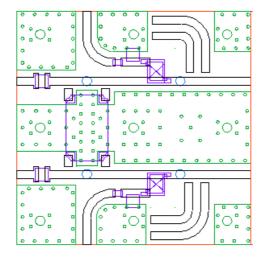

| Sección V. Implementación y Medida                         | 44 |

| 1. Introducción                                            | 44 |

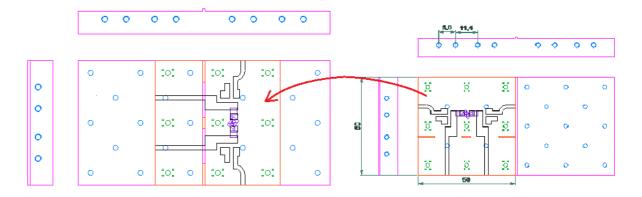

| 1.1. Layout del sistema                                    | 44 |

| 1.2. Placas, bases y componentes                           | 44 |

| 2. Red de interconexión                                    | 44 |

| 2.1. Layout del sistema                                    | 44 |

| 2.2. Medidas realizadas en el laboratorio                  | 46 |

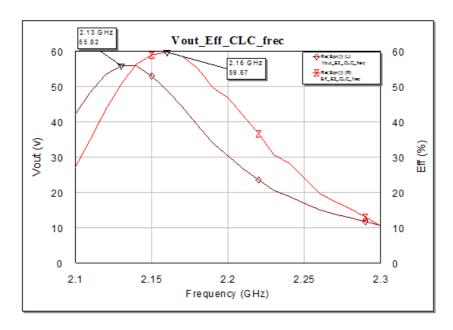

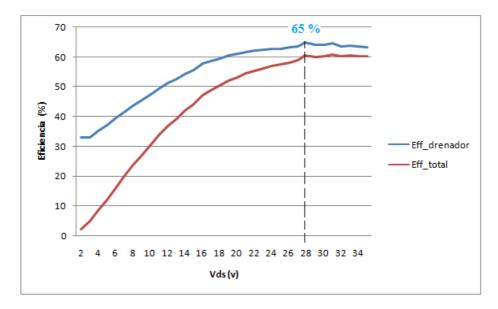

| 2.3. Comportamiento del convertidor                        | 47 |

| 2.3.1. Eficiencia y tensión de salida                      | 47 |

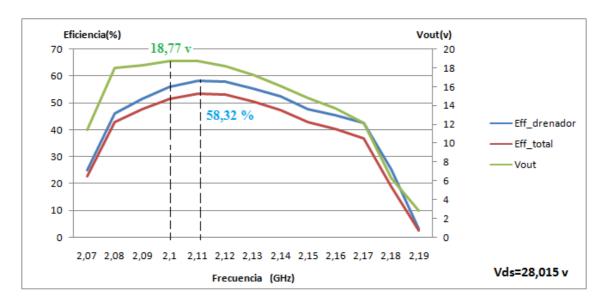

| 2.3.2. Modulación en frecuencia                            | 48 |

| 3. Red de polarización                                     | 49 |

| 3.1. Layout del sistema                                    | 49 |

| 3.2. Medidas realizadas en el laboratorio                  | 49 |

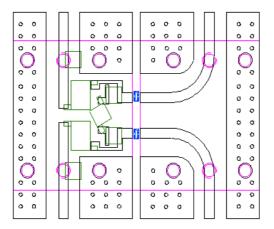

| 4. Circuito y montaje final del convertidor E <sup>2</sup> | 51 |

| 4.1. Layout del sistema                                    | 51 |

| 4.2. Montaje final de todos los componentes                | 52 |

| 4.3. Medidas realizadas en el laboratorio                  | 53 |

| 4.3.1. Eficiencia a la frecuencia de trabajo               | 54 |

| 4.3.2. Respuesta en frecuencia                             | 55 |

| 5. Referencias                                             | 57 |

| Sección VI. Conclusiones y Líneas Futuras                  | 58 |

| 1. Conclusiones   | 58 |

|-------------------|----|

| 2. Líneas futuras | 58 |

| 3. Referencias    | 59 |

### Introducción

#### 1. Escenario

El desarrollo de los sistemas inalámbricos en las últimas décadas se puede caracterizar por la evolución de la transmisión fundamentada en la voz de los años 70 a la transmisión de datos de hoy en día. Se espera que este tráfico medio de datos continúe creciendo de forma exponencial, lo que exigirá sistemas más eficientes y con una respuesta transitoria más rápida. La búsqueda de mayores velocidades de tasa de datos está impulsando la integración de formatos de modulación digital robustos multinivel o multiportadora (WCDMA, LTE) en el sistema global para las comunicaciones móviles, gracias al uso de técnicas como el seguimiento de la envolvente "Envelope Tracking" (ET) o eliminación y restauración de la envolvente "Envelope Elimination and Restoration" (EER) [1]. Del mismo modo, la potencia de las redes inalámbricas de área local (WLAN), con el despliegue de los servicios 802.11a/b/g y los desarrollos de una cuarta generación (4G) de tecnología móvil y WiMAX, prometen ofrecer capacidad adicional. Está claro que el futuro de los dispositivos inalámbricos necesitará soportar un incremento del número de aplicaciones.

Una parte fundamental del dispositivo inalámbrico es el transmisor. Los transmisores inalámbricos suelen emplear arquitecturas como la cartesiana o IQ, que exigen el uso de amplificadores lineales de RF. Habitualmente se utilizan amplificadores clase A, pero la alta relación entre la potencia pico a potencia promedio (PAPR) de los formatos de modulación mencionados, requieren una amplificación mucho más eficiente que la que se puede obtener con estos amplificadores lineales.

Por otro lado, la eficiencia en potencia es un factor fundamental a tener en cuenta en transmisiones inalámbricas, maximizar la autonomía de los terminales de usuario y reducir los gastos relacionados al elevado consumo de potencia de las estaciones base, que conlleva, no sólo razones económicas, sino también medioambientales, a la necesidad de utilizar una arquitectura eficiente como es la del transmisor polar evitando el uso del amplificador lineal poco eficiente [2] [3]. Tan importante es la eficiencia en una estación base que aproximadamente la mitad del gasto de energía correspondiente al transmisor (alrededor del 25% del total), se debe a la mala eficiencia del amplificador de potencia.

La necesidad de cumplir con las restricciones planteadas, nos lleva a la búsqueda de sistemas de transmisión que consigan un buen compromiso entre la linealidad y la eficiencia. El transmisor polar es el que mejor se ajusta a esta relación, cumpliendo los criterios de amplificación y tasas de transmisión de información requeridas en transmisión inalámbrica.

#### 2. Objetivos

El objetivo de este proyecto es el diseño e implementación de un convertidor resonante de potencia de RF sobre tecnología de alta eficiencia GaN HEMT en la banda de 2.14 GHz. La elección de esta frecuencia fue motivada por coincidir con una de las bandas de comunicaciones móviles y por ser más del doble de la frecuencia que se había probado anteriormente en el departamento. Con ello, se podría probar la capacidad del proceso con longitud de puerta igual a 0,25µm del fabricante seleccionado.

Dada la importancia de la eficiencia en potencia en transmisión inalámbrica, se realizan cada vez más nuevos diseños que permiten obtener valores elevados de eficiencia, utilizando transistores de alta eficiencia. Siguiendo esta línea, se pretende implementar un convertidor DC/DC que abarque el proceso de inversión de la señal de DC y la posterior rectificación de la señal de RF en un mismo sistema, de forma que obtengamos valores más altos que los conseguidos con implementaciones separadas del inversor y rectificador.

Para lograr el propósito de alta eficiencia, se usarán transistores de Nitruro de Galio (GaN HEMT) de Cree Inc., compañía líder del sector. [3]

También, se estudiarán las características de los dispositivos GaN HEMT y su uso en topologías clase E, centrándonos en el diseño del convertidor que aproveche dichas características y pueda ser optimizado para obtener buenos resultados de eficiencia.

Por último, se realizarán medidas sobre dicha implementación que permita conocer su comportamiento, como la eficiencia a la frecuencia de trabajo y la respuesta en frecuencia.

#### 3. Estructura de la memoria

Esta memoria se encuentra estructurada en secciones, cada una de ellas la presentaremos a continuación a modo de resumen:

- Sección I: se presenta el proyecto fin de carrera, para ello se hace una breve introducción sobre los temas a tratar en el mismo y los objetivos que pretendemos lograr una vez finalizado.

- Sección II: se realiza un estudio de las arquitecturas de transmisión de alta eficiencia del transmisor cartesiano y polar. Así como de las soluciones para el modulador de envolvente, ET y EER.

- Sección III: se describen las características de los amplificadores de potencia, centrándose en las topología de clase E, y de los transistores GaN HEMT.

- Sección IV: se presentan las características del convertidor DC/DC así como su diseño. Se explicarán detalladamente la caracterización de los transistores, las redes de polarización y adaptación utilizadas, y los demás componentes necesarios.

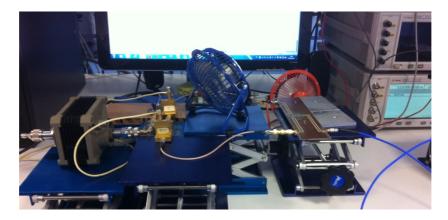

- Sección V: se incluye el layout de cada diseño y las simulaciones realizadas para cada uno. Además se expone la implementación final del convertidor DC/DC y los resultados obtenidos en el laboratorio para las diferentes medidas.

- Sección VI: para concluir se incluirán una reflexión sobre los resultados obtenidos durante el proyecto y se enfocarán las líneas de investigación futuras.

#### 4. Referencias

- [1] J. A. García, J. de Mingo, G. Montoro, L. Cabria, R. Marante, P. García, C. Sánchez, E. Beltrán, P.L. Gilabert, "Arquitecturas de transmisión inalámbrica de alta eficiencia"

- [2] J. A. García, C. Fager, A. Zhu, J. C. Pedro, P. Cabral, P. Colantonio, "Emerging Wireless Transmitter Architectures", TARGET-2007-11-27-WP232-D-D.2-3.0, Noviembre 2007

- [3] L.R. Kahn, "Single-Sideband Transmission by Envelope Elimination and Restoration", Proc. IRE, vol. 40, no. 7, pp. 803-806, Julio 1952.

- [4] Yang Gao, Alex Q. Huang, "Feasibility Study of AlGaN/GaN HEMT for Multimegahertz DC/DC Converter Applications", IPEMC 2006

## Sección II

## Arquitecturas de Transmisión de Alta Eficiencia

### 1. Limitaciones transmisores inalámbricos actuales, Transmisor Cartesiano o I/Q

Los problemas actuales para la consecución de valores elevados de eficiencia en la transmisión de formatos de modulación multinivel o multiportadora, vienen asociados básicamente al principio de funcionamiento que rige la propia arquitectura vigente: el transmisor Cartesiano o transmisor I/Q.

En los sistemas de radiocomunicación se debe transmitir a frecuencias muy determinadas, debido a este requerimiento se emplea la transmisión paso banda.

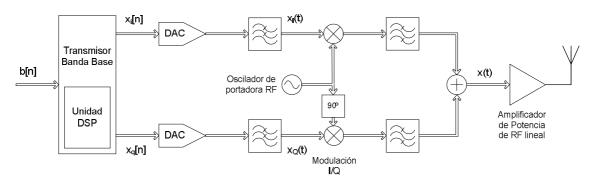

Una representación banda base de las señales paso banda es la cartesiana, componentes en fase y cuadratura. Esta arquitectura se utiliza tradicionalmente para transmitir en radiofrecuencia. En este esquema de transmisión, que se muestra en la Figura 1, las componentes en fase y cuadratura de la señal a transmitir modulan respectivamente a las componentes en fase y cuadratura de la señal portadora. Después, las dos señales moduladas se combinan formando la señal a transmitir, que es procesada por un amplificador de potencia de RF teóricamente lineal, y poco eficiente, y enviada por la antena.

Figura 1. Arquitectura del transmisor cartesiano

La señal de salida, antes del amplificador de potencia, se representa en función de sus componentes en fase y en cuadratura como se indica en la siguiente expresión:

$$x(t) = x_i(t) \cdot \cos(w_c \cdot t) - x_q(t) \cdot \sin(w_c \cdot t) \tag{1}$$

Sección II

Esta arquitectura no satisface el compromiso de linealidad con alta eficiencia de potencia tan necesario en los sistemas inalámbricos actuales, para alcanzar este objetivo se pueden utilizar arquitecturas alternativas, como la del transmisor polar.

#### 2. Soluciones para el modulador de envolvente

#### 2.1. EER (Envelope Elimination and Restoration) / Transmisor Polar

#### 2.1.1. Transmisor EER original:

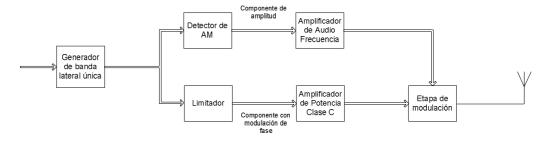

En 1952 Kahn [1] propone la arquitectura de un transmisor capaz de eliminar y restaurar la envolvente de una señal de entrada, su esquema se puede ver en la Figura 2.

La rama superior se encarga de detectar la envolvente, mediante un detector de AM, obteniendo la componente de amplitud y posteriormente de amplificarla, con un amplificador de potencia de audio frecuencia. Esta última componente modula de nuevo a la componente modulada en fase y amplificada, resultando en una copia amplificada de la señal de entrada.

La rama inferior elimina la envolvente de la señal mediante un limitador, obteniendo así una portadora modulada en fase con amplitud constante. Esta componente es amplificada hasta el nivel de potencia deseado mediante un amplificador clase C.

En una implementación moderna, tanto la envolvente como la portadora modulada en fase son generadas por un Procesador Digital de Señal (DSP).

Figura 2. Arquitectura original del transmisor EER

#### 2.1.2. Transmisor Polar:

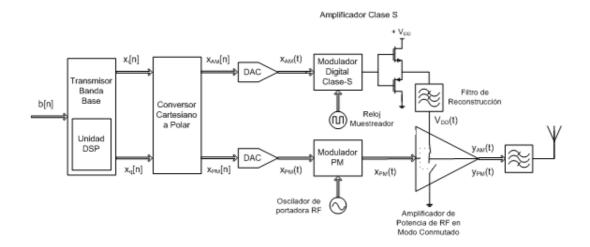

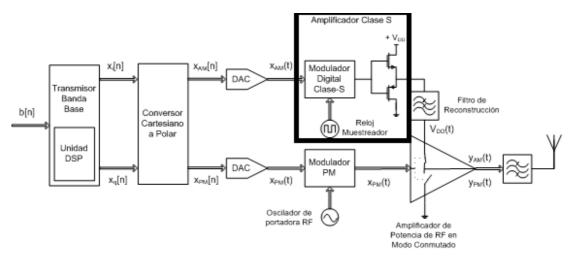

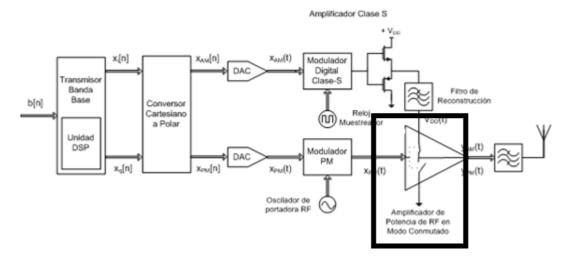

Basándonos en la idea de eliminación y restauración de envolvente, explicada anteriormente, surge la arquitectura del transmisor polar representado en la Figura 3 que además integra avances recientes en muestreo de señal.

Figura 3. Arquitectura del transmisor polar

La idea del transmisor polar es sustituir el modulador I/Q que teníamos en el transmisor cartesiano tradicional, por un modulador AM/PM polar. De este modo, se puede tratar de forma independiente las componentes de amplitud y fase,  $x_{AM}(t)$  y  $x_{PM}(t)$ , de la envolvente compleja de la señal de comunicaciones, hasta que son combinadas en el amplificador de potencia de RF. Este amplificador es un dispositivo de conmutación que opera en modo altamente eficiente, como un clase E

De esta forma podremos representar la señal paso banda a transmitir (antes del amplificador) en función de sus componentes de amplitud y fase, que también son señales paso bajo. Quedando expresado de la siguiente forma:

$$x(t) = x_{AM}(t) \cdot \cos(w_c \cdot t + x_{PM}(t))$$

(2)

Para asegurar un uso óptimo de la potencia, la rama encargada de la modulación AM debe realizar también una amplificación conmutada (clase S). Por lo tanto, la componente de amplitud  $x_{AM}(t)$  atraviesa un amplificador clase S y un filtro de reconstrucción, que la introduce un cierto retraso, y después modula dinámicamente la tensión de polarización en drenador del amplificador clase E.

La componente de fase  $x_{PM}(t)$  se transforma en una señal de envolvente constante que, al no tener variaciones de amplitud, puede servir de excitación del amplificador de potencia de alta eficiencia.

Por lo tanto, obtendremos una señal de salida que tiene información de amplitud  $(y_{AM}(t))$  y de fase  $(y_{PM}(t))$ .

El problema que presentan este tipo de arquitecturas es que está limitado por la presencia de una serie de no idealidades que provocan **distorsión no lineal**, lo que provoca que la eficiencia en potencia sea inferior al 100% que tendríamos idealmente. Las no idealidades más significativas, pero también más fáciles de controlar, son aquellas que aparecen a nivel de sistema, debidas a la propia arquitectura. También habrá que tener en cuenta las no linealidades de amplitud y fase en la etapa de modulación, el amplificador conmutado de alta eficiencia.

## Mecanismos lineales de distorsión: no idealidades debidas a la arquitectura del sistema

- Retraso diferencial entre las ramas de AM y PM.

- Ancho de banda finito del filtro reconstructor de la rama AM

El retraso que se produce entre la componente moduladora de amplitud y la portadora de RF modulada en fase fue anteriormente tratado en [2], considerándolo como fijo e independiente de la frecuencia de la envolvente banda base. Del mismo modo, el ancho de banda finito del modulador fue tratado de un modo aproximado, asumiendo un filtro de reconstrucción ideal.

Los fenómenos anteriores son procesos lineales, pero pueden causar distorsión no lineal, ya que, tanto la generación de las componentes AM y PM en el DSP del transmisor polar, como su recombinación en el amplificador de potencia, son ambos procesos no lineales.

Estas dos no idealidades debidas a la arquitectura del sistema fueron inicialmente estudiadas por Raab [2] que también reconoció la existencia de otras fuentes de distorsión asociadas al estado de modulación, las características  $V_{DD}$ -AM y  $V_{DD}$ -PM del amplificador de potencia.

Más adelante, Milosevic [3] consideraría un filtro de reconstrucción más general para tratar la distorsión debida al ancho de banda finito del modulador.

## Mecanismos no lineales de distorsión: no idealidades debidas a la etapa de modulación

- Conversión  $V_{DD}(t)$ - $y_{AM}(t)$  no lineal.

- Modulación parásita V<sub>DD</sub> (t)-y<sub>PM</sub>(t).

La distorsión causada en la etapa de modulación es debida a las no linealidades de las características  $V_{\text{DD}}$ -AM y  $V_{\text{DD}}$ -PM del amplificador de potencia.

Un amplificador de potencia en modo conmutado tiene una conversión  $V_{DD}(t)$ - $y_{AM}(t)$  no lineal, denotada por una ligera compresión de la característica  $V_{DD}(t)$ - $y_{AM}(t)$  en niveles altos de  $V_{DD}$ .

Además, en niveles bajos de  $V_{DD}$ , presenta un fenómeno denominado feedthrough, que se caracteriza por la presencia de nivel de salida de RF cuando la tensión de polarización es nula. Este fenómeno también provoca una modulación parásita  $V_{DD}(t)$ - $y_{PM}(t)$ .

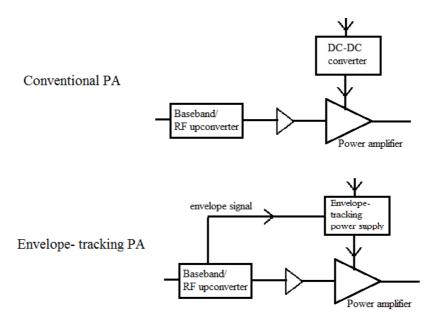

#### 2.2. ET (Envelope Tracking) seguimiento de la envolvente

Todo parece indicar que en el futuro las técnicas de polarización variable de amplificadores para seguimiento de envolvente, también conocida como *Envelope Tracking* [4], tendrán una gran importancia, especialmente la de modulación de la tensión de drenador (en algunos casos también se suele hacer de puerta), dado el alto grado de eficiencia energética que es posible alcanzar con tales amplificadores. La idea es que esta polarización variable se ajuste al nivel de la envolvente de la señal a amplificar [5], evitando la degradación brutal de la eficiencia que se produce cuando dichas condiciones se mantienen fijas.

Figura 4. Arquitectura del transmisor convencional vs ET

El inconveniente está en que tecnológicamente se requiere de fuentes de alimentación de salida variable eficientes (lo cual se consigue usando fuentes conmutadas) y que puedan variar a alta velocidad, ya que han de ser capaces de seguir el ancho de banda de la envolvente [6]. Este ancho de banda requerido puede llegar a ser de decenas de MHz.

## 3. Técnicas para mejorar la eficiencia del transmisor polar

#### 3.1. Uso de un amplificador de envolvente de alta eficiencia

Uno de los limitadores para mejorar la eficiencia de un transistor polar es la rama superior (por donde va la amplitud de la señal), ya que se encarga de amplificar la señal moduladora que llega al amplificador de RF.

Figura 5. Arquitectura del transmisor polar, detalle del amplificador clase S

La eficiencia total del transmisor polar viene determinada por el producto de la eficiencia de la rama AM y la del amplificador de RF. Se sabe que en el amplificador de RF podemos obtener un valor alto de eficiencia (en función de la banda de trabajo), sin embargo en la red de AM no tenemos tanta suerte. Podría mejorar de manera considerable empleando un amplificador de envolvente de alta eficiencia.

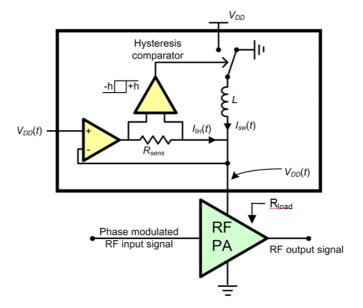

Existen dos tipos de soluciones que se han propuesto para implementar el amplificador de envolvente de alta eficiencia: un amplificador lineal asistido por conmutación y un convertidor reductor DC/DC (o amplificador clase S tradicional). Elegiremos uno u otro en función del ancho de banda en el que queramos trabajar.

El amplificador lineal asistido por conmutación permite solventar el problema para condiciones de gran ancho de banda, aprovechando el hecho de que la mayor parte de la energía se concentra a muy bajas frecuencias. Si se usase este circuito se llegaría a alcanzar un excelente nivel de eficiencia total, en torno al 60% [7].

Figura 6. Amplificador lineal asistido por conmutación

Esta topología se basa en la combinación de una etapa lineal de amplificación de tensión de banda ancha con una etapa de corriente en modo conmutado de alta eficiencia, usando un lazo de realimentación (control de realimentación de corriente mediante un comparador de histéresis). Se trata de una configuración con división de banda, donde el contenido de potencia en DC y a bajas frecuencias le proporciona una fuente conmutada de alta eficiencia, mientras que la potencia a alta frecuencia es suministrada por una fuente de alta fidelidad.

Para soluciones banda estrecha se emplearan los convertidores DC/DC conmutados con excelentes resultados en eficiencia (tanto usando modulación sigmadelta como modulación por anchura de pulso (PWM)).

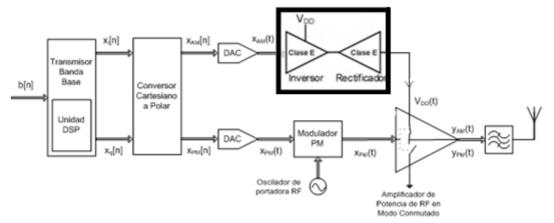

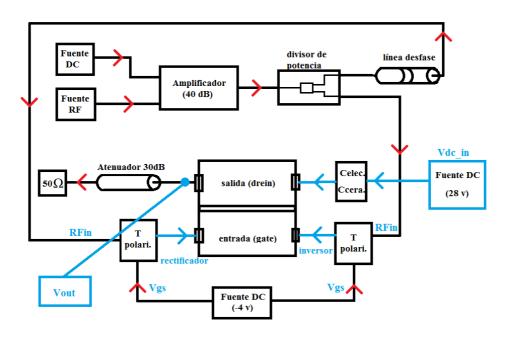

La Figura 7 muestra una posible implementación del convertidor DC/DC integrado en la arquitectura del transistor polar. Está compuesto de dos partes que realizan el cambio de señal de entrada de DC a señal de salida de RF, para posteriormente detectarla, obteniendo a la salida del convertidor la señal de amplitud amplificada. Esta implementación será la que desarrollaremos a lo largo del proyecto.

Figura 7. Arquitectura del transmisor polar con un convertidor DC/DC como el desarrollado en este proyecto

#### 3.2. Uso de transistores GaN HEMT

Uno de los factores clave en el diseño de un dispositivo de alta eficiencia, son los componentes utilizados y, en concreto, el tipo de transistor. Nos centraremos en los transistores HEMT (High Electron Mobility Transistor) que son un tipo de transistor de efecto de campo. Exiten gran variedad de composiciones de materiales de estos transistores Silicio, Arseniuro de Galio (GaAs), Indio o Nitruro de Galio (GaN) todo depende de la aplicación para la que se destine.

Los requisitos actuales en la reducción del consumo de energía y reducción del volumen en sistemas de electrónica de potencia requieren dispositivos semiconductores con mejora en potencia disipada y frecuencia de conmutación más alta. Aunque los dispositivos de silicio hayan estado desempeñando el papel principal como dispositivo activo en la electrónica de potencia hasta ahora, el límite del uso de este material parece cercano, lo que implica que los dispositivos con nuevos materiales deben estar preparados para los requisitos de alto rendimiento del futuro.

Una breve comparativa entre los dispositivos de Silicio y los de GaN HEMT [8] demuestra una velocidad de conmutación 10 veces más alta que el límite del silicio. Este resultado muestra que el estado del arte del GaN HEMT tiene ya características superiores lejanas al límite del dispositivo del Silicio. Aunque los dispositivos prácticos de GaN todavía tengan resistencias parasitas tales como resistencia del substrato o la resistencia de contacto, los nuevos dispositivos disponibles en el mercado pueden demostrar su resultado en operaciones de alta frecuencia.

Los semiconductores de Nitruro de Galio (GaN) y sus aleaciones (AlGaN, In GaN) han surgido en la última década como uno de los materiales más prometedores en el campo de los transistores de efecto de campo para aplicaciones de alta potencia y alta

temperatura. Su principal atractivo radica en la anchura del gap (GaN 3.4 eV) que le confiere gran estabilidad térmica y tensión de ruptura (3 MV/cm).

Dadas sus características, en estudios realizados en 2006 [9] y en 2010 [10] se destacan los AlGaN/GaN HEMTs como buenos candidatos para su uso como convertidores DC/DC en aplicaciones de alta frecuencia. Según el fabricante, las investigaciones se centran principalmente en obtener aplicaciones con eficiencia extremadamente alta, cercana al 90%. Sin ser tan optimistas, teniendo en cuenta que en la eficiencia del transmisor polar influye notablemente la rama AM, se podría obtener eficiencias superiores al 50%, con eficiencias del convertidor DC/DC y del amplificador de RF cercanas al 80%.

#### 4. Técnicas de modulación de la impedancia de carga

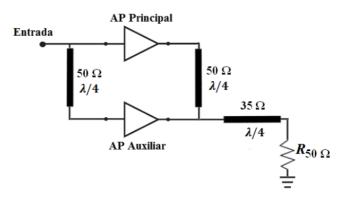

La arquitectura Doherty o amplificador Doherty, como también se conoce, fue propuesto por primera vez en 1936 por W. H. Doherty [11]. Su descubrimiento tuvo lugar debido a la observación de una disminución de los niveles de eficiencia que se alcanzaban cuando se trabajaba con señales que presentaban variaciones significativas en su amplitud.

La arquitectura clásica, combina dos amplificadores de potencia de igual capacidad a través de una red o línea de transmisión de  $\lambda/4$ , como se puede ver en la siguiente figura:

Figura 8. Arquitectura básica de un amplificador Doherty

Uno de los aspectos más interesantes que la caracteriza es la modulación mutua de la impedancia de carga de los amplificadores [4]. Este concepto plantea que la resistencia o la reactancia de una carga de RF se puede modificar aplicando corriente desde otra fuente, en fase con la primera. Esta relación estaría caracterizada por la siguiente expresión:

$$Z_1 = R_L \cdot \left(\frac{l_1 + l_2}{l_2}\right) \tag{3}$$

donde  $Z_I$  es la impedancia vista por el primer generador y que puede ser controlada mediante la variación de la amplitud y/o la fase de la corriente  $I_2$ .

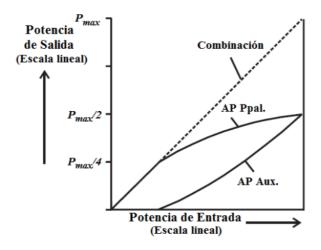

El amplificador principal (de portadora) se polariza en clase B, mientras que el auxiliar (de picos) se polariza en clase C. La potencia de salida máxima va a estar dada por la combinación de ambos dispositivos (principal y auxiliar). Cuando el nivel de entrada es igual o menor que la mitad del valor pico de la envolvente, sólo opera el amplificador principal; a medida que aumenta el nivel de señal de entrada el auxiliar se "enciende", puesto que el principal ha entrado en saturación y ambos contribuyen a la potencia de salida para mantener la eficiencia elevada. En este régimen la potencia de salida crece de forma proporcional a la potencia de entrada porque la relación entre ellas es casi lineal, como se observa en la Figura 9.

Figura 9. Funcionamiento de un amplificador Doherty

La limitación fundamental de este esquema está dada por el hecho de que al usar dispositivos reales la característica de salida pierde la linealidad, sobre todo cuando se trabaja con señales cuyo PAPR está por encima de los 10 dB. Por otra parte ambos amplificadores operan en modo lineal y por consecuencia limitados en términos de eficiencia. También presenta restricciones en términos de ancho de banda, esto puede solucionarse aumentando el número de amplificadores auxiliares, pero como es evidente se encarece el sistema. A pesar de las dificultades, esta es la variante más utilizada actualmente en las estaciones base, para elevar la eficiencia, puesto que solamente implica el cambio del amplificador de RF dentro del transmisor I/Q, no por la configuración Doherty convencional, pero si por una asimétrica o por una tres niveles (un amplificador principal y dos auxiliares), que permita manipular señales reales de comunicación donde la PAPR se encuentra por encima de los 6 dB.

Sección II

#### 5. Referencias

- [1] L. R. Kahn, "Single-Sideband Transmission by Envelope Elimination and Restoration", Proc. IRE, vol. 40, no. 7, pp. 803-806, Julio 1952.

- [2] F. H. Raab, "Intermodulation Distortion in Kahn-Technique Transmitters," IEEE Trans. on MTT, vol. MTT-44, no. 12, pp. 2273-2278, Diciembre 1996.

- [3] D. Milosevic, J. van der Tang and A. van Roermund, "Intermodulation Products in the EER Technique Applied to Class-E Amplifiers," Int. Symp. on Circuits and Syst. Dig., vol. I, pp.637-640, Vancouver, Mayo 2004.

- [4] F. H. Raab, P. Asbeck, S. Cripps, P. B. Kenington, Z. B. Popovic, N. Pothecary, J. F. Sevic, and N. O. Sokal, "Power amplifiers and transmitters for RF and microwave," IEEE Trans. Microwave Theory Tech, vol. 3, pp. 814–826, March 2002.

- [5] J. de Mingo, A. Valdovinos, "Performance of a New Digital Base-Band Predistorter Using Calibration Memory", *IEEE Transactions onVehicular Technology*, Vol. 50, No: 4, pp 1169- 1176, July 2001.

- [6] D. F. Kimball, J. Jeong, et al., "High-Efficiency Envelope-Tracking WCDMA Base-Station Amplifier Using GaN HFETs," *IEEE Trans. Microwave Theory and Techniques*, Vol. 54, No. 11, pp. 3848-3856, Nov. 2006.

- [7] I. Kim, J. Kim, J. Moon, J. Kim, B. Kim, "Hybrid EER Transmitter using Highly Efficient Saturated Power Amplifier for 802.16e Mobile WiMAX Application," *IEEE MTT-S Microwave Symp. Dig.*, Boston, USA, pp. 1385-1388, June 2009.

- [8] I. Omura, W. Saito, T. Domon, K. Tsuda, "Gallium Nitride Power HEMT for High Switching Frecuency Power Electronics" IEEE, 978-1-4244-1728-5/07/2007

- [9] Yang Gao, Alex Q. Huang "Feasibility Study of AlGaN/GaN HEMT for Multimegahertz DC/DC Converter Applications", North Carolina State University, IEE, 1-4244-0449-5/06/2006.

- [10] M. de las Nieves Ruiz Lavín "Convertidor resonante de potencia en RF sobre tecnología GaN HEMT", Proyecto fin de carrera, Universidad de Cantabria, 2010.

- [11] W. H. Doherty, "A new high efficiencypower amplifier for modulated waves", Proc. IRE, vol. 24, no. 9, pp. 1163-1182, Sept. 1936.

## Amplificadores de Potencia

#### 1. Características de los amplificadores de potencia

Para la creación de transmisores inalámbricos tendremos que tener en cuenta el efecto del amplificador de potencia de RF, ya que es el que más potencia consume dentro del sistema de transmisión.

El desarrollo de estos trasmisores emergentes viene determinado por el límite del compromiso linealidad-eficiencia que alcanzan los trasmisores IQ, que en la actualidad operan dentro de las estaciones base. Ambos parámetros, linealidad y eficiencia, dependen en gran medida del funcionamiento del amplificador de potencia de RF.

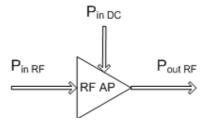

Figura 10. Arquitectura del transmisor polar, detalle del amplificador de potencia

Los amplificadores de potencia proporcionan ganancia en tensión y ganancia en corriente. Tiene dos funciones, convertir la potencia de entrada de DC en potencia de salida RF y amplificar la potencia de entrada de la señal de RF. Esto se puede ver claramente en la Figura 11.

Figura 11. Potencias en un amplificador de potencia de RF

#### 1.1. Parámetros significativos del amplificador de potencia

#### 1.1.1. Eficiencia

La eficiencia de este proceso de amplificación se puede expresar en varios términos:

Eficiencia de drenador (η<sub>D</sub>)

La eficiencia en drenador, también conocida como eficiencia de conversión DC-RF, representa en qué medida la potencia de DC se convierte en potencia de salida de RF. Se puede obtener con la siguiente expresión:

$$\eta_D = \frac{P_{outRF}}{P_{inDC}} \tag{4}$$

• Eficiencia de potencia añadida (PAE).

La eficiencia de potencia añadida (PAE, Power-Added Efficiency) considera además la ganancia del amplificador, definiendo la eficiencia como la diferencia de potencia de RF entre la salida y la entrada dividida entre la potencia de DC:

$$PAE = \frac{P_{outRF} - P_{inRF}}{P_{inDC}} = \frac{P_{outRF} \cdot \left(1 - \frac{P_{inRF}}{P_{outRF}}\right)}{P_{inDC}} = \frac{P_{outRF}}{P_{inDC}} \cdot \left(1 - \frac{1}{G}\right) = \eta_D \cdot \left(1 - \frac{1}{G}\right)$$

(5)

Si la ganancia es elevada, PAE  $\cong \eta$  (eficiencia total). Si la ganancia es pequeña, la PAE sería bastante inferior a  $\eta$ . En condiciones de operación con G<1, la PAE <0.

Eficiencia total (η).

La eficiencia total compara la potencia total recibida por el amplificador (RF+DC) con la potencial total entregada a la salida. Se expresa de la siguiente manera:

$$\eta = \frac{P_{outRF}}{P_{inRF} + P_{inDC}} = \frac{\eta_D}{\frac{\eta_D}{G} + 1}$$

(6)

#### 1.1.2. Linealidad

La linealidad de un amplificador, como hemos visto, da una idea de la capacidad del dispositivo para reproducir en la salida la amplitud y la fase de la señal de entrada. Es decir, el dispositivo es lineal a la frecuencia de trabajo si la amplitud de la señal de salida varía linealmente con la amplitud de la señal de entrada, y además, la diferencia entre la fase de la señal de salida y la de la señal de entrada permanece constante. Cuando el dispositivo es no lineal, la señal de salida aparece distorsionada: la amplitud de salida se comprime y la fase deja de ser constante.

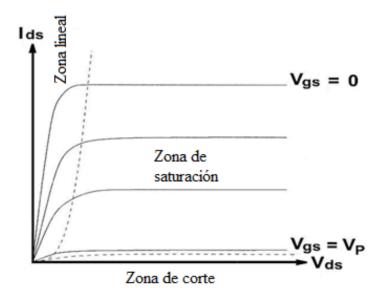

La linealidad es función de la porción de tiempo que el amplificador permanece en la zona de funcionamiento lineal, como se puede ver en las curvas características I-V que se muestran en la Figura 12.

La no linealidad de la amplitud suele provocar, en general, mayor distorsión que la variación de fase. El comportamiento no lineal provocado por la compresión de la ganancia se da cuando la amplitud de la señal de entrada al amplificador es tan grande que satura al dispositivo. La variación de la fase de la señal de salida también es función del grado de saturación. Por lo tanto, la distorsión de la señal es más significativa a medida que el amplificador se aproxima a la zona de funcionamiento en saturación.

Figura 12. Curvas características I-V de un transistor FET

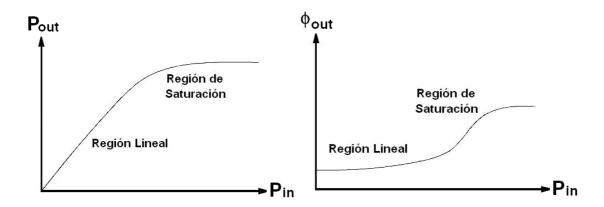

En la Figura 13 podemos observar la variación de la ganancia de compresión y de la fase en función de la potencia de entrada a un amplificador de potencia:

Figura 13. Ganancia de compresión y variación de fase debida a la saturación de un amplificador

Para obtener una amplificación lineal, el nivel pico de potencia debe mantenerse dentro de la región lineal del amplificador, y evitar así los efectos no deseados debido a las no linealidades. Teniendo en cuenta esto, si se pretende una amplificación lineal, la opción más común consiste en trabajar lejos del punto de compresión lo que provoca que la eficiencia del amplificador de potencia disminuya.

Cuando amplificamos señales de amplitud constante no nos influye la no linealidad del amplificador de potencia. Esto es debido a que la saturación del amplificador es función de la amplitud de la señal de entrada, por lo que, si ésta se mantiene constante, la saturación también se produce a un nivel constante y la ganancia del amplificador no varía. Tanto las arquitecturas "outphasing" como la polar, introducen en los amplificadores señales de amplitud constante.

#### 1.2. Comportamiento no lineal del amplificador

El amplificador de potencia, cuando trabaja en zonas de alta eficiencia energética (cerca del punto de compresión), se comporta como un dispositivo altamente no lineal. La no linealidad del amplificador de potencia provoca distorsión en la señal de salida.

Un modelo simplificado del amplificador de potencia, sin tener en cuenta efectos de memoria, relaciona la señal de salida con la de entrada a través de un polinomio de grado N como muestra la ecuación siguiente:

$$V_{out}(t) = G_V \cdot V_{in}(t) + k_2 \cdot V_{in}^2 + k_3 \cdot V_{in}^3 + \dots + k_N \cdot V_{in}^N(t)$$

(7)

Si consideramos únicamente los tres primeros términos, el primero corresponde al término lineal de ganancia por la entrada. El segundo término es proporcional al cuadrado de la tensión de entrada y provoca la distorsión armónica de segundo orden. El tercer término, que es proporcional al cubo de la tensión de entrada, es la causa de la distorsión de intermodulación o de tercer orden.

En la señal de salida tendremos armónicos y productos de intermodulación no deseados, estos últimos debidos, por ejemplo, a los efectos no lineales de los términos segundo y tercer orden del polinomio. Pueden identificarse componentes en banda y fuera de la banda de frecuencias de la señal original, como la distorsión armónica de 2º y 3er orden y la distorsión de intermodulación de 2º y 3er orden.

La distorsión armónica puede eliminarse mediante filtrado, pero no ocurre así con la distorsión producida por los productos de intermodulación en banda, ya que las frecuencias aparecen demasiado cerca de las frecuencias de la señal.

#### 2. Clases de amplificadores de potencia

Los amplificadores de potencia se dividen en dos grandes clases: amplificadores modo fuente de corriente y amplificadores modo conmutado. En este caso, nos centraremos más en el modo fuente de corriente, los cuales pueden pertenecer a diferentes tipos en función del punto de operación del dispositivo dentro de la recta de carga dinámica. La elección de este punto causa que el dispositivo activo no esté, necesariamente, conduciendo durante toda la duración del ciclo completo de una señal sinusoidal (sólo ocurre en el clase A).

A continuación se exponen las características generales de las clases más comunes. Entraremos más en detalle con los amplificadores en modo conmutado, concretamente el Clase E, ya que son considerados como una buena opción en amplificadores de potencia para sistemas inalámbricos; por tanto, será el que utilizaremos en este proyecto.

#### Clase A

El transistor se encuentra siempre polarizado en su región de saturación para un FET (o lineal para un bipolar), mediante la inyección de una corriente continua y constante en drenador. La señal mantiene al transistor conduciendo durante los 360° del ciclo y las corrientes y tensiones presentes en el circuito de salida son una réplica de las señales de entrada.

- Ventajas: proporciona la amplificación más lineal y el mayor factor de ganancia de los amplificadores. Permite su utilización a frecuencias próximas a la máxima de operación del transistor.

- Inconvenientes: la eficiencia es muy baja (idealmente 50%), debido a que el dispositivo disipa potencia incluso en ausencia de señal de entrada.

#### Clase B

Los transistores están polarizados en el límite entre la región de saturación y la región de corte, para el caso de FET. La conducción sólo se realiza durante un semiciclo (180°).

- -Ventajas: la eficiencia es alta (idealmente 78.5%), debido a que no hay consumo de potencia en ausencia de señal de entrada. Tiene un comportamiento bastante lineal.

- Inconvenientes: si se implementa con bipolares, en aplicaciones de banda ancha requiere un montaje en contrafase para poder amplificar en los dos semiciclos de la señal de entrada y, además, introducen un tipo de distorsión asociada al circuito de entrada denominada distorsión de cruce.

#### Clase AB

Es un compromiso entre la clase A y la B, tanto desde el punto de vista de eficiencia como de ganancia en potencia y linealidad. Trata de corregir la distorsión de cruce recurriendo al montaje en contrafase mediante diodos. El punto de trabajo, en este caso, es tal que el ángulo de conducción está comprendido entre 180°- 360°. Esta situación se da cuando el punto de polarización se encuentra en la zona de saturación pero bastante más cerca de la de corte que de la lineal (FET).

- Ventajas: proporciona una señal de salida altamente lineal con respecto a la señal de entrada, aunque cada dispositivo sólo conduce durante medio ciclo, ambos dispositivos "se ceden el relevo".

- Inconvenientes: empeoramiento del rendimiento respecto a la clase B, ya que se consume la potencia necesaria para dicha polarización en reposo.

#### Clase C

Se polariza por debajo del corte, y la carga se acopla mediante un circuito LC paralelo, sintonizado a la frecuencia de la señal de entrada. De esta forma, se encuentra en estado de corte la mayor parte del periodo de dicha señal y amplifica sólo durante cortos intervalos, casi funciona como un conmutador.

- Ventajas: aumenta la eficiencia respecto a los anteriores (idealmente 100%), a costa de reducir la linealidad a medida que el ángulo de conducción se aproxima a cero

- Inconvenientes: la ganancia es bastante inferior, de manera que la potencia de excitación necesaria va aumentando. Es esencialmente no lineal, incluso para la frecuencia fundamental.

#### Amplificadores en Modo Conmutado: Clases D, D<sup>-1</sup>, E, F, F<sup>-1</sup> y S

Las denominaciones de clases, desde la D hasta la S, corresponden a distintas variantes de amplificadores de conmutación. La optimización del diseño de estos amplificadores para ser modulados por la tensión de drenador es clave en la arquitectura del transmisor polar.

Los amplificadores de potencia en modo conmutado son no lineales, pero consiguen altas eficiencias, ya que funcionan como un conmutador, minimizando con ello las pérdidas de potencia en el transistor. Funcionan haciendo la tensión drenadorfuente cero cuando por el conmutador fluye corriente (interruptor en ON), y forzando la corriente a cero cuando existe diferencia de tensión entre los terminales drenador-fuente (interruptor en OFF).

En amplificadores conmutados clase D, E y F el transistor está altamente saturado por una señal de gran amplitud a la entrada, estando el dispositivo polarizado cerca del corte. Las formas de onda de tensión y corriente se ven recortadas por estas dos condiciones, consiguiendo así el efecto el comportamiento de conmutador, y alcanzando el 100% de eficiencia de drenador teórica.

En la práctica, existen pérdidas provocadas por elementos parásitos como reactancias, o la resistencia existente cuando el conmutador se encuentra en estado ON (idealmente cero). Estos factores, junto con un tiempo de conmutación también distinto de cero, hacen que la eficiencia teórica sea inalcanzable en la práctica.

#### 3. Amplificador clase E

El descubrimiento del amplificador clase E es relativamente reciente (N.O. Sokal y A.D. Sokal, 1975 [1]), pero quedó relegado, hasta que, alrededor de los años 90, el despliegue de la telefonía móvil requirió de amplificadores de altísima eficiencia para economizar batería.

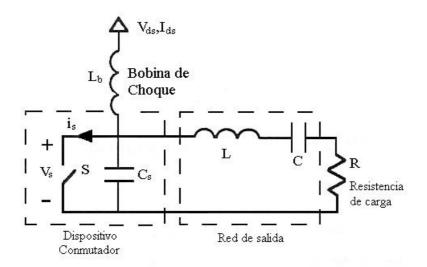

Figura 14. Circuito de alta eficiencia clase E original

Estos amplificadores trabajan en régimen de saturación, por lo que son extremadamente no lineales, y los armónicos generados aparecen en su salida, donde deben ser convenientemente filtrados. La red resonante de salida, como se puede ver en la Figura 14, tiene como principal innovación, una capacidad en paralelo con el dispositivo. Esta capacidad será aportada de manera externa, o bien estará constituida, en parte o completamente por la capacidad parásita de salida del dispositivo. Además se caracteriza por el empleo de un único dispositivo activo, un transistor conmutado conectado a una red de carga pasiva.

En contrapartida a la no linealidad, el rendimiento de estos amplificadores es muy alto, pudiendo superar el 90%, y en condiciones ideales, un 100%. Su alta eficiencia se debe a que funciona como un interruptor (conectado a una fuente de corriente constante) que evita las pérdidas de potencia mediante la carga y descarga del condensador del que dispone, alcanzando así mejores valores de eficiencia en alta frecuencia que un clase D.

Sus ventajas principales son, además de su mayor eficiencia, la mayor fiabilidad, la reducción del tamaño y del peso de los equipos y sobre todo, su diseño predecible y consistente gracias a la existencia de procesos de diseño claros y definidos. Se utilizan en algunas estaciones transmisoras y aplicaciones satelitales donde la eficiencia es un aspecto fundamental.

#### 2.1. Análisis del amplificador de potencia clase E

Un amplificador de potencia que trabaja con una eficiencia del 75% puede entregar tres veces más potencia que otro que lo haga con un 50% de eficiencia utilizando el mismo dispositivo, ya que la potencia de salida está limitada por la disipación térmica en los transistores. Por esto, pasaremos a analizar la topología del

amplificador en modo conmutado clase E, teniendo en cuenta los niveles de eficiencia alcanzados en unos estudios realizados en [2][3].

El amplificador clase E es un circuito resonante en modo conmutado en el cual el producto de la tensión y la corriente en el dispositivo conmutador es idealmente nulo en todo momento. El transistor actúa como un interruptor, y el circuito que lo acompaña ha de ser debidamente diseñado para procurar un funcionamiento clase E.

En bajas frecuencias, estos circuitos han conseguido eficiencias de hasta el 96% [4]. Idealmente, la eficiencia sólo está limitada por la resistencia de saturación drenadorfuente del transistor, y por las propiedades de sus elementos parásitos. Las reactancias parásitas del elemento activo están incluidas en el diseño del circuito sintonizado por lo que no degradan las prestaciones del amplificador. La capacidad C<sub>s</sub>, de la Figura 15, puede representar la capacidad de salida intrínseca del transistor, mientras que parte de la inductancia L estaría relacionada con el efecto del empaquetado del transistor.

Para poder hacer un análisis sencillo del circuito clase E, realizaremos las siguientes suposiciones:

- El *duty cycle* o ciclo útil que nos permite un funcionamiento óptimo es del 50%, es decir, que el conmutador estará en estado ON (encendido) durante medio periodo y en estado OFF (apagado) durante el otro medio.

- El dispositivo conmutador tiene una resistencia en estado ON (R<sub>ON</sub>) idealmente nula y en estado OFF (R<sub>OFF</sub>) infinita. En la práctica, se debe asegurar que la resistencia ofrecida por el dispositivo cuando se encuentra en abierto sea lo suficientemente alta y que la resistencia parásita que ofrece cuando se encuentra en corto sea lo más pequeña posible. El condensador C<sub>s</sub>, para un diseño de frecuencia máxima, consiste únicamente en la capacidad parásita de salida del transistor, la cual se asumirá como lineal en este análisis. En la práctica, la capacidad C<sub>s</sub> es a menudo no lineal, y cambia en función del voltaje aplicado.

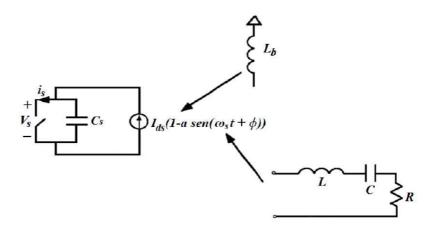

- La corriente que circula a través de la carga será idealmente sinusoidal a la frecuencia fundamental de trabajo, y la corriente que fluye por la bobina de choque L<sub>b</sub> se asume constante (I<sub>ds</sub>). Se aplica, por tanto, una corriente equivalente a través de la capacidad de conmutación, que se compone de un nivel constante (DC) más una sinusoide (RF).

La solución exacta de este circuito en el dominio del tiempo, aun asumiendo elementos ideales y C<sub>s</sub> lineal, requiere la solución de un sistema de ecuaciones diferenciales de tercer orden variante en el tiempo, pero con las aproximaciones supuestas anteriormente, se reduce a un sistema de primer orden variante en el tiempo, como muestra la Figura 15:

Figura 15. Circuito de alta eficiencia clase E asumiendo corriente sinusoidal en la carga [6]

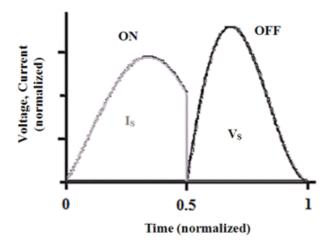

Como se puede ver, el conmutador puede estar en estado ON u OFF. A continuación, analizaremos los pasos de un estado a otro:

Cuando el interruptor está cerrado (OFF), no hay tensión entre sus terminales y una corriente sinusoidal (más una componente de continua) fluye por él.

En el instante en el que está en estado ON, la corriente que lo atraviesa es cero, pero en el instante en que conmuta a estado OFF se produce un salto o discontinuidad de la corriente que circula por el conmutador, al transferirse la corriente del interruptor a la capacidad en paralelo.

Este salto de intensidad causará pérdidas que aparecerán en cualquier inductancia parásita entre el conmutador y el condensador. En el caso aquí presentado, donde  $C_s$  es la capacidad parásita interna de un transistor, esta inductancia está minimizada. Si se utiliza alguna capacidad externa, entonces, cualquier inductancia parásita entre el transistor y la capacidad provoca una pérdida de energía. Esto se produce cada periodo de conmutación en la inductancia parásita.

$$Perdidas = \frac{1}{2} \cdot L \cdot i^2 \tag{8}$$

Cuando el conmutador está en estado OFF, la corriente sinusoidal continúa circulando, pero lo hace a través de la capacidad en paralelo al interruptor. Durante el semiciclo OFF:

$$C_{s} \cdot \frac{\partial V_{s}}{\partial t} = I_{ds} \cdot (1 - a \cdot \sin(w_{s} \cdot t' + \varphi))$$

(9)

Que integrando resulta:

$$V_S(t) = \frac{I_{ds}}{C_S} \cdot \int_0^t (1 - a \cdot \sin(w_S \cdot t' + \varphi)) \cdot dt'$$

(10)

Sección III —————

Para garantizar un modo de operación clase E es necesario imponer ciertas condiciones de contorno, como que el condensador  $C_s$  permanezca descargado en los cambios de estado del conmutador, de ON a OFF y viceversa, y procurar transiciones suaves en la forma de onda de la señal. Estas condiciones para el clase E son:

• ZVS (Zero Voltage Switching) [Conmutación a tensión cero]:

$$V_{DS}(t = t_{ON}) = 0 (11)$$

• ZDS (Zero Derivative Switching) [Conmutación a derivada cero]:

$$\frac{\partial V_{DS}(t)}{\partial t} | t = t_{ON} = 0 \tag{12}$$

La primera de las dos condiciones evita que el condensador se cortocircuite en los cambios de estado del conmutador y la segunda asegura transiciones suaves en dichos cambios de estado.

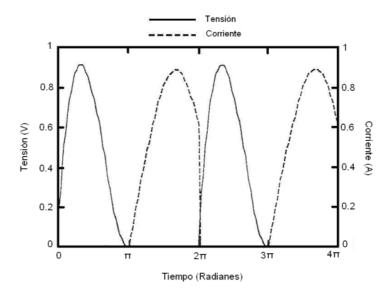

Figura 16. Formas de onda de tensión y corriente en estado OFF y ON respectivamente [5]

La forma de onda de la corriente en el estado ON es aproximadamente sinusoidal. Esto se consigue si el factor de calidad del circuito resonante es alto  $(Q_L \ge 2.5)$ . En cuanto a la tensión en estado OFF queda determinada por la caída en el condensador. Es precisamente con esta capacidad que se consiguen las condiciones de ZVS y ZDS.

Para lograrlas, la impedancia vista desde el paralelo entre el condensador y drenador hacia el circuito resonante debe ser inductiva.

Aplicando las condiciones de contorno anteriores, podremos resolver la integral de la ecuación 10:

$$V_{S}(t) = \frac{I_{dS}}{w_{S} \cdot C_{S}} \cdot \left( w_{S} \cdot t + a \cdot (\cos(w_{S} \cdot t + \varphi) - \cos \varphi) \right)$$

(13)

Por lo que podremos determinar las componentes a y φ:

$$a = \sqrt{1 + \frac{\pi^2}{4}} \cong 1.862 \tag{14}$$

$$\varphi = -\tan^{-1}\left(\frac{2}{\pi}\right) \cong -32.48^{\circ} \tag{15}$$

Es necesario recordar que estas constantes son válidas para cualquier circuito clase E de elevado factor de calidad, con una capacidad en paralelo con el conmutador. Ya se saben, por tanto, las tensiones y corrientes en el conmutador

$$V_{S}(t) = \begin{cases} \frac{I_{ds}}{w_{s} \cdot C_{s}} \cdot \left(w_{s} \cdot t + a \cdot (\cos(w_{s} \cdot t + \varphi) - \cos \varphi)\right) & 0 \leq w_{s} \cdot t \leq \pi \\ 0 & \pi \leq w_{s} \cdot t \leq 2 \cdot \pi \end{cases}$$

(16)

$$V_{s}(t) = \begin{cases} 0 & 0 \le w_{s} \cdot t \le \pi \\ I_{ds} \cdot (1 - a \cdot \sin w_{s} \cdot t + \varphi) & \pi \le w_{s} \cdot t \le 2 \cdot \pi \end{cases}$$

$$(17)$$

Si se representan estas formas de onda, serían como se muestran en la Figura 17:

Figura 17. Formas de onda teóricas de la tensión y la corriente en un conmutador clase E

Es interesante saber cuánta corriente Ids se genera para una tensión dada Vds, y viceversa:

$$V_{ds} = \frac{1}{T_s} \cdot \int_0^{\frac{T_s}{2}} V_s(t) \cdot dt = \frac{1}{\pi} \cdot \frac{I_{ds}}{W_s \cdot C_s}$$

(18)

$$I_{ds} = \pi \cdot w_s \cdot C_s \cdot V_{ds} \tag{19}$$

Una vez establecidas  $w_s$ ,  $C_s$  y  $V_{ds}$ , el dispositivo debe estar habilitado para manejar la corriente máxima requerida, cuya expresión puede verse a continuación.

$$I_{\text{max}} = (1+a) \cdot I_{\text{ds}} \cong 2.86 \cdot I_{\text{ds}}$$

(20)

Si el dispositivo no puede soportar esta corriente será imposible conseguir un circuito clase E de comportamiento ideal a esta frecuencia.

Un valor orientativo de la frecuencia máxima de operación se da en la siguiente expresión:

$$f_{\text{max}} = \frac{I_{\text{ds}}}{2 \cdot \pi^2 \cdot C_{\text{s}} \cdot V_{\text{ds}}} = \frac{I_{\text{max}}}{C_{\text{s}} \cdot V_{\text{ds}}} \cdot \frac{1}{2 \cdot \pi^2 \cdot (1+a)} \cong \frac{I_{\text{max}}}{56.5 \cdot C_{\text{s}} \cdot V_{\text{ds}}} \tag{21}$$

Como se puede deducir de la expresión anterior, cuanto mayor es la tensión de polarización de drenador, menor es la frecuencia máxima de operación (proporcionalmente). Por encima de esta frecuencia, el circuito no puede funcionar como un clase E ideal. Sin embargo, se puede conseguir un funcionamiento aproximado al ideal, a costa de una ligera degradación de la eficiencia máxima obtenida.

Lo anterior también implica que, dadas diversas tecnologías (MESFET, HEMT, HBT) y utilizando determinados procesos de fabricación, se consigan diferentes rendimientos en el aspecto de potencia de salida máxima en función de la frecuencia, para un circuito clase E.

Observando la componente de DC de  $v_s(t)$ , se obtendrá una expresión que describe los parámetros de continua del circuito clase E (Vds y Ids). En cambio, la componente a la frecuencia fundamental de  $v_s(t)$ , describe las impedancias complejas en RF del circuito.

Las componentes frecuenciales de los armónicos superiores, presentes en el voltaje del conmutador, no serán consideradas para este análisis de primer orden. Sin embargo, se supondrá que la red de carga tiene una impedancia casi infinita a estos armónicos superiores y, por lo tanto, la corriente que fluye por el conmutador para los armónicos superiores deberá tender a cero.

La componente fundamental de la corriente en la carga  $i_{net1}$  es conocida, pero la componente fundamental de la tensión en la carga  $v_{s1}$  debe ser hallada mediante el uso de series de Fourier, dado que  $v_s(t)$  es una función periódica. Los cálculos para resolver estas ecuaciones son bastante extensos y complejos, de modo que se mostrarán directamente los resultados.

$$v_{s1} = a_0 \cdot I_{ds} \cdot sen(w_s \cdot t + \phi_0)$$

(22)

$$i_{net1} = a \cdot I_{ds} \cdot sen(w_s \cdot t + \varphi)$$

(23)

donde las constantes  $a_0$  y  $\phi_0$  son:

$$a_0 = \frac{2 \cdot |K_1|}{I_{ds}} = \frac{1}{W_s \cdot C_s} \cdot \sqrt{\frac{\pi^2}{16} + \frac{4}{\pi} - \frac{3}{4}}$$

(24)

$$\phi_0 = \frac{\pi}{2} + \angle K_1 = \frac{\pi}{2} + tg^{-1} \left( \frac{2 \cdot \pi}{8 - \pi^2} \right)$$

(25)

El fasor impedancia de la red de carga externa puede ser ahora calculado como:

$$Z_{\text{net1}} = \frac{a_0}{a} \cdot e^{j \cdot (\phi_0 - \phi)} \cong \frac{0.28015}{w_s \cdot C_s} \cdot e^{j \cdot 49.0524^o}$$

(26)

Es interesante destacar que el ángulo de la impedancia de carga requerida para operar como clase E, con un condensador en paralelo al conmutador, es una constante independiente del resto de la topología del circuito. La magnitud es directamente proporcional a la impedancia del condensador en paralelo a la frecuencia de conmutación.

Para asegurar un funcionamiento clase E, todo lo que se necesita es obtener una impedancia a la frecuencia fundamental igual a  $Z_{net1}$ , y condiciones de circuito abierto a todos los armónicos superiores.

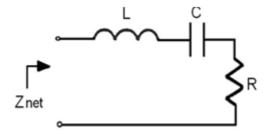

En la Figura 18 se expone una topología específica para la red de carga externa:

Figura 18. Red de carga externa vista por el dispositivo conmutador a frecuencias de RF

Esta red satisface la condición de alta impedancia a todas las frecuencias de armónicos superiores a la fundamental, por lo que sólo importa que la impedancia de la red sea la impedancia anterior a la frecuencia fundamental. Es decir, que:

$$Z_{\text{net1}} = Z_{\text{net}} = j \cdot w_s \cdot L + \frac{1}{j \cdot w_s \cdot C} + R$$

(27)

Si se iguala esta expresión a la obtenida anteriormente para  $Z_{net1}$ , se obtiene una ecuación compleja con dos incógnitas,  $C_s$  y C. Igualando las partes reales e imaginarias de ambas expresiones se obtiene:

$$C = C_{s} \cdot \left( \frac{\left(\frac{\pi^{2}}{4} + 1\right) \cdot \frac{\pi}{2}}{\frac{W_{s} \cdot L}{R}} \right) \cdot \left( 1 + \frac{\frac{\pi^{3}}{16} - \frac{\pi}{4}}{\frac{W_{s} \cdot L}{R} - \left(\frac{\pi^{3}}{16} - \frac{\pi}{4}\right)} \right) \cong C_{s} \cdot \left( \frac{5.447}{\frac{W_{s} \cdot L}{R}} \right) \cdot \left( 1 + \frac{1.153}{\frac{W_{s} \cdot L}{R} - 1.153} \right)$$

$$(28)$$

Estas ecuaciones de  $C_s$  y C son expuestas de esta forma y comparadas con las ecuaciones originales. La expresión para  $C_s$  obtenida aquí es idéntica a la original, mientras que la expresión dada por Sokal para C es:

$$C \cong C_s \cdot \left(\frac{5.447}{Q_L}\right) \cdot \left(1 + \frac{1.42}{Q_L - 2.08}\right) \quad \text{donde } Q_L = \frac{w_s \cdot L}{R}$$

(29)

Para diseñar un amplificador clase E utilizando esta topología se deben establecer inicialmente  $w_s$ , L y R. Estos parámetros determinan  $Q_L$ . Entonces  $C_s$  y C son evaluados utilizando las expresiones anteriores.

Sin embargo, esta topología tiene una utilidad limitada para circuitos de microondas, ya que la frecuencia, la impedancia de carga y la capacidad del conmutador no pueden ser establecidas de forma independiente.

Para un amplificador de microondas saturado, la impedancia de carga es a menudo de 50  $\Omega$ , y frecuentemente, al iniciar un diseño, ya se parte con un determinado transistor en mente, con una cierta capacidad de salida  $C_s$ .

Entonces la frecuencia de operación  $w_s$  queda ya establecida. Para solucionar el problema de no poder establecer estos tres parámetros de forma independiente, se expone a continuación una nueva topología, propuesta para su uso en circuitos de microondas clase E.

#### 4. Referencias

- [1] N. A. Sokal, A. D. Sokal, "Class-E A New Class of High-Efficiency Tuned Single-Ended Switching Power Amplifiers", IEEE Journal of Solid-State Circuits, Vol. SC-10, N° 3, Junio 1975

- [2] Roberto Peña Catalina, "Diseño De Un Amplificador Conmutado Clase-E A La Frecuencia De 2 GHz", Proyecto fin de Carrera, Universidad de Cantabria, Julio 2003

- [3] T. B. Mader, Z. B. Popović, "The Transmisión-Line High-Efficiency Class-E Amplifier", IEEE Microwave and Guided Wave Letters, Vol. 5, N° 9, Septiembre 1995

- [4] Cripps, S. C., Advanced Techniques in RF Power Amplifier Design, Norwood, MA: Artech House, 2002.

- [5] M. Niknejad. "The Class E/F Family of Harmonic-Tuned Switching Powers Amplifiers"

- [6] Leysi Rizo Salas "Implementacion de arquitecturas emergentes de transmisión basadas en conceptos de amplificación de alta eficiencia", Proyecto fin de Master, Universidad de Cantabria, 2012.

# Diseño de un Covertidor Clase E<sup>2</sup>

## 1. Introducción teórica del convertidor resonante de potencia

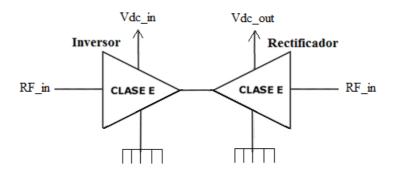

Siguiendo la línea de los primeros estudios realizados a finales de los 80 sobre el uso de un convertidor resonante DC/DC en alta frecuencia [1], se describe el convertidor como un sistema formado por un inversor clase E y un rectificador clase E. Su disposición sería la que se puede observar en la Figura 19.

Figura 19. Estructura del convertidor

Estudios anteriores habían implementado el convertidor resonante con un rectificador convencional, obteniendo niveles bajos de eficiencia. Por ello se optó por sustituirlos por unos rectificadores clase E, lo que permitió que su funcionamiento se asemejase a un interruptor, como se ha explicado en el capítulo anterior, evitando la pérdida de potencia en la carga y descarga del condensador, y que favorecen que el sistema pueda proporcionar gran eficiencia en alta frecuencia gracias a forzar tanto al inversor como al rectificador a las condiciones de ZVS y ZDS. Este convertidor, clase  $E^2$  que combina ambas topologías fue propuesto por Kazimierczuk y Jozwik [2].

La mejora del rendimiento de las fuentes de potencia de modo conmutado, es el resultado directo de las altas frecuencias de conmutación utilizadas en los procesos de conversión de energía. Uno de los principales beneficios que se obtiene al aumentar la frecuencia de conmutación es la reducción del tamaño de los componentes de filtrado, lo que se traduce en una mayor eficiencia. De este modo, se logrará aumentar la eficiencia al mejorar su componente principal, el convertidor DC/DC.

Estudios posteriores [3], presentan el circuito del convertidor resonante como se muestra en la Figura 20. Es un circuito considerablemente más pequeño que los propuestos anteriormente, lo que permitirá reducir el almacenamiento de energía utilizando componentes pasivos de menor tamaño y valor.

Figura 20. Circuito del convertidor resonante DC-DC presentado por M. K. Kazimierczuk

En la actualidad, se está despertando un gran interés en el funcionamiento de convertidores de potencia a frecuencias de conmutación mayores a las que se usan normalmente (en el rango de cientos de KHz a unos pocos MHz). Al operar a mayor frecuencia es posible obtener una respuesta más rápida del convertidor a variaciones en la tensión de entrada o la carga, así como una mayor densidad superficial de potencia. Los especialistas en el área de Electrónica de Potencia buscan poder introducir todos los elementos de una fuente de potencia dentro de un mismo empaquetado (Power Supply in Package) o en un mismo chip (Power Supply on Chip).

#### 1.1. Elección de una topología para el convertidor

Como hemos explicado en la introducción de esta sección, el convertidor está formado por la combinación de un inversor clase E y un rectificador clase E síncrono. Para el diseño del convertidor, tendremos que elegir una topología que nos permita obtener las mejores prestaciones.

#### 1.1.1. Inversor clase E

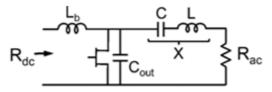

Figura 21. Inversor Clase E

Según hemos visto anteriormente, Lb se supone como una inductancia infinita, con el fin de considerar la rama del dispositivo de carga como una fuente de corriente continua. La red de salida con un alto factor de calidad como para asegurar que la corriente que lo atraviesa sea una sinusoide a la frecuencia de conducción.

Sintonizando el circuito LC resonante ligeramente por debajo de la frecuencia de conmutación, las condiciones óptimas para un inversor son las siguientes [4]:

$$D = 0.5 \tag{30}$$

$$R_{ac} = \frac{0.1836}{w \cdot C_{out}} \tag{31}$$

$$X = \frac{0.2116}{w \cdot C_{out}} \tag{32}$$

donde D es el ciclo de trabajo de conmutación, mientras que  $R_{ac}$  y X son las componentes real e imaginaria de la impedancia óptima de funcionamiento vista por el dispositivo (incluyendo la capacitancia) a la frecuencia fundamental.

En estas condiciones, se ha demostrado que el inversor es visto por su fuente de DC como una carga de valor:

$$R_{dc} = \frac{1}{\pi \cdot w \cdot C_{out}} \tag{33}$$

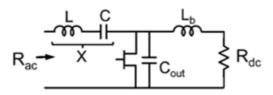

#### 1.1.2. Rectificador clase E

Figura 22. Rectificador Clase E

Las condiciones óptimas para el rectificador son las mismas que para el inversor, D, X, y  $R_{dc}$ , mientras que el desplazamiento de fase requerido  $\Delta \varphi$  entre puerta-fuente y drenador-fuente debe establecerse en 180° para obtener la sincronización deseada.

En el caso del rectificador, representa a la excitación en CA una carga resistiva de valor  $R_{\rm ac}$ .

#### 1.1.3. Convertidor resonante clase E<sup>2</sup>

Figura 23. Circuito básico del convertidor resonante clase E2 DC-DC

El convertidor DC/DC clase  $E^2$  es la formación en cascada de los dos circuitos descritos anteriormente. El rectificador da la carga  $R_{ac}$  requerida por el inversor de

forma que ambos puedan operar según las condiciones de funcionamiento ZVS y ZDS sin añadir ningún elemento adicional para la interconexión.

La combinación en serie de los dos circuitos resonantes formaría un circuito LC donde el valor de la reactancia debe ser:

$$2 \cdot X = \frac{0.4232}{w \cdot C_{out}} \tag{34}$$

Para un funcionamiento sin pérdidas, la tensión continua de salida sería igual al valor de polarización de entrada, mientras que la carga de DC ofrecida por el convertidor a su fuente de alimentación sería exactamente su resistencia de carga  $R_{\rm dc}$ . Todo esto es gracias a la simetría en la topología, ya que sin ella nada de esto sería posible, porque el inversor ofrece al rectificador la carga deseada y viceversa. Si no hubiese simetría, aunque uno de los dos ofrezca la carga correcta, el otro no podría ofrecer el valor correcto de carga. Con todo ello obtendríamos una impedancia al fundamental de:

$$Z_d(f) = R + 2 \cdot \left[ j \cdot w_s \cdot L - \frac{1}{j \cdot w_s \cdot C} \right] = \frac{0.18}{w_s \cdot C_s} + j \cdot \frac{0.42}{w_s \cdot C_s}$$

(35)

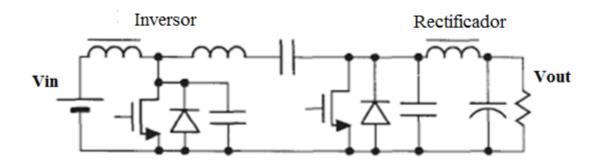

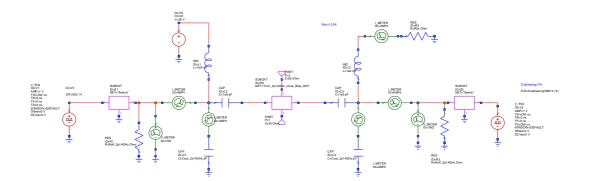

#### 2. Diseño de un convertidor DC/DC

Nos basaremos en los primeros estudios realizados a finales de los 80 sobre el uso de un convertidor resonante DC/DC en alta frecuencia. Uniremos dos amplificadores clase E, el primero funcionará como inversor, es decir, realizará el cambio de DC a AC, y el segundo como rectificador, efectuando el cambio de AC a DC nuevamente.

Una de las motivaciones de este proyecto es conseguir la implementación de ambas ramas en la misma placa, de tal forma que se obtenga mayor eficiencia que si se implementasen de manera independiente. Con ello conseguiríamos mejorar la rama AM del transmisor polar, y, por tanto, obtener mayor eficiencia total del conjunto. Es importante que el diseño que realicemos sea flexible y fiable, porque como ya sabemos no siempre obtenemos los mismos resultados en las simulaciones que en el laboratorio.

#### 2.1. Caracterización del transistor

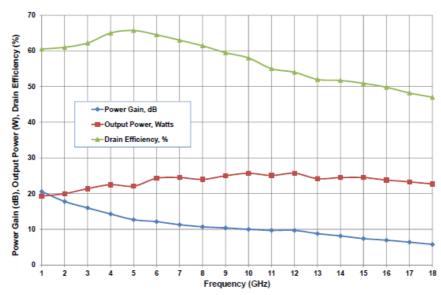

El convertidor está compuesto de dos transistores de alta eficiencia así como de elementos pasivos necesarios para formar las redes de adaptación, polarización, etc. Los transistores elegidos para la realización del convertidor son de GaN HEMT de Cree Inc, en concreto el modelo CGHV1J025. El uso de este tipo de transistores, en vez de otros, se explicó en la Sección III. Sus características más detalladas pueden consultarse en sus hojas de características en [5].

Figura 24. Ganancia, potencia de salida y eficiencia en drenador del CGHV1J025

Como podemos ver, de los valores que nos proporciona el fabricante en su datasheet (Figura 24), este tipo de transistor nos va a permitir una alta eficiencia en el drenador a la frecuencia a la que vamos a trabajar y una ganancia también elevada.

Para poder caracterizar el transistor, tendremos que aproximar su funcionamiento a un modelo, que permita estimar las condiciones de trabajo óptimas y su máximo rendimiento en operación clase E. Tendremos que obtener los valores de los parámetros que nos permitan cumplir las condiciones ZVS y ZDS.

#### Parámetros del modelo del transistor:

#### $\checkmark$ $C_{out}$ :

La capacidad de salida se puede estimar con el transistor en estado OFF. A baja frecuencia  $C_{out}$  no influye nada, lo que se tiene es un abierto ( $R_{OFF}$ ). Conforme aumenta la frecuencia se tiende al cortocircuito por el condensador.

Por debajo de la zona de pinch-off, valores de  $V_{GS} < V_P$ , el  $S_{22}$  es casi igual al ideal. En el momento que el transistor empieza a conducir, la conductancia de salida tiene un aumento significativo, esto nos indica que la admitancia de salida que está viendo el transistor ya no es solo debida a la capacidad sino también a una conductancia.

$$Y = G + j \cdot B \rightarrow C_{out} = \frac{B}{2 \cdot \pi \cdot f} = 1.965 pF$$

(36)

#### $\checkmark R_{OFF}$ :

Resistencia o parte real de la impedancia de salida del transistor (considerado como un equivalente paralelo  $R_{OFF}$  //  $C_{out}$  en su estado OFF) cuando su estado es abierto:

$$R_{OFF} = 1886 \,\Omega \tag{37}$$

$\checkmark$   $R_{ON}$ :

Resistencia del transistor cuando su estado es cerrado (ON):

$$R_{ON} = 0.61\Omega \tag{38}$$

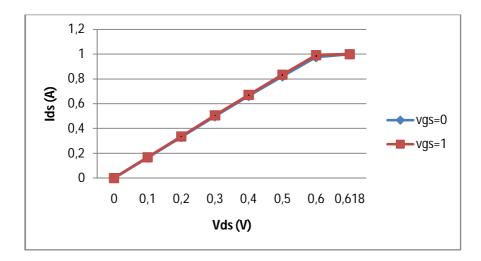

Se puede obtener de los parámetros S del transistor, pero es preferible sacarlo de las medidas I/V. Para ello, haremos un pequeño barrido de la tensión para  $V_{GS}=0$  v y  $V_{GS}=1$  v, obteniendo como era de esperar una  $R_{ON}\approx0.61\Omega$

| $V_{GS} = 0 \text{ v}$ | $V_{DS}(v)$ | $I_{DS}(A)$ |

|------------------------|-------------|-------------|

|                        | 0           | 0           |

|                        | 0,1         | 0,165       |

|                        | 0,2         | 0,332       |

|                        | 0,3         | 0,499       |

|                        | 0,4         | 0,663       |

|                        | 0,5         | 0,822       |

|                        | 0,6         | 0,977       |

|                        | 0.618       | 1           |

| $V_{GS}=1 \text{ v}$ | $V_{DS}(v)$ | $I_{DS}(A)$ |

|----------------------|-------------|-------------|

|                      | 0           | 0           |

|                      | 0,1         | 0,167       |

|                      | 0,2         | 0,336       |

|                      | 0,3         | 0,506       |

|                      | 0,4         | 0,672       |

|                      | 0,5         | 0,835       |

|                      | 0,6         | 0,993       |

|                      | 0,607       | 1           |

Figura 25. Curvas I/V del transistor para  $V_{GS}$ = 0v y  $V_{GS}$ = 1v, entre valores pequeños de  $V_{DS}$  (zona lineal)

#### Parámetros que ofrece el clase E:

#### $\checkmark R_{DC}$ :

Si el amplificador cumple con las condiciones de ZVS y ZDS, es visto por su fuente como una carga de valor  $R_{DC}$ :

$$R_{DC} = 12.98 \,\Omega \tag{39}$$

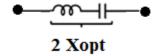

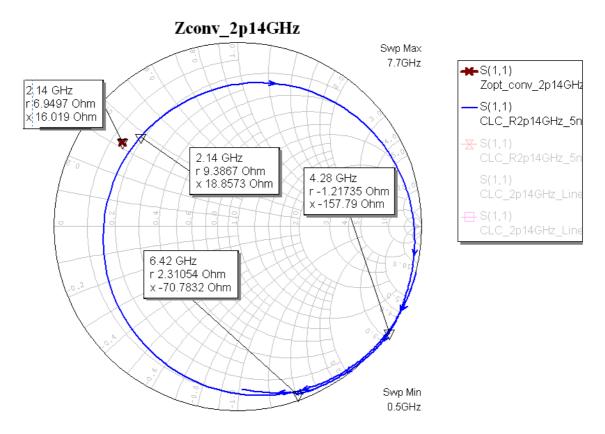

#### $\checkmark$ $Z_{opt}$ :

Impedancia óptima que debe ver el dispositivo a la frecuencia fundamental:

$$Z_{opt} = 8.095 + j \cdot 16.02 \,\Omega \tag{40}$$

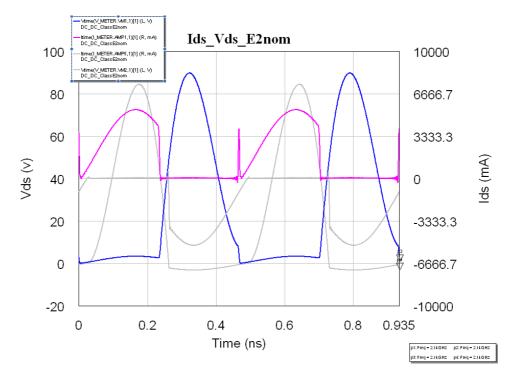

Una vez que tenemos los parámetros que cumplen las condiciones ZVS y ZDS, se evalúo el comportamiento del convertidor en términos de frecuencia de conmutación a través de simulaciones. A continuación mostraremos las formas de onda de corriente y tensión de drenador tanto del inversor como del rectificador, así como el esquemático utilizado para lograrlo.

Figura 26. Condiciones ZVS y ZDS del inversor y rectificador

Como se puede observar en la figura anterior, dónde están superpuestos el comportamiento de ambos transistores, son formas invertidas con respecto al tiempo. Cuando un transistor se encuentra en su estado de conducción, el otro no lo está y viceversa. Las condiciones de ZVS y ZVDS también se pueden apreciar en las transiciones del inversor de OFF a ON y en el rectificador de ON a OFF.

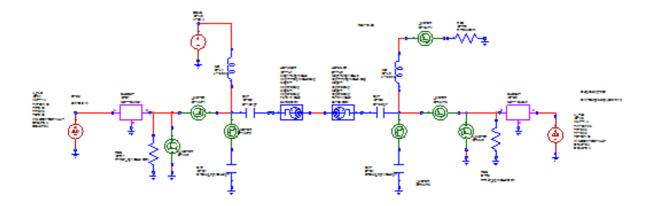

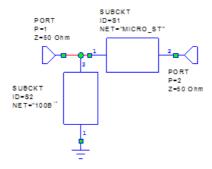

Figura 27. Esquemático empleado para observar las condiciones ZVS y ZDS

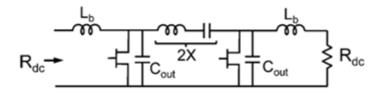

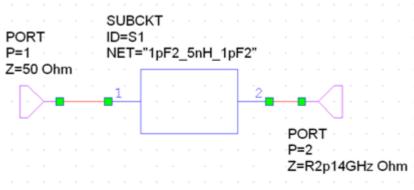

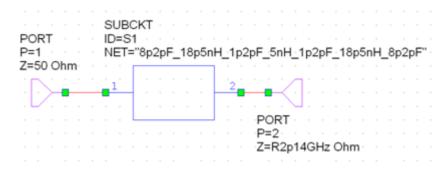

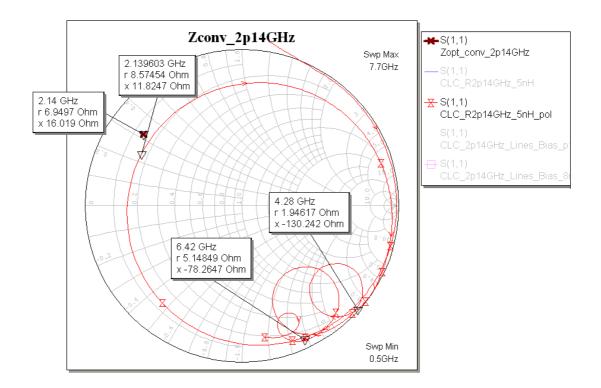

#### 2.2. Diseño de la red de interconexión [6]

En trabajos realizados con anterioridad se diseñó una red de interconexión multiarmónica para terminar cada uno de los armónicos, en nuestro caso se continúa con el objetivo de simplificar las redes lo más posible buscando el comportamiento óptimo con una red de una sola bobina autoresonante y ajustándose la capacidad cuidadosamente para proporcionar la reactancia deseada de 2.X [7] [8].

Figura 28. Red de interconexión básica del convertidor

El circuito debe guardar simetría ya que en ella se basa en funcionamiento del convertidor, el inversor ofrece al rectificador la carga deseada y viceversa, si no hubiese simetría aunque uno de los dos ofrezca la carga correcta al otro éste no podría ofrecer el valor correcto de carga.

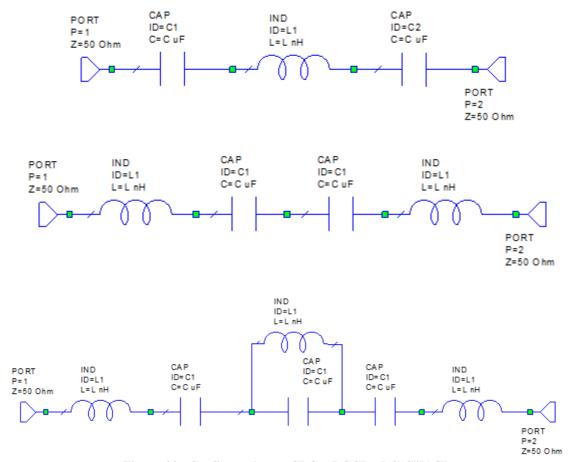

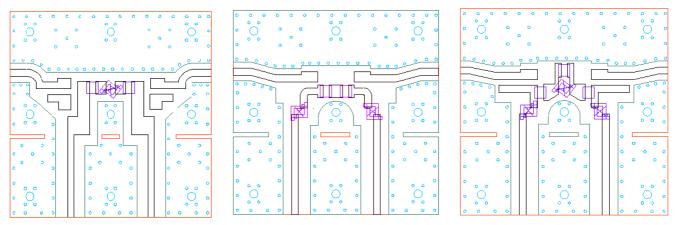

Diseñamos 3 tipos diferentes de configuraciones posibles que fueran simétricas, el por qué de hacer tres era poder probar en el laboratorio las tres y elegir la mejor. En la sección de medidas explicaremos cuál escogimos.

Figura 29. Configuraciones: CLC - LCCL - LC(C||L)CL

#### 2.3. Diseño de la red de polarización

A continuación, tendremos que diseñar la red de polarización de puerta y drenador de nuestro convertidor. Esta red nos servirá para limitar el tipo de señal que circula por nuestro circuito, ya que estamos trabajando con alterna y continua. Concretamente, evitaremos que por la rama de entrada y de salida de continua (por la que circulan  $v_{DC}$  y  $v_{OUT}$ ) tengamos señal de RF y por las ramas de RF (entrada o excitación de las puertas o interconexión de los drenadores) tengamos señal de continua.

Como sabemos, el funcionamiento ideal de estas redes es que los condensadores y bobinas en continua se comporten como circuito abierto y cortocircuitos respectivamente, mientras que en alterna tengan justo el funcionamiento contrario. Pero esto realmente nunca sucede ya que los componentes no son ideales.

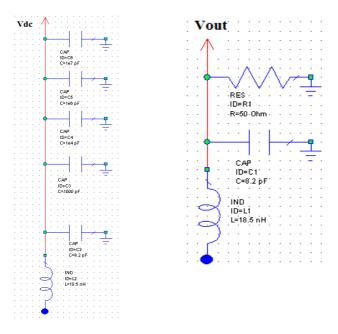

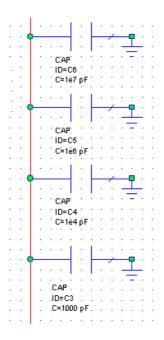

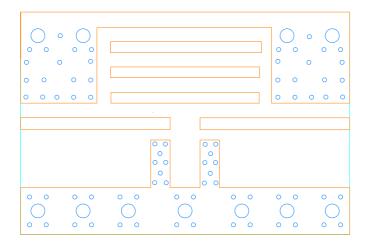

#### 2.3.1. Polarización del drenador

Para la polarización del drenador elegiremos unos valores de condensadores y bobinas que resuenen a una frecuencia lo más próxima posible a nuestra frecuencia de funcionamiento. Esto nos permitirá eliminar la señal de RF que pudiéramos tener en la

rama del diseño que queramos. Para seleccionar los valores más convenientes lo mejor es hacer una medida en el laboratorio, pero a priori elegiremos como mejor condensador uno de 8,2pF de ATC de la serie 100B y una bobina de 17,5nH o 18,5 nH de Coilcraft de la serie Mini que resuenan a 2,2GHz y 2,5 GHz respectivamente.

Figura 30. Red de polarización del drenador para la entrada (v<sub>DC</sub>) y salida (v<sub>OUT</sub>) de continua