# ESCUELA TÉCNICA SUPERIOR DE INGENIEROS INDUSTRIALES Y DE TELECOMUNICACIÓN

#### UNIVERSIDAD DE CANTABRIA

# Proyecto Fin de Grado

Implementación de la metodología de verificación UVM en Vivado para diseños digitales.

Implementation of Universal Verification Methodology UVM on Vivado for digital desings.

Para acceder al Título de

# GRADUADO EN INGENIERÍA ELECTRÓNICA INDUSTRIAL Y AUTOMÁTICA

**Autor: Juan Camilo Martínez Uribe**

Septiembre – 2025

#### Resumen

El proyecto aborda el aprendizaje e implementación de la metodología estándar de verificación UVM (Universal Verification Methodology) en el entorno Vivado para realizar la verificación funcional de un módulo digital generador de ondas de radiofrecuencia. Para ello fue necesario también aprender el lenguaje de descripción hardware SystemVerilog que permite la programación orientada a objetos en la que se apoya UVM. El sistema de verificación permitió ejecutar pruebas configurables con las que se detectaron errores varios de precisión en el módulo y su caracterización, comprobando que UVM es un acercamiento robusto y eficaz para la verificación de diseños digitales.

#### **Abstract**

The project addresses the learning and implementation of the standard verification methodology UVM (Universal Verification Methodology) in the Vivado environment to perform the functional verification of a digital radiofrequency waveform generator module. For this purpose, it was also necessary to learn the SystemVerilog hardware description language, which allows the object-oriented programming that UVM relies on. The verification system allowed to perform configurable tests that revealed several precision errors on the module and its characterization, demonstrating that UVM is a robust and effective approach to digital designs verification.

# **Índice General**

| 1 | MEMORIA     | 4  |

|---|-------------|----|

|   |             |    |

| 2 | PRESUPUESTO | 81 |

| _ |             |    |

| 3 | CODIGO      | 86 |

# 1 MEMORIA

# **Índice de Memoria**

| l | MEMO           | RIA                                                     | 4   |

|---|----------------|---------------------------------------------------------|-----|

|   | 1 1 IN         | roducción                                               | 7   |

|   | 1.1.1          | Objetivos                                               |     |

|   | 1.1.2          | Alcance                                                 |     |

|   | 1.1.3          | Estructura del documento                                |     |

|   |                | TADO DEL ARTE                                           |     |

|   | 1.2.1          | Verificación de diseños hardware                        |     |

|   | 1.2.2          | Métodos de verificación anteriores                      |     |

|   | 1.3 CC         | NOCIMIENTOS PREVIOS                                     |     |

|   | 1.3.1          | SystemVerilog                                           |     |

|   | 1.3.2          | UVM                                                     |     |

|   | 1.4 IMI        | PLEMENTACIÓN DEL SISTEMA DE VERIFICACIÓN                | 20  |

|   | 1.4.1          | Esquema general                                         |     |

|   | 1.4.2          | DUT                                                     |     |

|   | 1.5 IMI        | PLÉMENTACIÓN DEL ENTORNO                                | 26  |

|   | 1.5.1          | Top                                                     |     |

|   | 1.5.2          | Entorno                                                 |     |

|   | 1.5.3          | Agente puerto de entrada                                |     |

|   | 1.5.4          | Agente puerto de salida                                 | 29  |

|   | 1.5.5          | Agente reloj                                            | 29  |

|   | 1.5.6          | Modelo de referencia                                    |     |

|   | 1.5.7          | Marcador                                                |     |

|   | 1.5.8          | Cobertura                                               |     |

|   | 1.6 IMI        | PLEMENTACIÓN DEL BANCO DE PRUEBAS                       |     |

|   | 1.6.1          | Planteamiento del test                                  |     |

|   | 1.6.2          | Configuración de test.                                  |     |

|   | 1.6.3          | Secuencia de agente de puerto de entrada                |     |

|   | 1.6.4          | Secuencia de agente reloj                               |     |

|   | 1.6.5          | Llamada a test configurado                              |     |

|   | 1.6.6<br>1.6.7 | Parámetros de cobertura                                 |     |

|   | 1.6.7          | Simulación Vivado                                       |     |

|   | 1.6.9          | Tras la simulación                                      |     |

|   | 1.6.10         | Test compuesto                                          |     |

|   |                | SULTADOS Y ANALISIS                                     |     |

|   | 1.7.1          | Errores detectados durante el proceso de implementación |     |

|   | 1.7.1          | Resultados de la prueba final                           |     |

|   |                | NCLUSIONES                                              |     |

|   |                | BLIOGRAFÍA                                              | _   |

|   | i.a Dic        |                                                         | / 9 |

# Índice de figuras

| Figura 1 - Fases de UVM                                                                | 14 |

|----------------------------------------------------------------------------------------|----|

| Figura 2 - Árbol jerárquico de las clases de UVM                                       |    |

| Figura 3 - Puertos TLM                                                                 |    |

| Figura 4 - Resumen del sistema de mensajes de UVM                                      |    |

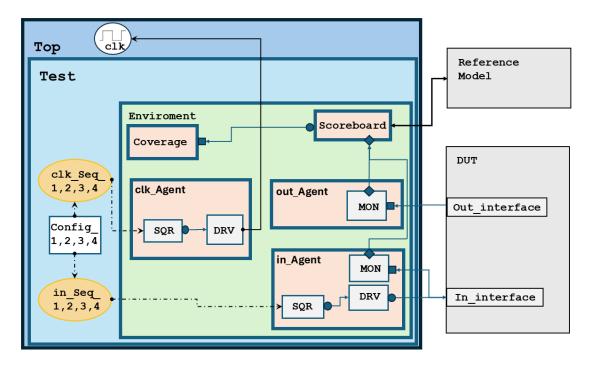

| Figura 5 - Estructura básica de un sistema UVM                                         |    |

| Figura 6 - Estructura del sistema de verificación implementado                         |    |

| Figura 7 - Intervalo de repetición de pulsos                                           |    |

|                                                                                        |    |

| Figura 8 - Chirp en modulación IQ                                                      |    |

| Figura 9 - Tono en modulación IQ                                                       |    |

| Figura 10 - Secuencia de rampas                                                        |    |

| Figura 11 - Estructura de la interfaz del puerto de entrada del DUT                    | 27 |

| Figura 12 - Fase de ejecución del controlador del agente de entrada                    |    |

| Figura 13 - Fase de ejecución del monitor del agente de entrada                        |    |

| Figura 14 - Manejo de estados del modelo de referencia                                 |    |

| Figura 15 - Estado WAIT_FOR_PARAM del modelo de referencia                             |    |

| Figura 16 - Estado WAVE_GEN del modelo de referencia                                   | 32 |

| Figura 17 - Cálculo de las ondas en el modelo de referencia                            | 33 |

| Figura 18 - Fase de ejecución del marcador                                             | 35 |

| Figura 19 - Detección de desincronización                                              | 35 |

| Figura 20 - Manejo de estados del acumulador de errores                                | 36 |

| Figura 21 - Estructura del acumulador de errores                                       |    |

| Figura 22 - Informe final de la verificación por terminal                              |    |

| Figura 23 - Conteo de errores para histograma                                          |    |

| Figura 24 - Manejo del muestreo para cobertura                                         |    |

| Figura 25 - Diferentes retrasos de señal aleatorizados                                 |    |

| Figura 26 - Restricción de aleatorización condicionada                                 |    |

| Figura 27 - Varios rangos de aleatorización para un mismo registro                     |    |

| Figura 28 - Mensaje de resumen de la configuración seleccionada previa al test         |    |

| Figura 29 - Mensaje de resumen de configuración distinta                               |    |

| Figura 30 - Gestión de restricciones contradictorias                                   |    |

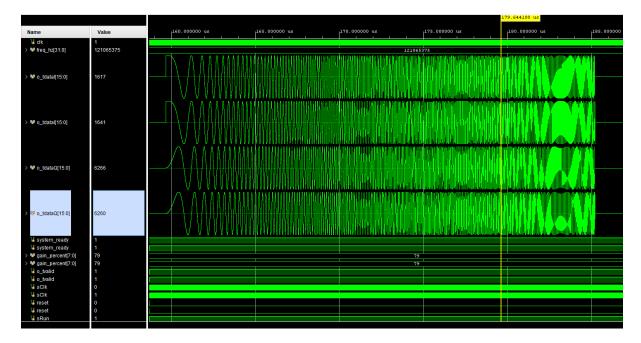

| Figura 31 - Visión general de simulación de formas de onda en Vivado                   |    |

| Figura 32 - Aleatorización de intervalo entre resets                                   |    |

| Figura 33 - Restricciones de aleatorización de periodo del reloj generado              |    |

| Figura 34 - Discrepancia entre frecuencia generada e indicada                          |    |

|                                                                                        |    |

| Figura 35 - Generación del reloj y su recalculación                                    |    |

| Figura 36 - Fase de construcción del test                                              |    |

| Figura 37 - Fase de ejecución del test                                                 |    |

| Figura 38 - Rangos de aleatorización junto a los selectores en el objeto configuración |    |

| Figura 39 - Ejemplo de estructura de los puntos de cobertura.                          |    |

| Figura 40 - Paquete de lista de tests                                                  |    |

| Figura 41 - Paquete del entorno                                                        |    |

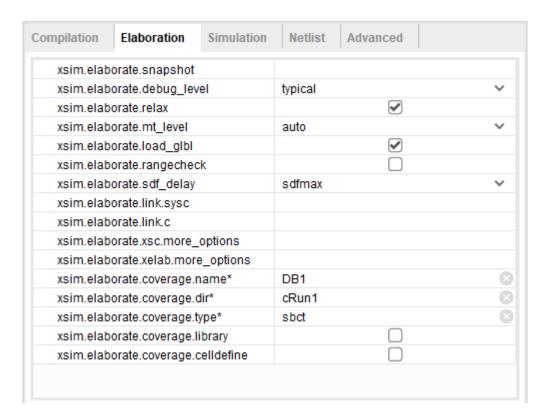

| Figura 42 - Configuración de elaboración de la simulación en Vivado                    |    |

| Figura 43 - Jerarquía de fuentes de simulación en Vivado                               |    |

| Figura 44 - Interfaces a las que se tiene acceso en la simulación de Vivado            |    |

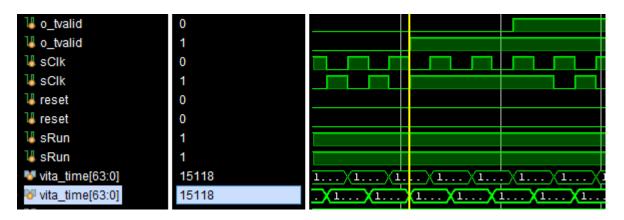

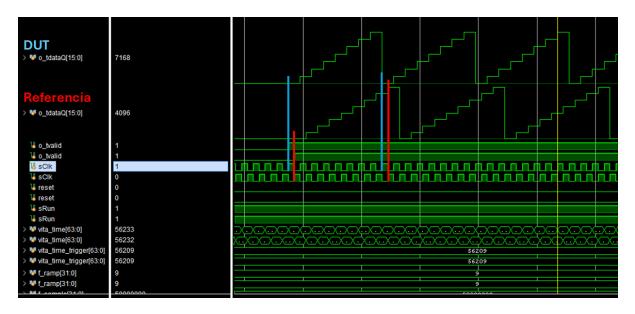

| Figura 45 - Registros del DUT y modelo real                                            |    |

| Figura 46 - Resumen de mensajes generados por entorno UVM tras la simulación           |    |

| Figura 47 - Generación y resumen de cobertura de código                                |    |

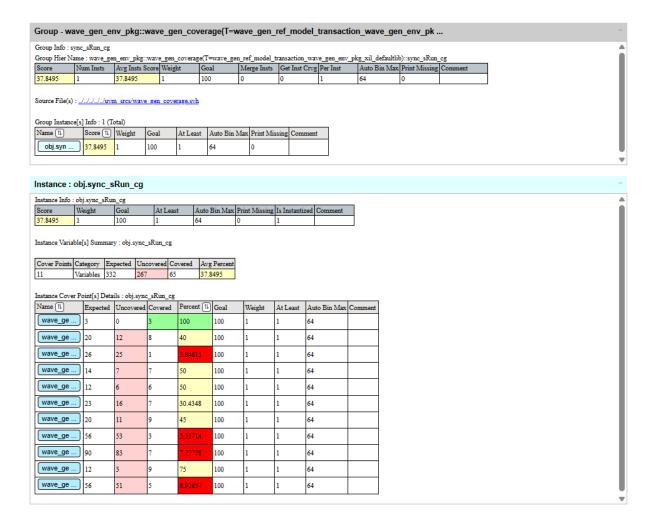

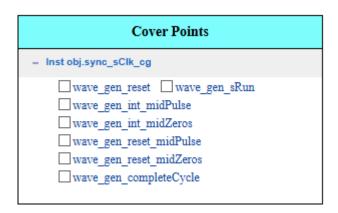

| Figura 48 - Generación de cobertura funcional                                          | 61 |

| Figura 49 - Informe de un grupo de cobertura                                           | 62 |

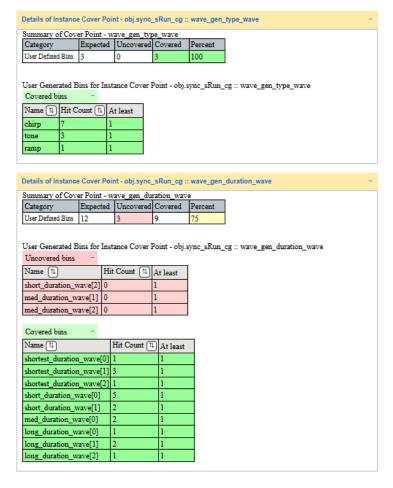

| Figura 50 - Informe de puntos de cobertura con bins individuales                       | 63 |

| Figura 51 - Estructura del test largo                                                 | . 64 |

|---------------------------------------------------------------------------------------|------|

| Figura 52 - Fase de ejecución del test largo                                          | . 65 |

| Figura 53 - Desincronización entre DUT y modelo de referencia                         | . 66 |

| Figura 54 - No transmisión del reloj al modelo de referencia para resincronizar el    |      |

| comportamiento                                                                        | . 66 |

| Figura 55 - Error de número de muestras en la generación de rampas                    | . 67 |

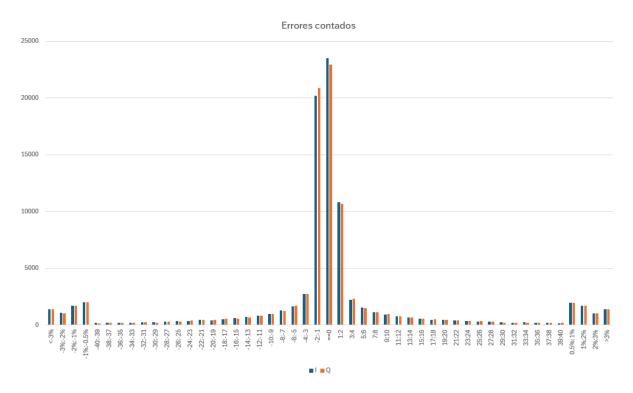

| Figura 56 - Histograma de errores en una prueba con los 3 tipos de onda               | . 68 |

| Figura 57 - Errores altos en una prueba con los 3 tipos de onda                       | . 68 |

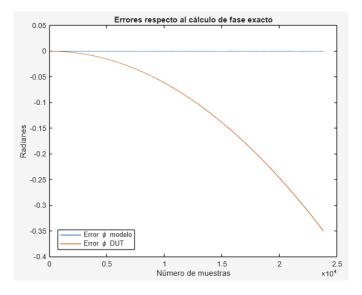

| Figura 58 - Error acumulativo en el cálculo de la fase del chirp                      | . 69 |

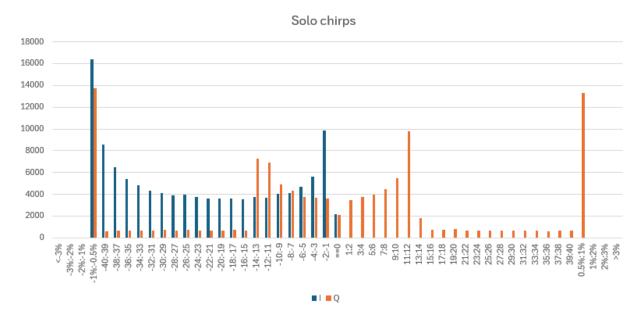

| Figura 59 - Histograma de errores de solo chirps tras la corrección del error de fase | 70   |

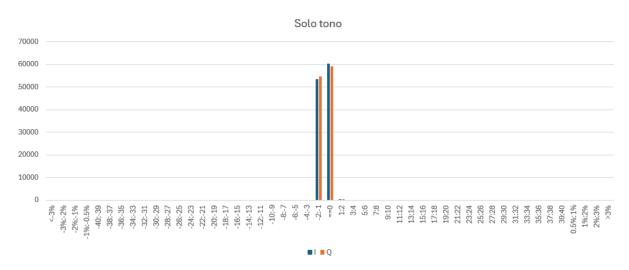

| Figura 60 - Histograma de solo tonos final                                            | 71   |

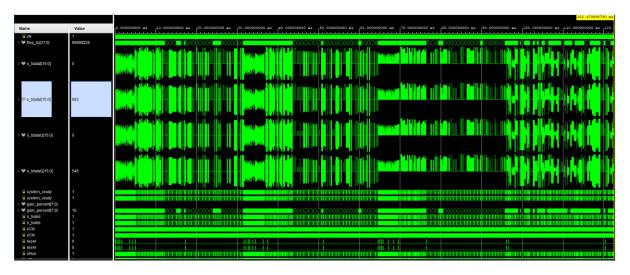

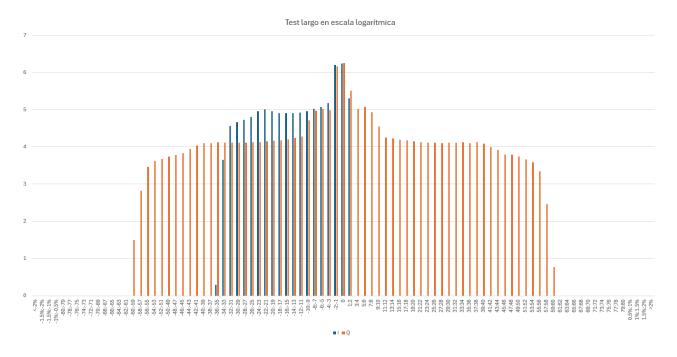

| Figura 61 - Simulación de verificación completa                                       | 72   |

| Figura 62 - Histograma de la prueba larga en escala logarítmica                       | 72   |

| Figura 63 - Resumen del informe de cobertura funcional                                | 73   |

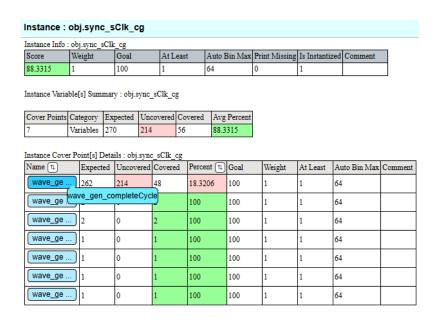

| Figura 64 - Puntos de cobertura muestreados cada ciclo de reloj                       | 73   |

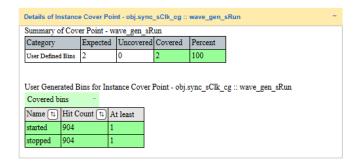

| Figura 65 - Punto de cobertura de la señal sRun                                       | 74   |

| Figura 66 - Informe del grupo de cobertura sync_sClk_cg completo                      | 74   |

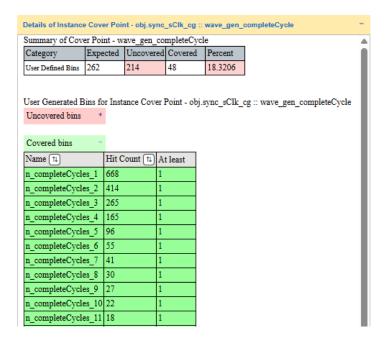

| Figura 67 - Punto de cobertura de ciclos de generación de señal completados           | 75   |

| Figura 68 - puntos de cobertura muestreados cada reconfiguración de señal             | 75   |

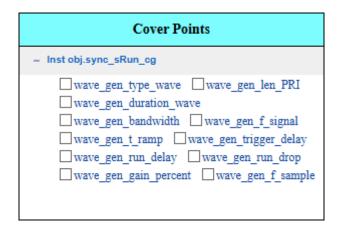

| Figura 69 - Resumen de puntos de cobertura de sync_sRun_cg                            | 76   |

| Figura 70 - Bins no cubiertos del punto de cobertura asociados a f_signal             | 76   |

| Figura 71 - Bins no cubiertos del punto de cobertura asociados a sRun_delay           | . 77 |

| Figura 72 - Bins no cubiertos del punto de cobertura asociado a f_sample              | . 77 |

# 1.1 INTRODUCCIÓN

La verificación es una parte importante en el diseño de sistemas digitales complejos, que progresivamente ha ido suponiendo una parte más significativa del presupuesto de un sistema digital. Su propósito es comprobar que el diseño opere de la forma esperada dentro de los parámetros para los que fue diseñado. Conforme un diseño se hace más complejo, el tratar de comprobar todas sus partes se hace inviable desde un punto de vista económico, por la necesidad de tener que implementar un banco de pruebas específico para cada funcionalidad del diseño a probar. Para ello se han ido desarrollando diferentes metodologías para simplificar el proceso de verificación optimizando todo el proceso. En este proyecto se implementa la metodología UVM, desarrollada en 2011 por Accellera basándose ampliamente en la metodología VMM/OVM, en la que ya estaba definida buena parte de la estructura que implementa la metodología (ambiente, agentes, monitores...) estandarizándola como una librería de clases base de SystemVerilog para facilitar su implementación. Si bien la metodología sique recibiendo soporte hoy en día, siendo la última versión la UVM v2020.3.1 lanzada en agosto de 2024, en el proyecto se usará la versión UVM v1.2 lanzada en 2014 ya que es la versión de la librería incluida en la suite de Vivado v2024.2 utilizada en el proyecto.

# 1.1.1 Objetivos

El objetivo final del proyecto es comprobar el correcto funcionamiento del módulo generador de ondas de radiofrecuencia.

Para ello se implementará un entorno de verificación que incluirá también un modelo de referencia con el que se comparará no solo el comportamiento general del módulo si no también la precisión de las ondas generadas frente a un modelo más cercano a lo ideal.

Se implementarán diferentes pruebas orientadas a diferentes comportamientos del módulo para orientar cada prueba individual de manera más precisa, esto es importante considerando que en una implementación básica de la metodología los estímulos son aleatorios, por lo que controlar la aleatoriedad es vital si, como es el caso, se trabaja principalmente con pruebas cortas individuales.

#### 1.1.2 Alcance

Se implementó un sistema de verificación que consta del manejo de señales a Nivel de Transferencia de Registros, un registro de errores respecto al modelo de referencia y un registro de diferentes secuencias de estímulos de entrada para comprobar que el objetivo de cada prueba individual ha sido realmente cubierto.

Para flexibilizar las pruebas individuales se implementó una prueba configurable que permitió realizar diferentes pruebas orientadas a comportamientos específicos, esto facilitó la repetibilidad de los diferentes errores encontrados para así poder aislar su causa.

Una vez implementado el sistema de verificación, junto a la prueba configurable, se hicieron múltiples pruebas orientadas a la detección de diferentes posibles errores. Se usaron diferentes métricas de verificación con la que se caracterizaron los límites del diseño hardware.

# 1.1.3 Estructura del documento

En este documento se cubre en una primera parte: un breve repaso de la historia de la verificación funcional de diseños hardware junto a su importancia, una explicación de la metodología de verificación UVM y la necesidad del uso del lenguaje SystemVerilog para la implementación de la metodología. Una vez considerados los conocimientos previos necesarios para la implementación del sistema, se hará una explicación de cada componente del sistema considerando dos partes fundamentales: el entorno, que es fijo entre pruebas y el banco de pruebas, que define el comportamiento de cada prueba individual. Por último, se tratará con los resultados de diferentes pruebas en los que se comentará diferentes errores hallados por el sistema de verificación que pudieron ser corregidos del todo o mejorados dentro de un rango.

## 1.2 ESTADO DEL ARTE

La verificación es un proceso necesario que idealmente se produce de manera concurrente al diseño del módulo a verificar. Para un diseño muy sencillo se puede realizar un banco de pruebas que compruebe todas sus posibles interacciones y esto sería suficiente para considerarlo verificado. Pero una vez la complejidad de los diseños comienza a incrementar se hace insostenible este acercamiento a la verificación y se hace evidente la necesidad de herramientas especializadas para este proceso.

Un caso famoso que muestra la importancia de una verificación robusta es el del Error de División del Intel Pentium. Este afectó a los primeros procesadores Pentium en 1994. El error sucedía por el algoritmo usado para aumentar la velocidad de cálculo de divisiones en coma flotante, en el que ciertos valores en una look-up table no estaban correctamente definidos por lo que los resultados que daba eran erróneos. Este error acabo por costarle a Intel un total de 475 millones de dólares en varias demandas y el reemplazo de los procesadores afectados. Tras esta resolución Intel se vio forzado a implementar una verificación más robusta, para esto colaboraron con academia en lo que sería la implementación de Verificación Formal, ámbito puramente matemático, a la verificación de circuitos. Iterando sobre esta idea es que finalmente se llegaría a la creación de un lenguaje de especificación formal llamado ForSpec, el cual sería cedido a Accellera e influenciaría la creación de SystemVerilog Assertions (SVA), un subset de SystemVerilog centrado en la detección de eventos bajo diferentes secuencias en las señales de un módulo.

Si bien ese error no es más que un incidente ocasionado por una verificación insuficiente, es uno que afectó de manera masiva a un público más generalizado y sirvió como una motivación en la inversión al desarrollo del campo de la verificación.

#### 1.2.1 Verificación de diseños hardware

La verificación de diseños hardware podría decirse que comenzó con la posibilidad de simulación de los diseños en sí, el primer estándar al respecto fue la tecnología SPICE (Simulation Program with Integrated Circuits Emphasis en inglés) en la década de los 70, en la que se implementaron varías tecnologías para diferentes tipos de simulaciones en un software libre que fue rápidamente adoptado por la industria.

Para diseños más complejos se necesitaba simulaciones a nivel de puertas lógicas. Cada gran fabricante llegó a desarrollar sus propios simuladores específicos. La tecnología siguió avanzando hasta llegar a la creación del lenguaje Verilog, que permitía describir hardware con diferentes niveles de abstracción en 1985, el cual no llegaría a ser un estándar IEEE hasta 1995. Durante esa década el foco del desarrollo de técnicas de verificación fue cambiando de ser únicamente la simulación a la metodología implementada.

Los componentes ya habían aumentado su complejidad lo suficiente como para que no resultase viable una simulación directa de toda su funcionalidad por lo que se exploraron diferentes formas de acelerar el proceso. Entre ellas la orientación de la simulación o la consideración de métricas de cobertura, de entre las cuales destacó la cobertura de código,

especialmente útil si el diseño es una caja blanca o la cobertura funcional, aplicable a cualquier diseño.

#### 1.2.2 Métodos de verificación anteriores

Una vez establecido el lenguaje SystemVerilog en 2005 y centrándose únicamente en los predecesores inmediatos a la metodología UVM, es notable que UVM fue desarrollado a raíz de múltiples tecnologías en uso en industria. Adopta conceptos de AVM (Advanced Verification Methodology) de Siemens EDA, OVM (Open Verification Methodology) de Siemens EDA y Cadence, VMM-RAL (Verification Metodology Manual – Register Abstraction Layer) y tecnologías sueltas de Mentor como lo pueden ser TLM2 (Transaction Level Model) y Phasing (Fases de verificación).

De entre ellos podemos destacar dos de esas influencias.

#### **VMM-RAL**

Verification Metodology Manual surgió como un intento en estandarizar el proceso de verificación en 2005. Propuso estandarizar diversos componentes de verificación en pos de la reutilización de entornos usando el reciente lenguaje estándar de SystemVerilog, cuando hasta el momento era común que cada proveedor utilizase un lenguaje concreto que se ajustase a sus necesidades específicas.

Al igual que lo estaría UVM, estaba desarrollado como una librería de clases SystemVerilog, si bien no compartía la estructura del sistema que propone UVM, los principios básicos son los mismos: Un entorno reutilizable en el que verificar el funcionamiento de un diseño hardware de manera automatizada.

Tiene especial foco en el uso de aserciones en buena parte de la estructura del sistema de verificación y propone el uso de la cobertura en la prueba no solo como parte del análisis tras la prueba si no para orientar los estímulos generados durante la prueba. Dicho esto, su principal aportación a lo que más tarde sería UVM fue el diseño de componentes del sistema basado en interfaces, lo que significó un paso hacia la modularización del diseño de sistemas de verificación.

#### OVM

Open Verification Methodology fue lanzado en 2008, siendo el precursor directo a UVM, ya integra varias de las características que acabarían definiendo UVM: su acercamiento a

verificación a través de la programación orientada a objetos, la posibilidad de parametrizar dichos objetos para facilitar cambios en el entorno de verificación, la ejecución por fases para estandarizar la estructura de la programación, etc.

En una primera versión de UVM, la metodología que propone es prácticamente idéntica a la versión en el momento de OVM. El cambio de nombre vino por cuestión de propiedad de la metodología. OVM pertenecía a Cadence como proyecto de código abierto y era necesario fijar las características de la metodología para poder establecer un estándar que pudiese ser usado en la industria.

Durante años OVM fue usada como la metodología por defecto para verificación, pero tras la estandarización de UVM y la adquisición de la propiedad de OVM por Accellera, el soporte tras OVM, es decir, sus recursos de aprendizaje online y foros de discusión han sido sustituidos por UVM.

#### 1.3 CONOCIMIENTOS PREVIOS

Para la implementación de la metodología es necesario conocer tanto la metodología en si como el lenguaje en el que se apoya.

# 1.3.1 SystemVerilog

SystemVerilog es un lenguaje de descripción y verificación hardware estandarizado en la IEEE 1800 por Accellera en 2005, misma organización que estandarizó la metodología UVM.

Sus características principales pueden ser agrupadas en dos roles

- SystemVerilog para Transferencia a Nivel de Registros (RTL en inglés), que es una extensión de Verilog para diseños sintetizables.

- SystemVerilog para Verificación, incluye características de programación orientada a objetos (OOP en inglés) que, si bien no son necesariamente sintetizables, son útiles para el desarrollo de bancos de prueba.

Para su uso en la metodología UVM se utiliza principalmente sus características de verificación. Algunas de sus características más relevantes a la metodología son:

- Técnicas de programación orientada a objetos que permiten la creación de entornos complejos de verificación dividiendo el proceso en diferentes módulos que están orientados a ser reutilizados.

- Acceso a diferentes métricas de cobertura como lo pueden ser las aserciones (mediante SVA), que puede comprobar que sucedan, o no, eventos definidos por el usuario durante toda la duración de la prueba y los grupos de cobertura que funcionan de manera similar, pero tienen que ser muestreados explícitamente dentro del código.

- Aleatorización condicionada, lo que permite un gran número de posibles casos de prueba además de permitir la creación de pruebas más orientadas para hacer más hincapié en posibles casos limite.

- Posibilidad de agrupar señales en interfaces para asegurar que la transmisión de datos entre registros se produzca de manera sincronizada, este resultó ser un punto particularmente importante de cara a la simulación en vivado.

# 1.3.2 UVM

UVM, Universal Verification Methodology en inglés, es un estándar establecido por Accellera Systems Initiative para unificar los diferentes acercamientos a la verificación de diseños hardware en uso en industria en el momento.

La metodología en sí está implementada como una librería de clases base con las que se instancia el banco de pruebas, estas clases aseguran la ejecución en un orden especifico de las diferentes fases y subfases de la prueba. La utilidad radica en lo modular de su diseño que permite la reutilización, con mínimos cambios, de algunas de estas partes y en la flexibilidad para implementar diferentes comportamientos.

#### Fundamentos de UVM

Una simulación de verificación completa se compone de tres partes principales, el entorno, que es fijo entre diferentes pruebas, el banco de pruebas, que establece el comportamiento que se busca obtener en la prueba y el diseño sobre el que se realiza la prueba. La metodología UVM describe cómo tiene que estar creadas las primeras dos partes y la conexión con el diseño.

#### **Fases UVM**

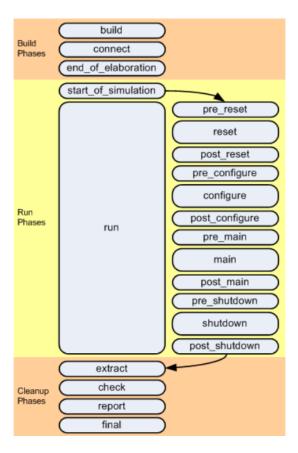

Una de las formas en las que la metodología UVM estandariza el proceso de implementación de un sistema de verificación es a través de su sistema de fases. La metodología considera 3 fases principales: construcción, ejecución y limpieza, ilustradas en la figura 1. El manejo de fases ocurre principalmente de manera interna en el sistema con la excepción de la fase de ejecución para que sea el usuario el que controle el final de la prueba.

En la fase de construcción se inicializa, configura y conecta todo el entorno. Este proceso ocurre en orden top to bottom, está orientado para que sean los componentes en capas exteriores los que apliquen las configuraciones necesarias a sus respectivos componentes internos. En esta fase también se crean todos los puertos TLM (Transaction Level Modeling) con los que están conectados los componentes que ocurre en orden bottom-up. Todo esto ocurre en tiempo 0 de simulación.

En la fase de ejecución comienza la comunicación con el módulo. Consiste en un reset del módulo, configuración de este de ser necesario, la generación de estímulos de la prueba y un corto periodo para asegurar que los efectos de los estímulos generados se han llegado a propagar por todo el sistema. La metodología también integra ganchos antes y después de cada una de estas subfases para facilitar la comunicación con el módulo en determinados

momentos de la prueba en caso de ser necesario, como también permite la inclusión de fases creadas por el usuario, aunque no es recomendable porque limita la reutilización del entorno.

Para esta fase es relevante conocer que el manejo de fases se realiza con objeciones, que son esencialmente banderas que indican si una fase ha acabado. En una implementación básica el usuario tiene que levantar explícitamente una de estas banderas al iniciar la secuencia de estímulos y bajarla al acabar la secuencia.

Finalmente está la fase de limpieza, en la que se extrae la información recolectada en la prueba, se establece si la prueba ha sido superada y se crea un informe de la verificación.

Figura 1 - Fases de UVM

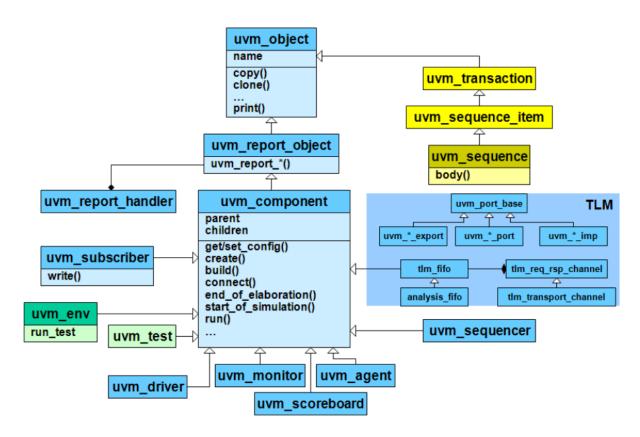

#### Jerarquía de clases

Los componentes UVM tienen definidos todos los métodos necesarios para el manejo interno del entorno junto a la comunicación entre componentes. Para usarlos basta con crear las clases necesarias para la implementación del entorno de verificación y, respetando las funciones que separan las fases, definir las funcionalidades específicas. Para implementar un entorno básico basta con extender dichas clases de los niveles más exteriores de la jerarquía, ilustrada en la Figura 2.

Figura 2 - Árbol jerárquico de las clases de UVM

#### **TLM**

La metodología UVM utiliza el modelado a nivel de transacciones para la comunicación entre componentes, que a diferencia de una comunicación RTL, Register Transfer Level, tradicional, empaqueta cada transmisión de datos en una única transmisión en lugar de cada uno de sus registros por separado lo cual podría llegar a ser mucho más demandante desde un punto de vista de recursos de computación. Esto puede llegar a ser importante de tener en cuenta dependiendo de la velocidad con la que tenga que interactuar con el módulo, en

concreto si llega a ser necesaria la implementación de FIFOS u otro método de arbitraje de transmisión de datos.

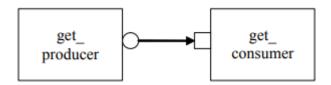

Este estándar establece el uso de dos tipos de puertos, los que inician transacciones, port, y los que no, export, representados comúnmente en diagramas como círculos y cuadrados respectivamente tal como se muestra en la Figura 3.

Tienen métodos orientados a usarse en la comunicación con el módulo, que son bloqueantes, y también métodos orientados a comunicaciones de análisis que son no bloqueantes.

Para utilizar las lecturas no bloqueantes es necesario poner las transacciones de análisis en puertos de análisis, además estos puertos permiten la comunicación con varios componentes a la vez.

Figura 3 - Puertos TLM

#### Mecanismos de configuración

UVM permite dos mecanismos de configuración, factory y base de datos. El mecanismo de factory permite de definición de componentes en la raíz de UVM que después pueden ser reemplazados entre sus equivalentes sobrescribiendo la definición dentro de otro componente, este acercamiento permite la instanciación de distintos tests con cambios mínimos en el código, utilizando handlers genéricos.

La base de datos permite configuración de un componente a otro sin importar si está dentro de su alcance. Son datos tanto de lectura como escritura, por lo que se puede cambiar la configuración durante la ejecución haciendo así una prueba dinámica. Si se utiliza como un configurador estático, su valor se sobrescribe al que haya sido inicializado dentro del propio componente, lo que permite la parametrización de una prueba.

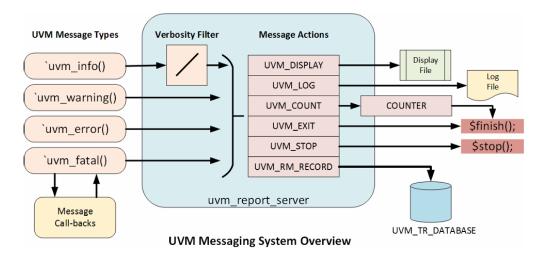

#### Gestión de mensajes

La metodología UVM maneja la gestión de mensajes a usuario dividiéndolos en 4 tipos de mensaje: info, warning, error y fatal. El sistema tiene algunas condiciones en las que imprime un mensaje en caso de que la construcción o conexión del entorno haya fallado, pero está orientado que sea el usuario el que defina los mensajes que considere necesario.

Figura 4 - Resumen del sistema de mensajes de UVM

Por defecto, un mensaje de fatal termina la simulación, un error la detiene, un warning solo imprime el aviso con una connotación de fallo y un info imprime cualquier otro tipo de aviso. Aunque la acción que realiza cada tipo de mensaje puede ser configurada.

El tipo de mensaje info incluye también un filtro de verbosidad para orientar la información que se muestra durante una prueba. Con ello se pueden separar, por ejemplo, avisos únicamente orientados a hacer depuración del sistema y los que dan información sobre la verificación. Además, tiene un sistema de etiquetas con la que se puede informar en el mensaje desde donde se está emitiendo que es uno de los datos que ofrece por defecto el informe final de UVM.

#### Estructura básica

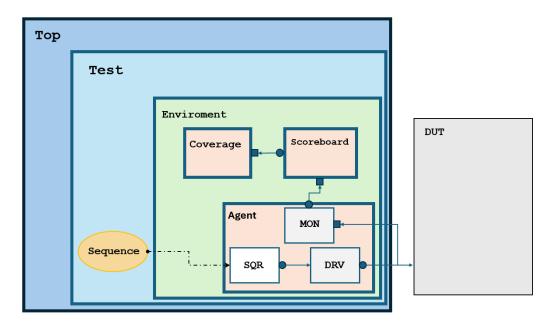

Figura 5 - Estructura básica de un sistema UVM

Desde el punto de vista del código, desde el *top* se instancian las conexiones al diseño, de aquí en adelante DUT (Desing Under Test) considerando su jerarquía dentro del sistema UVM, como también se hace una llamada al test que tiene que estar previamente definido en factory. Es común también definir señales que consumen tiempo real o que deben tener un comportamiento que no se tiene que ver afectado por la prueba en sí, como lo puede ser la señal de reloj del DUT. Ya que la documentación del estándar está toda en inglés, se darán los nombres originales junto a los nombres traducidos para facilitar la consulta de la documentación.

A nivel de test se instancia el entorno, la configuración del test y las secuencias que tendrá, siendo las dos últimas a lo que en este documento me refiero como el banco de pruebas. Según como se quiera plantear la verificación podría no ser siquiera necesario una configuración del test, valdría con crear diferentes secuencias que generen los diferentes comportamientos. Ambos acercamientos son perfectamente válidos, pero siempre es buena práctica parametrizar si se busca flexibilizar la verificación.

A nivel de entorno (Enviroment) se instancian los componentes y las conexiones entre ellos.

Un Agente (Agent), que es el componente que comúnmente termina conectado al DUT que a su vez instancia en su interior:

- un secuenciador (sequencer), que recibe los valores para cada señal de entrada que es generado en la secuencia,

- un controlador (driver), que transmite las señales del secuenciador al DUT

- un monitor, que recibe la respuesta del DUT.

En este ejemplo se considera solamente un agente, pero esto no tiene por qué ser necesariamente el caso, se podría añadir tantos agentes como secuencias se quieran controlar por separado, cabe también destacar que un agente no necesita estar conectado directamente al DUT pero sí es recomendable para simplificar la implementación del entorno.

Un Marcador (Scoreboard), que compara el funcionamiento del DUT con un modelo de referencia y registre los errores, ya sea con un simple conteo o un aviso de las condiciones con las que se produjo el error. Según el diseño a verificar, la complejidad al implementar un modelo de referencia puede variar, con un diseño simple podría bastar con un par de líneas describiendo su comportamiento llegando a ser el caso más simple un diseño combinacional como lo es un operador matemático. Modelos de referencia comunes pueden ser códigos no sintetizables, pero con la misma funcionalidad que el DUT en cuestión, pudiéndose utilizar la funcionalidad de DPI (Direct Programing interface) de SystemVerilog para comunicar el

sistema en SystemVerilog con código escrito en otro lenguaje, comúnmente C o C++ (pero no limitado a esos) y así tratar el modelo como una caja negra de cara a UVM.

Un componente de Cobertura (Coverage), que registra los estímulos que se ha transmitido al DUT como también los rangos de valores que ha generado el DUT durante la prueba. Cabe destacar que la inclusión de un componente de Cobertura implica el uso de grupos de cobertura para su manejo, siendo la otra alternativa la cobertura que ofrece SVA que puede llegar a ser más versátil ya que se instancia dentro de cada componente que se busca registrar. Este último acercamiento fue descartado de cara a este proyecto porque la herramienta Vivado v2024.2 no es compatible con la cobertura que ofrece SVA.

# 1.4 IMPLEMENTACIÓN DEL SISTEMA DE VERIFICACIÓN

En esta sección se explicará la implementado el sistema de verificación completo, pormenorizando paso a paso sus componentes junto a la justificación de su estructura final.

# 1.4.1 Esquema general

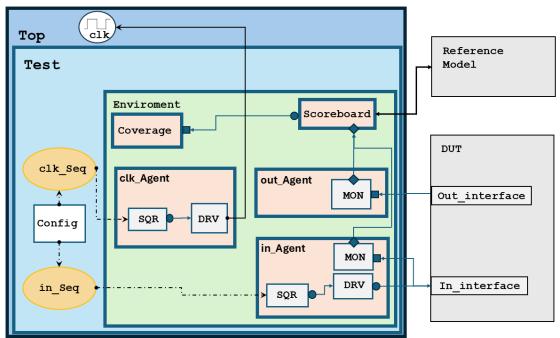

Figura 6 - Estructura del sistema de verificación implementado

En la Figura 6 está ilustrado el esquema general del sistema, se puede ver que a grandes rasgos cumple con la estructura de un entorno básico con una serie de componentes añadidos debido a la complejidad del diseño a verificar.

#### 1.4.2 DUT

Antes de entrar en detalle en cada módulo del sistema es necesario conocer el diseño a verificar. Cabe destacar que hasta el momento en este documento no ha sido relevante, ya que todo lo explicado anteriormente es común entre entornos UVM.

Considerando que el diseño a verificar será tratado como una caja negra, lo que necesitamos saber son solo dos cosas: su interfaz, eso son sus entradas y salidas, y su comportamiento esperado según sus entradas.

#### <u>Interfaz</u>

#### Entradas:

```

reset: 1 bit

sClk: 1 bit

sRun: 1 bit

vita_time: 64 bits sin signo – número de muestras

vita_time_trigger: 64 bits sin signo – número de muestras

len_PRI: 32 bits sin signo – número de muestras

duration_wave: 32 bits sin signo – número de muestras

type_wave: 3 bits

gain_percent: 8 bits sin signo – porcentaje

f_sample: 32 bits sin signo – hercios

bandwidth: 32 bits sin signo – hercios

f_signal: 32 bits sin signo – hercios

t_ramp: 32 bits sin signo – número de muestras

```

#### Salidas:

```

o_tdataI: 16 bits con signo – amplitud

o_tdataQ: 16 bits con signo – amplitud

o_tvalid: 1 bit

system_ready: 1 bit

```

De cara a la verificación se hace una subdivisión en los registros de entrada, entre los que rigen el **comportamiento temporal**: sClk, vita\_time y vita\_time\_trigger. Los registros de **control**: sRun y reset. Por último, los registros de **configuración** de la onda:

f\_sample, len\_PRI, duration\_wave, gain\_percent, type\_wave, f\_signal, bandwidth y t ramp.

#### Comportamiento:

El diseño es un generador de ondas que puede generar 3 tipos de onda diferentes, chirp lineal, tono y rampa según el valor en type wave.

La señal sClk es una señal de reloj generada a la misma frecuencia que indica el registro de frecuencia de muestreo  $f_sample$ , es importante que estas coincidan lo máximo posible para que se calcule correctamente la onda.

La señal vita\_time es un contador de tiempo en muestras que inicia al "encender" el sistema y no se reinicia. La señal vita\_time\_trigger es un registro que indica cuándo se tiene que empezar a generar muestras en referencia a vita\_time, tiene que ser mayor que vita time.

El registro sRun funciona como una señal run/stop, el sistema se para si está a 0 e inicializa una onda, es decir configuración y generación, cuando se conmuta a 1. Tiene que mantenerse accionada durante toda la generación de la onda. La salida de la generación de la onda se produce cuando vita time llega o supera a vita trigger time.

El registro reset pone el sistema en un estado inicial conocido previo a su funcionamiento. Se acciona cuando está a 1 y permite su funcionamiento cuando está a 0.

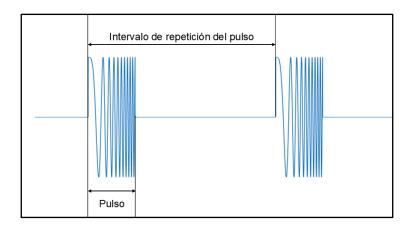

Los registros len\_PRI y duration\_wave se corresponden al intervalo de repetición del pulso (que consta de un tiempo en el que existe pulso y un tiempo en el que no hay señal) y la duración del pulso, ambos en número de muestras, por lo que su duración temporal depende de la frecuencia de muestreo.

Figura 7 - Intervalo de repetición de pulsos

El registro gain\_percent es una ganancia que cambia el valor de amplitud máximo que tendrá la onda, a 100% la amplitud máxima es de ±2^13. El registro se lee como numero entero por lo que el paso es de 1%.

Siguiente, están los registros de cada onda:

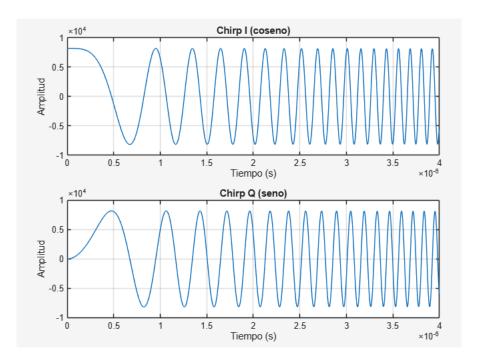

#### Chirp lineal:

Figura 8 - Chirp en modulación IQ

Es una onda sinusoidal que varía su frecuencia de manera lineal respecto al tiempo. La fase instantánea se rige por la ecuación:

$$\varphi(\mathsf{t}) = \varphi_0 + 2\pi \left(\frac{\mathsf{c}}{2}t^2 + f_0 t\right)$$

En la que  $\varphi_0$  es desfase inicial, c es el ancho de banda y  $f_0$  es la frecuencia inicial. Como no hay desfase y la frecuencia inicial siempre es 0Hz la expresión se simplifica a:  $\varphi(t) = \pi c \ t^2$

Siendo c el valor de bandwidth. La fase se calcula desde t=0 hasta  $t=duration\_wave*$  ( $\frac{1}{f\ sample}$ ). Es decir, el barrido de frecuencia del chirp dura lo que dure el pulso entero.

#### Tono:

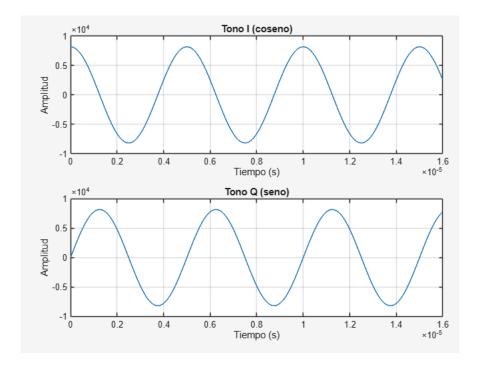

Figura 9 - Tono en modulación IQ

Es una onda sinusoidal simple cuya fase instantánea se calcula con la expresión:

$$\varphi(t) = 2\pi \cdot t \cdot f$$

Siendo f el valor de f\_signal.

Antes de continuar con el ultimo tipo de onda es adecuado aclarar que tanto para la generación del chirp como el tono se utiliza la modulación I/Q, es decir se generan 2 ondas simultáneamente, una con el seno y otra con el coseno de la misma fase instantánea. Esta es una técnica común en la generación de ondas de radiofrecuencia ya que ayuda a quitar

ambigüedades en la demodulación de la onda. Es por esto por lo que tanto la Figura 8 y Figura 9 están ilustradas 2 ondas con un desfase de 90°.

## Rampa:

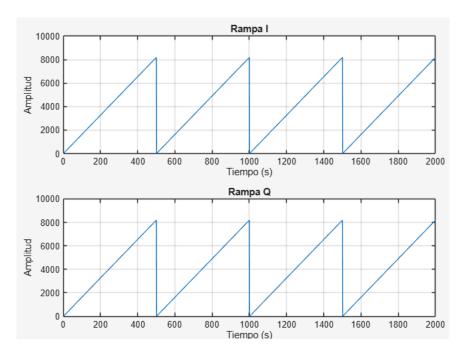

Figura 10 - Secuencia de rampas

A diferencia de las anteriores, no es sinusoidal, es una onda con un incremento lineal que se corresponde al incremento necesario para llegar a la amplitud máxima en un periodo indicado, ese periodo se corresponde al registro to to ramp en número de muestras.

Finalmente, están los registros output:

En los registros o\_tdataI y o\_tdataQ se escriben las amplitudes instantáneas de las ondas generadas. Estos registros solo tendrán valores válidos cuando el registro o\_tvalid sea igual a 1. El registro system\_ready es accionado por el DUT cuando la onda ha sido configurada y el sistema está listo para generar valores de onda.

# 1.5 IMPLEMENTACIÓN DEL ENTORNO

En el siguiente apartado, detallaré componente a componente como fue implementado el entorno de simulación. Puesto que el código completo está anexado al documento únicamente incluiré fragmentos que considere relevantes para la implementación del entorno UVM.

#### 1.5.1 Top

El documento wave\_gen\_tb\_top es la cabecera de toda la simulación, en él se instancian todas las interfaces de simulación que cabe destacar serán los registros visibles desde la simulación de vivado. Debido a esto, se consideró apropiado para la visualización instanciar el modelo de referencia como un módulo SystemVerilog al igual que el propio DUT.

En un entorno más simple es aquí donde se instanciaría el reloj que controlaría todo el sistema, pero en este caso es necesario una generación de señal de reloj dinámica y acceso a su frecuencia real dentro del entorno UVM, es por esto por lo que se hace necesario el agente reloj implementado más adelante. El top únicamente se encarga de conectar el reloj generado al resto de interfaces.

En el top se inician las fases de ejecución del sistema UVM dando inicio al test concreto ya definido en factory de UVM, que se explicará en la sección de implementación del banco de pruebas.

Por último, se asignan los interfaces virtuales a las interfaces correspondientes dentro del sistema UVM.

#### 1.5.2 Entorno

La clase wave\_gen\_env extiende de la clase uvm\_env, en ella se instancian todos los componentes del sistema UVM como objetos, que en este caso son agentes de puerto de entrada y salida, agente reloj, marcador y cobertura.

En la fase de construcción se crean todos los componentes y en la fase de conexión se conectan los puertos de análisis de los monitores de los agentes de entrada y salida con el marcador y el puerto de análisis del marcador con el de cobertura.

## 1.5.3 Agente puerto de entrada

El agente wave\_gen\_in\_agent se extiende de la clase uvm\_agent, en ella de declaran su secuenciador, controlador y monitor, que se crean en fase de construcción y se une el secuenciador con el controlador en fase de conexión.

#### <u>Interfaz</u>

Se declaran los registros que tiene la interfaz de entrada al DUT, junto a los clocking blocks para actualizar los datos a flanco de reloj positivo en el controlador y a flanco de reloj negativo en el monitor.

```

clocking dr cb@(posedge clk);

output reset;

output sClk;

output vita time;

output vita time trigger;

output f sample;

output bandwidth;

output t ramp;

output gain percent;

endclocking

modport DRV (clocking dr cb);

clocking rc cb@(negedge clk) ;

input reset;

input sClk;

input vita time;

input vita time trigger;

input f sample;

input bandwidth;

input t ramp;

input gain percent;

endclocking

modport RCV (clocking rc_cb);

```

Figura 11 - Estructura de la interfaz del puerto de entrada del DUT

Nótese que cada clocking block especifica si cada registro es entrada o salida para el sistema de verificación.

#### Secuenciador

La clase wave\_gen\_in\_sequencer se extiende de la clase uvm secuencer#(uvm secuence item) parametrizada por el ítem de secuencia del

agente, en este caso es wave\_gen\_in\_transaction, que será explicado en la sección de implementación del banco de pruebas. Únicamente se crea a sí misma, pero su función es de recibir lo que se genera en la secuencia correspondiente y transmitir el ítem secuencia al controlador.

#### Controlador

Se extiende de la clase uvm\_driver# (uvm\_secuence\_item) parametrizada por el mismo ítem secuencia, en ella se instancia la interfaz virtual correspondiente, que se conecta a la interfaz declarada en el top mediante la base de datos de UVM en la fase de construcción.

En la fase de ejecución, el controlador se encarga de volcar el ítem secuencia en la interfaz virtual cumpliendo con el protocolo de handshake entre la secuencia y el controlador.

```

virtual task run_phase(uvm_phase phase);

forever begin

seq_item_port.get_next_item(req);

drive();

@(vif.dr_cb);

$cast(rsp,req.clone());

rsp.set_id_info(req);

seq_item_port.item_done();

seq_item_port.put(rsp);

end

endtask : run_phase

```

Figura 12 - Fase de ejecución del controlador del agente de entrada

#### **Monitor**

La clase wave\_gen\_in\_monitor se extiende de la clase uvm\_monitor. En ella se instancia y conecta la interfaz virtual al puerto de la misma manera que en el controlador. También se crea el puerto de análisis que se usa para conectar el agente con el marcador.

En la fase de ejecución lee la interfaz que acaba de ser escrita en el controlador y vuelca la lectura en el puerto de análisis.

```

virtual task run_phase(uvm_phase phase);

forever begin

collect_trans();

mon2sb_port.write(act_trans);

end

endtask : run_phase

```

Figura 13 - Fase de ejecución del monitor del agente de entrada

## 1.5.4 Agente puerto de salida

El puerto de salida fue originalmente pensado para que manejase una secuencia en paralelo a la del agente del puerto de entrada, durante el proceso de implementación se descartó una señal de control, lo que hizo que dejase de ser necesario un controlador y un secuenciador, pero se mantuvo el agente en caso de haber sido necesario reintegrar la señal descartada.

Al igual que el agente de puerto de entrada, la clase wave\_gen\_out\_agent se extiende de uvm agent pero en este caso solo se encarga de instanciar únicamente el monitor.

## <u>Interfaz</u>

En la interfaz se declaran los registros de salida siendo únicamente necesario un clocking block para el monitor, con la misma estructura que el mostrado en el agente de entrada.

## **Monitor**

En el monitor está instanciado una interfaz virtual al puerto de salida a través de la base de datos de UVM. Está creado también el puerto de análisis que conecta al marcador.

En fase de ejecución lee los registros de la interfaz y los envía al marcador.

# 1.5.5 Agente reloj

En un principio no se estaba considerando la posibilidad de que el reloj fuese dinámico, por lo que los agentes de los puertos de entrada y salida recibían una señal de reloj generada en top. Para ampliar la funcionalidad del sistema de verificación se implementó un agente que generase un reloj de frecuencia variable, pero respetando todo lo que estaba implementado.

Antes de que el agente reloj fuese implementado, se generaba un reloj a una frecuencia concreta en el top y era este reloj el que accionaba cada ítem de secuencia, este es el reloj del test. Al accionarse a cada flanco de reloj positivo, resultaba en un reloj a la mitad de la frecuencia, la señal sclk, este es el reloj del DUT. Ya que todo estaba implementado con esta diferencia de frecuencia en mente, el agente tuvo que ser implementado para este comportamiento.

Su clase wave\_gen\_clk\_agent se extiende de la clase uvm\_agent y se encarga de crear el secuenciador, controlador y la conexión entre ambos.

#### Interfaz

La interfaz del agente reloj es una interfaz interna, es decir no está conectada directamente al DUT, en su lugar está pensada para que se lea desde la secuencia del agente del puerto de entrada. únicamente consta del bit de reloj y la frecuencia en hercios.

#### Secuenciador

La clase wave\_gen\_clk\_sequencer se extiende de la clase uvm\_sequencer# (uvm\_sequence\_item), Recibe el ítem generado en su secuencia y únicamente sirve de conexión entre la secuencia y el controlador.

# Controlador

La clase wave\_gen\_clk\_driver se extiende de la clase uvm\_driver# (uvm\_sequence\_item), en la fase de construcción conecta su interfaz virtual con la interfaz declarada en top, que es lo que permite el acceso del reloj a nivel de top.

En su fase de ejecución se ejecutan dos hilos de manera concurrente hasta el fin de la simulación con la sentencia fork...join none.

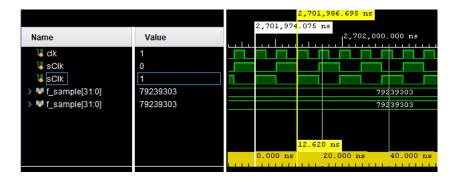

Uno de los hilos genera la señal de reloj del test directamente en la interfaz virtual a una frecuencia determinada y el otro hilo calcula el semiperiodo que tiene que respetar la señal de reloj. El semiperiodo se inicializa por defecto a 5ns y se mantiene así hasta que reciba un cambio válido desde su secuencia. Por último, calcula cual es la frecuencia correspondiente al semiperiodo calculado para que se transmita al agente del puerto de entrada. El cálculo se explicará más adelante junto a la secuencia del agente.

#### 1.5.6 Modelo de referencia

El modelo de referencia se implementó como un módulo de SystemVerilog conectado a nivel de top, esto da acceso no solo a la interfaz del modelo sino también a las variables internas, lo que facilitó la depuración de su código para que se ajuste correctamente al módulo real frente a los mismos estímulos.

El modelo de referencia no necesita limitarse a tener únicamente los puertos del módulo real, en este caso se incluyó en su interfaz una salida que facilitaría el posterior análisis y comparación que es el registro o\_phase de tipo real (equivalente a un tipo coma flotante de doble precisión en C) que da acceso a la fase instantánea en cada muestra al sistema UVM sin realizar un cálculo redundante de por medio.

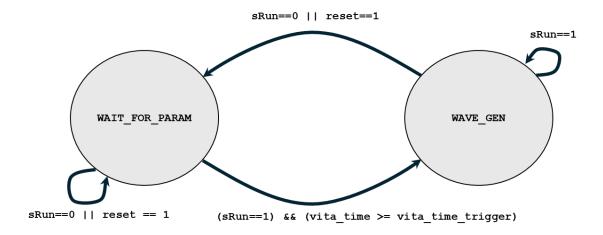

Para su funcionamiento se implementó una máquina de estados simple de dos estados, un estado en el que espera los parámetros de onda y un estado para generar la onda.

Figura 14 - Manejo de estados del modelo de referencia

El manejo de los estados se hace de acuerdo con lo explicado del comportamiento del modelo real. Es notable recalcar que el modelo de referencia no está limitado de la misma forma en la que lo está el módulo real, por lo que en este caso puede pasar de estar en espera sin leer la configuración en su puerto de entrada a generar onda de un ciclo al siguiente. Lo que esto permite es la detección de errores de desfase de ciclo cuando el módulo real no ha tenido suficiente tiempo para tener datos listos para transmitir en su puerto de salida.

En el estado WAIT\_FOR\_PARAM el modelo guarda los valores en los registros de entrada ya que tiene que ignorar todos los registros de **configuración** durante el estado WAVE\_GEN, y hace los ajustes para compartir la lógica de generación de onda entre los 3 tipos de onda.

```

if( sRun && (vita_time >= vita_time_trigger)) begin // vuelca parametros de entrada a

registros antes de empezar a generar onda cuando vita_time_trigger se alcance

system_ready <= 1;

typeWave<=type_wave;

lenPRI<=len_PRI;

durationWave<=duration_wave;

o_tvalid <= 0;

i_f_signal = f_signal;

i_f_sample = f_sample;

i_t_ramp = t_ramp;

i_gain_percent = gain_percent;

real_gain = (gain) * real'(i_gain_percent)/100;</pre>

```

```

i_bw = bandwidth;

signalT = 1/real'(i_f_signal);

sampleT = 1/real'(i_f_sample);

if(type_wave==2) begin // arreglo para rampa

signalT = i_t_ramp * sampleT;

i_f_signal = 1/real'(signalT);

real_gain = (gain-1) * real'(i_gain_percent)/100; // El val max que puede llegar

la rampa real es 8191 no 8192

end else if (type_wave==0) begin // arreglo para chirp

signalT = (duration_wave)*sampleT;// Un barrido dura un duration_wave entero

i_f_signal = 1/sampleT;// Tomo la periodicidad de la señal como el barrido entero

end

end

```

Figura 15 - Estado WAIT\_FOR\_PARAM del modelo de referencia

En el estado WAVE\_GEN se controla el pulso de generación de la onda, cumpliendo con lo especificado en el comportamiento del propio DUT.

```

WAVE_GEN: begin

o tvalid <= 1;

system_ready <= 1;</pre>

sampleCounter <= sampleCounter+1;</pre>

//---- Verifica que no haya llegado al fin del periodo

if(sampleCounter <= durationWave) begin</pre>

//////// Genera la onda

end

//////// Actualiza la salida

if(sampleCounter<durationWave) begin // si es menor al duration wave leido antes,</pre>

pasa dato

o tdataI <= I;

o tdataQ <= Q;

o tvalid <= 1;

o_phase <= $realtobits(r_data);</pre>

end else begin // si sobrepasa duration wave, vuelca 0 a la salida

o tdataI <= 0;

o tdataQ <= 0;

o tvalid <= 1;

o phase <= 0;

signalCounter <=0;</pre>

end

///////// Verifica que no haya pasado lenPRI

if (sampleCounter > lenPRI - 2 ) begin

sampleCounter<=0;</pre>

signalCounter<=0;

end

end

```

Figura 16 - Estado WAVE\_GEN del modelo de referencia

Por último, la generación de los 3 tipos de onda. Nuevamente, como no necesita ser sintetizable, todos los cálculos se realizan en variables de tipo real y se hace una conversión implícita al final de cada onda en la definición de  $\mathbb{Q}$  e  $\mathbb{I}$ , que es lo que se vuelca en los registros de salida directamente. El truncamiento que realiza implícitamente SystemVerilog es al entero más cercano, en caso de ser necesario o verse apropiado para una tendencia del modelo real se podría forzar la orientación del truncamiento, se decidió dejar el truncamiento al número entero más cercano para que el modelo difiriera lo mínimo respecto a un cálculo exacto.

```

if(sampleCounter <= durationWave) begin</pre>

//////// Genera la onda

if(typeWave==0) begin // chirp

r_data = pi * ( ((i_bw) * (sampleCounter*sampleT))/ (signalT) ) *

(sampleCounter*sampleT);

auxSinQ=$sin(r data);

auxCosI=$cos(r_data);

Q = auxSinQ * (real_gain);

I = auxCosI * (real_gain);

end else if(typeWave==1) begin // tono

r data=2*pi*sampleCounter * (sampleT*i f signal);

auxSinQ=$sin(r data);

auxCosI=$cos(r data);

Q = (\sin(r_data) * (gain) * real'(i_gain_percent)/100.0);

I = (\$\cos(r \text{ data}) * (gain) * real'(i gain percent)/100.0);

end else begin // rampa

r_data = signalCounter * (real_gain) / real'(i_t_ramp-1);

I = (r data); // real a logic

Q = (r data);

if(signalCounter < i t ramp - 1) begin</pre>

signalCounter <= signalCounter+1;</pre>

end else begin

signalCounter<=0;

end

end

```

Figura 17 - Cálculo de las ondas en el modelo de referencia

#### 1.5.7 Marcador

La clase wave\_gen\_scoreboard se extiende de la clase uvm\_scoreboard, la clase está orientada a recibir transacciones de los diferentes monitores dentro de los agentes conectados al DUT y compararlos con un modelo de referencia.

Se declaran las interfaces tanto del módulo real como el modelo de referencia, los puertos necesarios junto a una cola fifo para las transacciones que van entrando. Todo esto se crea

en la fase de construcción de UVM. En la fase de conexión se conectan los puertos con la fifo que se asegura que los datos de ambas interfaces correspondan al mismo instante.

Es notable destacar que la fase de ejecución del marcador está controlada por la disponibilidad de transacciones en la fifo, esto es así porque como componente de análisis, el marcador no tiene prioridad en la ejecución del sistema, solo se ejecuta cuando el sistema UVM no está activamente comunicándose con el DUT.

El manejo de errores en el marcador entra también en un amplio espectro de posibilidades, desde una comparación simple entre registros hasta aplicar métricas de error para registros concretos. Se consideró tratar con todos los errores de sincronización y errores en los valores de la señal en el marcador, cada manejo de error será explicado en el orden en la que se ejecutan en cada ciclo en la fase de ejecución, siendo la métrica principal del error el cálculo de la Raíz del Error Cuadrático Medio (Root-Mean-Square Error en inglés).

#### **RMSE**

La raíz del error cuadrático medio es una métrica usada para comparar el comportamiento de una variable frente un valor de referencia, su cálculo corresponde a la expresión

$$RMSE = \sqrt{\frac{\sum_{t=0}^{T} (\hat{x}_t - x_t)^2}{T}}$$

En el que t es la muestra actual, T el numero total de muestras,  $\hat{x}$  es el valor de referencia y x el valor muestreado.

Es una métrica de precisión en las mismas unidades de la muestra muy sensible a valores de error altos por lo que es adecuada para detectar rápidamente si ha sucedido o no un error a lo largo de la simulación. Idealmente si la referencia y los datos muestreados coinciden totalmente su valor es 0, pero es prácticamente imposible que este sea el caso.

Para su análisis hay que considerar que las unidades de su resultado son las mismas que las de la señal en cuestión, ya que lo que se está calculando es un error absoluto.

#### Fase de ejecución

```

build_actual_out();

if(!ignoreNext) begin

send to ref model();

@(vif.rc sb);

get from ref model();

if(actual.sClk) begin

compare_data();

if(!ignoreNext) begin

rmse sum();

sb2cov port.write(actual);

end

end

end else begin

ignoreNext=0;

end

end

endtask

```

Figura 18 - Fase de ejecución del marcador

La primera comparación es una comparación simple entre los registros. Para los registros de entrada no hay una razón por la que puedan ser diferentes, por lo que si lo son se puede asumir que hay un fallo con el sistema de verificación, por lo que salta directamente una advertencia con el tipo de mensaje `uvm\_warning.

La segunda comparación realizada es que la señal de o\_tvalid, que indica que el valor que está en la salida corresponde a la onda configurada, coincida entre el módulo real y el modelo. Como la única posibilidad de desfase es que el modelo se adelante, se acciona una bandera que indica que está adelantado (el bit ignoreNext) que detiene el modelo de referencia hasta que la señal de o\_tvalid del DUT se accione. Además, se hace un conteo del número de desfases en una simulación.

Con esta verificación se logran dos cosas, la primera es la detección de desfases, lo que permitió caracterizar el número de ciclos que necesita el módulo real para empezar a transmitir la onda que genera y la resincronización de la señal para no tener que descartar una onda completa para hacer la comparación.

```

if((actual.o_tvalid != expected.o_tvalid)) begin

`uvm_warning("SCOREBOARD", $sformatf("o_tvalid FAILED at vita=%d"

,actual.vita_time))

ignoreNext =1;

desyncFail=desyncFail+1;

end

```

Figura 19 - Detección de desincronización

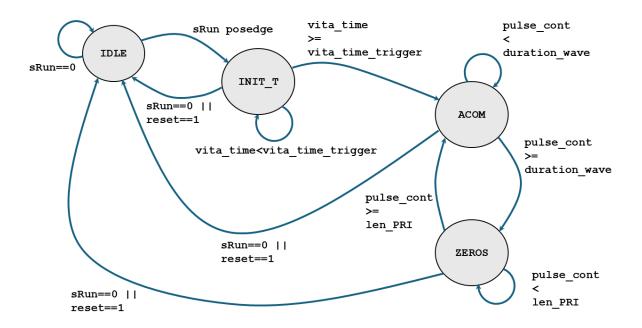

Las siguientes comparaciones se realizan en la llamada a la tarea rmse\_sum, que comenzó como un acumulador de errores en cada o\_tdata. Para ello se implementó una máquina de estados para únicamente contabilizar las muestras que correspondan a la parte activa del pulso de generación de onda.

Se consideraron 4 estados:

Figura 20 - Manejo de estados del acumulador de errores

IDLE, que corresponde a la espera de configuración de la onda.

INIT T, que corresponde con el periodo entre la configuración y la generación de datos.

ACOM, que corresponde con el periodo activo del pulso de generación.

ZEROS, que corresponde con la generación de ceros en el resto de pulso de generación.

Para controlar los estados fue necesario un contador auxiliar pulse\_cont para saber si se están generando valores de onda o ceros. Es necesario establecer esta distinción para únicamente tomar en cuenta los valores de onda generados para la acumulación del error, de lo contrario, las muestras en las que la salida son ceros, que siguen contando como muestras válidas, disminuirían artificialmente el error.

```

case (state)

IDLE: begin ; end

INIT T: begin pulse cont<=0; end</pre>

ACOM: begin pulse cont<=pulse cont+1;

if(actual.o tvalid) begin

err_I = actual.o_tdataI - expected.o_tdataI;

err_Q = actual.o_tdataQ - expected.o_tdataQ;

if( err I>41 || err Q>41 || err I<-41 || err Q<-41) begin</pre>

// si el error es más del 0.5%

`uvm info("SCOREBOARD", $sformatf("Readings \n actual.I=%d actual.Q=%d \n

expected.I=%d expected.Q=%d \n errI = %d errQ=%d \n at vita: %d",

actual.o_tdataI,actual.o_tdataQ,expected.o_tdataI,expected.o_tdataQ

,err I,err Q,actual.vita time), UVM HIGH)

end

// `uvm_info("SCOREBOARD", f(n) = 0 com_err_I:%d com_err_Q:%d -- at

vita: %d ",com error I,com error Q,actual.vita time ), UVM HIGH)

com error I= com error I + ((err I)**2);

com error Q= com error Q + ((err Q)**2);

valid samp=valid samp+1;

track peak error();

histogram error(err I, err Q);

//$fdisplay(csv chirps,"%d, %d, %d, %d,%0.12f",

actual.o tdataI,actual.o tdataQ,expected.o tdataI,expected.o tdataQ,

$bitstoreal(expected.o_phase));

//`uvm info("SCOREBOARD", sformatf("\n com err I:%d com err Q:%d -- at vita:%d ", info("scoreboard"))

com error I,com error Q,actual.vita time ), UVM HIGH)

end

end

ZEROS: begin

if(pulse cont>=actual.len PRI) begin

pulse cont=0;

end else begin

pulse cont=pulse cont+1;

end

end

endcase

```

Figura 21 - Estructura del acumulador de errores

Por orden de aparición en el código, lo que sucede en el estado ACOM es:

Un mensaje por terminal para depuración que avisa que se ha excedido un error del 0.5% respecto al valor máximo de 8191 (2^13 - 1) junto al tiempo en vita\_time para encontrarlo fácilmente.

El sumatorio de los errores cuadrados para el posterior cálculo del RMSE con el conteo de muestras consideradas en el cálculo.

Un rastreo de los picos de error positivos y negativos por cada registro o\_tdata, que también guarda el tiempo en el que sucedió y la fase a la que corresponden dichos valores. Se

esperaba que los errores máximos correspondieran al chirp o al tono por la dificultad añadida que es el cálculo de funciones trigonométricas en hardware.

Un conteo de rangos de error para realizar un histograma de los errores una vez hubiese acabado la simulación. Con este se podrían encontrar tendencias en los errores de manera visual.

### Fase de extracción

En el marcador se usa también la fase de extracción que se ejecuta una vez han acabado las secuencias de entrada del sistema.

En la fase de extracción se realizan los cálculos necesarios para mostrar las métricas consideradas en la prueba para mostrarlas por terminal junto al informe general de UVM. De manera opcional también crea un archivo csv con todas las métricas orientado a facilitar su almacenamiento y análisis.

```

UVM_INFO C:/Xilinx/Vivado/2024.2/data/system_verilog/uvm_1.2/xlnx_uvm_package.sv(19968) @ 27040000000: reporter [TEST_DONE] 'run' phase is ready to proceed to the 'extract' phase UVM_INFO ../.../../uvm_srcs/wave_gem_scoreboard.svh(437) @ 27040000000: uvm_test_top.env.sb [SCOREBOARD] times desync: 0

UVM_INFO ../.../../uvm_srcs/wave_gem_scoreboard.svh(460) @ 27040000000: uvm_test_top.env.sb [SCOREBOARD]

RMSE I: 13.119, RMSE Q: 15.428, valid samples: 104146

UVM_INFO ../.../../uvm_srcs/wave_gem_scoreboard.svh(463) @ 2704000000: uvm_test_top.env.sb [SCOREBOARD]

ETROR [iii] 1: 1 phase: 3.261211 rad time: 3434 ]

ETROR [max Q: 58 phase: 3.157454 rad time: 3262] | [min Q: -58 phase: 3.109432 rad time: 3261]

```

Figura 22 - Informe final de la verificación por terminal

```

[SCOREBOARD] Bin 35 [ -10: -9] I:4505 Q:2175

[SCOREBOARD] Bin 36 [ -8: -7] I:4626 Q:3928

[SCOREBOARD] Bin 37 [ -6: -5] I:4922 Q:4888

[SCOREBOARD] Bin 38 [ -4: -3] I:5990 Q:5720

[SCOREBOARD] Bin 39 [ -2: -1] I:23592 Q:15525

] I:15959 Q:20242

[SCOREBOARD] Bin 40 [

== 0

[SCOREBOARD] Bin 41 [

1:

21 I:2911 Q:8983

[SCOREBOARD] Bin 42 [ 3:

4] I:0 Q:6290

[SCOREBOARD] Bin 43 [

5:

6] I:0 Q:5786

[SCOREBOARD] Bin 44 [

7:

8] I:0 Q:2870

[SCOREBOARD] Bin 45 [

9: 10] I:0 Q:1704

```

Figura 23 - Conteo de errores para histograma

#### Código opcional para análisis pormenorizado

De manera opcional, estando comentado en el código anexado, están incluidas las funciones para guardar en un csv los datos necesarios para el cálculo de cada muestra de una onda, además de las propias muestras generadas por el DUT y el modelo de referencia. Sirve para

facilitar un análisis pormenorizado de una onda en específico en otro entorno como lo puede ser una hoja de cálculo Excel o Matlab.

Está comentado por su consumo innecesario de recursos de computación durante una simulación por lo que es una funcionalidad reservada a pruebas cortas más dirigidas, pero resultó ser útil una vez encontrada una fuente de error para analizar a fondo.

#### 1.5.8 Cobertura

La clase wave\_gen\_coverage se extiende de la clase uvm\_subscriber# (uvm\_sequence\_item), está orientada a recibir transacciones de un único puerto con la estructura con la que se parametriza y a ejecutarse cada que reciba una transacción. Para agrupar tanto entradas como salidas en una sola transacción utilizo la estructura creada para el modelo de referencia, ya que tiene todos los registros en una sola interfaz.

Antes de comenzar con la explicación del contenido del componente, es conveniente recalcar que, si bien vivado soporta gran parte de las funcionalidades que ofrece SystemVerilog, una de las que no, es la cobertura mediante SVA, lo que deja como único método compatible para la cobertura funcional a los grupos de cobertura.

#### Grupos y puntos de cobertura

Es un constructo de SystemVerilog que permite la cobertura funcional. Lo fundamental de esta forma de controlar la cobertura es que es muestreada, es decir, no considera todos los eventos de los registros consideradas si no solo el estado de los registros en un momento determinado y su cambio respecto a la muestra o muestras anteriores.

La pieza central de esta metodología son los puntos de cobertura: cada punto de cobertura está asociado a un registro en concreto. Cuando dicho registro es muestreado el punto de cobertura acumula en un contador la coincidencia dentro de unos rangos definidos por el usuario. Cada uno de estos rangos se corresponde a un contador llamado bin y pueden ser definidos de manera implícita o explicita. Si no se especifica nada se crea un bin por cada posible valor de una variable. Por ejemplo, a una variable de 8 bits se le asociaría de manera implícita 256 contadores, uno por cada valor que puede tener, por lo que es conveniente especificar de manera explícita los rangos que se esperan.

Como se mencionó, un bin no se limita al valor actual, si no que también permite capturar el cambio de un valor o grupo de valores a otro valor o grupo de valores específicos, como

también permite condicionar el conteo a otro registro por separado. Lo primero es útil para, por ejemplo, contar solo cuando la señal de control conmuta, el lugar de contar cada ciclo de reloj en el que está activado y lo segundo resulta útil cuando un valor solo se tiene en cuenta en una condición especifica.

Un acercamiento al conteo condicionado que no llegó a incluirse en la implementación son los cruces de bins, en el que se crean bins adicionales correspondientes a las combinaciones de cumplimiento de los bins indicados, que, si bien acortaría el proceso de definición de los bins considerados, se optó por una declaración de los condicionales explicita para facilitar la legibilidad en código.

Los puntos de cobertura se encapsulan en grupos de cobertura para asignar opciones de cara al informe de cobertura compartida entre puntos de cobertura y para unir los que tienen que ser muestreados a la vez.

En la implementación se optó por crear 2 grupos de cobertura, uno que sería muestreado cada ciclo de reloj del DUT y otro que solo sería muestreado al momento de configurar la onda a generar.

Para gestionar el instante de muestreo utilizo el contador de tiempo del DUT y varias banderas, que es una manera alternativa para saber en qué estado se encuentra el DUT que la utilizada en el marcador. Se optó por esta forma porque facilita el acceso a los diferentes retardos entre señales que se generan en la secuencia del puerto de entrada.

El siguiente fragmento se corresponde a la última llamada de función en el marcador (sb2cov\_port.write(actual);) definida en la clase de cobertura, lo que marca el fin de un ciclo en fase de ejecución dentro del entorno de UVM.

```

function void write(T t);

this.cov trans = t;

if(prev sRun && !cov trans.sRun) begin

v dropsRun=cov trans.vita time;

end

if(!prev_sRun && cov_trans.sRun) begin

vita delay = cov trans.vita_time_trigger - cov_trans.vita_time;

v sRun delay = cov trans.vita time - v prev sRun;

v prev sRun = cov trans.vita time;

v config=v prev sRun;

completeCycles=0;

v_dropsRun = cov_trans.vita_time - v_dropsRun;

sync sRun cg.sample();

end

// Control de interrupciones a traves de flags

if(( cov trans.vita time - v config ) <= cov trans.duration wave) begin</pre>

midPulse=1;

```

```

midZeros=0;

sync_sClk_cg.sample();

end else if((cov_trans.vita_time-v_config) > cov_trans.duration_wave) begin

midPulse=0;

midZeros=1;

if((cov_trans.vita_time-v_config)>=cov_trans.len_PRI) begin

completeCycles=completeCycles+1;

sync_sClk_cg.sample();

v_config=cov_trans.vita_time;

end else begin

sync_sClk_cg.sample();

end

end

prev_sRun=cov_trans.sRun;

endfunction

```

Figura 24 - Manejo del muestreo para cobertura

Como los puntos de cobertura dependen de un comportamiento esperado, veo conveniente especificar cuales fueron considerados una vez esté explicada el comportamiento que se busca provocar en la secuencia.

# 1.6 IMPLEMENTACIÓN DEL BANCO DE PRUEBAS

Una vez establecido un entorno funcional, es necesario definir la serie de estímulos con las que se busca verificar el comportamiento del DUT. Un posible comportamiento podría ser aleatorizar todas las variables en todo su posible rango de valores, pero esto sería poco productivo por una razón de peso; el módulo ha sido diseñado con una serie de parámetros de funcionamiento en mente, por lo que estos parámetros se deben tener en cuenta al limitar la aleatorización.

El proceso de implementación de una prueba versátil fue un proceso iterativo, del cual el documento se centrará solo en la estructura final de la prueba, ya que todas las versiones previas de la prueba fueron encapsuladas en un solo test.

A modo de contexto, las primeras pruebas tomaban algún comportamiento, como lo puede ser el periodo activo y frecuencia de los pulsos de generación de onda para dejarlos fijos frente al resto de las variables aleatorizadas, es decir, se guiaba el comportamiento con una variación reducida. Cada grupo de variables fijas que definían un comportamiento suponía crear una secuencia concreta que aplicar en un test. Con la implementación final se encapsuló los diferentes comportamientos planteados en una sola secuencia llamada desde un único test valiéndose de la base de datos de UVM para configurar cada prueba.

#### 1.6.1 Planteamiento del test

El test fue planteado como una prueba que facilite ser guiada a diferentes comportamientos, debido a que uno completo largo consume mucho tiempo y recursos computacionales, si lo que se quiere comprobar en el momento está más o menos localizado, se puede orientar un test corto en el que esté prácticamente asegurado que dentro de los posibles estímulos generados se encuentren ejemplos de lo que se busca comprobar, para ello se plantearon 4 modos de test y diferentes seleccionadores de aleatorización.

Primero, hay un seleccionador independiente al modo de test por cada variable que se consideró aleatorizable, con la que se escoge si se usan o no valores aleatorios para esa variable en el test. Si no se usan valores aleatorios se tiene que definir el valor fijo de dicha variable.

El resto de los seleccionadores están para escoger en qué rango se aleatoriza una variable. Tomando por ejemplo el registro  $f_{samp}$ , la frecuencia de muestreo, están considerados 4 rangos de aleatorización según el valor del selector.

```

0: [100MHz:80MHz] 1: [80MHz:50MHz] 2: [25MHz:80MHz] 3: [1MHz:25MHz]

```

Con esto se puede orientar el análisis sabiendo que el resto de las variables está en el mismo orden de frecuencia o uno diferente y como afecta a los valores generados.

Dicho esto, los modos de test son:

### Cada selector por separado

Se considera cada uno de los selectores por separado y se mantiene el comportamiento de los selectores escogidos durante todo el test.

#### **Selectores compartidos**

Se toma en cuenta un único rango para que todas las variables estén más o menos en el mismo orden de magnitud de frecuencia durante todo el test.

#### Barrido de comportamientos

Durante la duración del test cambia los selectores de manera conjunta para simular comportamientos desde la máxima frecuencia a la mínima, a modo de una revisión general.

Hasta 1/16 de la duración del test va a máximas frecuencias, disminuye al siguiente rango hasta 1/4, luego disminuye al siguiente rango a 1/2 y la última mitad del test lo hace en los rangos de frecuencia mínima.

# **Totalmente Aleatorio**

Aleatoriza los selectores con lo que los valores aleatorios quedan dentro de los parámetros de diseño y se generan interacciones dentro de dichos parámetros que no podrían haber sido generados empleando los modos anteriores.

# 1.6.2 Configuración de test.

La clase wave\_gen\_config usada para la configuración del test se extiende de la clase uvm\_object, para que forme parte del sistema UVM y pueda ser llamado desde su base de datos. La clase está compuesta de estructuras con los registros necesarios para cada uno de los selectores antes mencionados.

Exceptuando el selector de modo y el selector compartido usado en su respectivo modo, las variables consideradas para aleatorizar son: f\_sample, len\_PRI, duration\_wave, type\_wave, bandwidth, f\_signal, t\_ramp y gain\_percent. Cabe destacar que dichos registros son directamente parte del puerto de entrada del DUT y, además, se introducen 4 variables aleatorizables más que se encargan de retrasos entre señales de control en número de muestras. Estas son: vita\_delay, el número de muestras que tarda en alcanzarse el vita\_time\_trigger desde el accionamiento de sRun, sRun\_delay, el número de muestras entre desactivaciones sRun que marca el momento de reconfiguración de las ondas generadas, sRun\_drop, el número de muestras que la señal sRun permanece desactivada y reset\_delay, el número de muestras que tarda en accionarse una señal de reset desde la anterior.

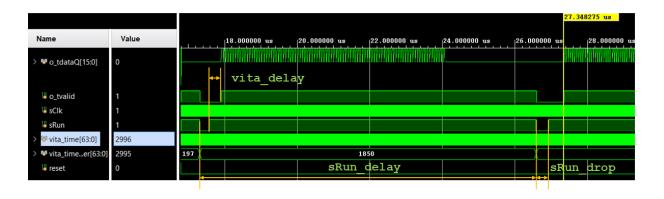

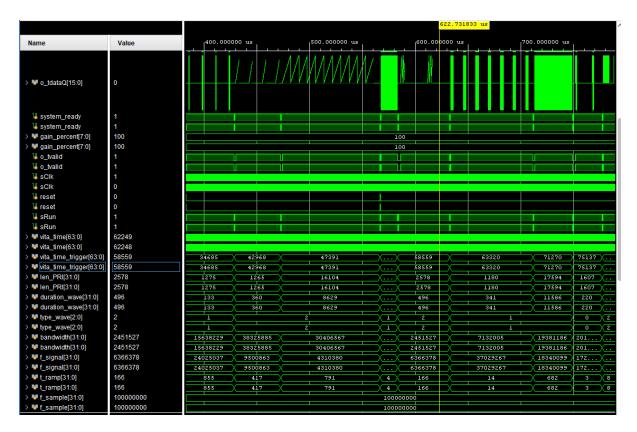

Figura 25 - Diferentes retrasos de señal aleatorizados

# 1.6.3 Secuencia de agente de puerto de entrada

La secuencia se planteó parametrizada para facilitar su reutilización. Su estructura está definida en tres partes:

- 1. El ítem secuencia que es la unidad considerada para la transacción entre componentes de UVM.

- 2. Una secuencia genérica base que configura lo necesario para su correcta definición en UVM.

- 3. La secuencia configurada.

### <u>ítem secuencia</u>

El ítem de secuencia es la clase wave\_gen\_in\_transaction que se extiende de la clase uvm\_sequence\_item, para hacerla de uso genérico únicamente contiene los registros del puerto de entrada del DUT. En la definición de los elementos de la transacción puede estar definido también si serán aleatorios. Definirlos de tipo aleatorios (rand) hace que se aleatorice desde SystemVerilog, que es la manera apropiada de tratar con aleatorizaciones usando UVM. Cabe destacar también que lo que se aleatorice de otra forma se tiene que declarar únicamente con su respectivo tipo, como es el caso, por ejemplo, de la frecuencia de muestreo que se aleatoriza desde la secuencia del agente reloj o la señal sRun donde lo que se aleatoriza son retrasos en su comportamiento, no la señal en sí.