# Extracción y Dependencia con la Polarización del Modelo de Pequeña Señal de Dispositivos HEMT de Enriquecimiento

Juan Luís Cano<sup>(1)</sup>, Beatriz Aja, Eduardo Artal, Tomás Fernández

<sup>(1)</sup> juanluis.cano@unican.es

Dpto. de Ingeniería de Comunicaciones. Universidad de Cantabria.

Avd. de los Castros s/n, 39005, Santander, Spain

Abstract- This paper describes a step by step method for the small signal circuit model extraction of an Enhancement-mode pseudomorphic High Electron Mobility Transistor (E-pHEMT). This method is based on the "cold-FET" technique, modified to be used with enhancement-mode transistors. The technique applied, fully based on S-parameters measurements, permits to obtain the fifteen elements model, which fits the measured S-parameters in an accurate way through the bandwidth of operation of the transistor. Different plots of the intrinsic parameters are presented showing their bias dependence, which is found to be very similar to depletion mode devices.

## I. INTRODUCCIÓN

La técnica de FET-frío (cold-FET), descrita en primer lugar en [1], utiliza dos medidas de parámetros de Scattering (parámetros-S) tomadas con una tensión en drenador nula,  $V_{ds} = 0$ , para obtener los parámetros extrínsecos del modelo de pequeña señal: una de ellas con una alta polarización en puerta de la cual se extraen las inductancias y resistencias parásitas del modelo, y la otra con el transistor cortado, V<sub>gs</sub> < V<sub>T</sub>, de la cual se extraen las capacidades parásitas de este modelo. Posteriormente, los elementos intrínsecos del modelo se obtienen a partir de expresiones analíticas sobre los parámetros-S del dispositivo medidos en el punto de polarización deseado. En [2] se superan algunos problemas que surgen durante la aplicación de la técnica de FET-frío, como es la degradación causada en la puerta por la utilización de fuertes corrientes en esta zona del dispositivo, incluyendo la condición de FET sin polarizar (unbiased-FET),  $V_{gs} = 0 \ V \ y \ V_{ds} = 0 \ V$ , que sustituye a la medida con una fuerte polarización en puerta.

Ambas técnicas señaladas anteriormente fueron aplicadas a transistores de deplexión ( $V_T < 0~V$ ), en los cuales las condiciones de FET sin polarizar y FET cortado resultan en dos modelos de circuito diferentes, de los cuales se pueden extraer los elementos extrínsecos del modelo de pequeña señal. En el caso de transistores de enriquecimiento ( $V_T > 0~V$ ) ambas condiciones son equivalentes ya que  $V_{gs} = 0~V < V_T$  y por tanto, el circuito equivalente bajo estas condiciones es el mismo. La solución que se propone en este documento es polarizar el transistor con una tensión de puerta ligeramente superior a la tensión de corte, manteniendo una tensión nula en drenador, obteniéndose un circuito equivalente igual al del FET sin polarizar que aparece en [2].

Esta solución se aplica al transistor ATF-55143 de Agilent Technologies, el cual es un dispositivo E-pHEMT para aplicaciones de bajo ruido desde 450 MHz hasta 6 GHz,

con una tensión de corte  $V_T=0.3\ V$  y una anchura total de puerta de  $400\ \mu m$  [3].

## II. CONDICIÓN DE FET-FRÍO PARA E-PHEMT

En los transistores de enriquecimiento la tensión de corte es positiva y por tanto, si se hace nula la tensión de puerta, el transistor se encuentra en corte, lo que hace que las dos condiciones aplicables en los transistores de deplexión se conviertan en una única. Por otro lado, cuando se polariza en directa la puerta y se quiere que la corriente de ésta sea despreciable se necesita que el valor de esta tensión sea pequeño. En este documento se fija un valor de  $V_{\rm gs}=0.5~{\rm V}$ , el cual lleva al transistor a un estado de semi-no polarización. Esta condición, junto con la de transistor en corte, permite utilizar los modelos de circuito clásicos [2] para obtener los elementos extrínsecos del modelo de pequeña señal del dispositivo.

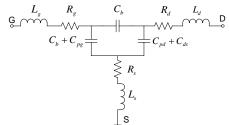

Fig. 1. Circuito equivalente para el E-pHEMT cortado.

# III. MEDIDA DE LOS PARÁMETROS-S DEL DISPOSITIVO

A partir de las medidas de los parámetros-S tomadas bajo las anteriores condiciones se pueden extraer fácilmente los elementos extrínsecos del modelo del dispositivo ( $R_g$ ,  $R_s$ ,  $R_d$ ,  $L_g$ ,  $L_s$ ,  $L_d$ ,  $C_{pg}$  y  $C_{pd}$ ), a través de las apropiadas transformaciones matriciales (parámetros S, Z e Y) junto con la eliminación de las contribuciones de los elementos ya calculados mediante un proceso de de-embedding. Una vez que se han calculado los elementos extrínsecos, los intrínsecos ( $C_{gs}$ ,  $R_i$ ,  $C_{gd}$ ,  $g_{ds}$ ,  $C_{ds}$ ,  $g_m$  y  $\tau$ ) se calculan en el punto de polarización deseado a partir de las medidas de parámetros-S del dispositivo en ese punto.

Para tomar estas medidas se utiliza un analizador de redes modelo 8510C de Hewlett-Packard junto con un útil de medida (test-fixture) especialmente construido para una adecuada calibración LRL (Line-Reflect-Line) en los terminales del transistor.

El test-fixture se diseñó sobre un sustrato de tipo GML1000 ( $\epsilon_r$ = 3.2 y h= 30 mils) con una línea de pequeña longitud para establecer el plano de referencia de la calibración y una línea con una longitud  $\lambda$ /4 mayor que la anterior para cubrir así un ancho de banda en la medida de 8:1 (ancho de banda/frecuencia inicial) [4]. Como elemento con un alto valor de reflexión se eligió un corto circuito, de forma que mostrase el mismo coeficiente de reflexión en ambos puertos del equipo de medida.

Dado que la banda de utilización de este transistor es muy grande se eligió la parte baja de la misma como la más indicada para obtener el modelo de éste, ya que los efectos parásitos de elementos ajenos al dispositivo, como por ejemplo el útil de medida, son menos importantes. De acuerdo con esto, las medidas se realizaron en la banda de 0.4 a 3.2 GHz.

# IV. EXTRACCIÓN Y AJUSTE DE LOS PARÁMETROS

Las resistencias e inductancias se obtienen a partir de los parámetros-S medidos bajo la condición de semi-no polarización, después de transformar estos en parámetros de impedancia (parámetros-Z).

$$Z_{11} = R_{s} + R_{g} + \frac{R_{c}}{3} + j \left( \omega \left( L_{s} + L_{g} \right) - \frac{1}{\omega C_{g}} \right)$$

(1)

$$Z_{12} = Z_{21} = R_s + \frac{R_c}{2} + j\omega L_s \tag{2}$$

$$Z_{22} = R_s + R_d + R_c + j\omega(L_s + L_d)$$

(3)

En las expresiones (1)-(3),  $R_c$  representa la resistencia del canal, mientras que  $C_g$  es el efecto capacitivo debajo de la puerta. Los valores de las inductancias se extraen directamente de las ecuaciones (1)-(3) ya que éstas forman un sistema de tres ecuaciones con tres incógnitas. Para determinar estos valores, las partes imaginarias de los parámetros-Z se representan y se ajustan mediante alguna herramienta de ajuste de curvas, como las existentes en Matlab©. En el caso de las resistencias, se tienen cuatro incógnitas por lo que se necesita una ecuación adicional. Esta ecuación (4) se puede extraer a partir de la medida del transistor en la condición de corte.

$$Re(Z_{11}) = R_s + R_a \tag{4}$$

Las representaciones de la ecuación (4) y de las partes reales de (1)-(3) son independientes de la frecuencia por lo que es fácil extraer los valores de las resistencias. Finalmente, las capacidades parásitas de los terminales,  $C_{pg}$  y  $C_{pd}$ , se calculan a partir de las medidas del transistor en la condición de corte. A partir de los parámetros-S calculados bajo esta condición, las contribuciones de las inductancias y resistencias parásitas calculadas anteriormente se pueden eliminar mediante un proceso de de-embedding, como se puede ver en la Fig. 1. Los parámetros-Z resultantes se transforman en parámetros de admitancia (parámetros-Y) de donde se pueden derivar las siguientes expresiones.

$$\operatorname{Im}(Y_{11}) = j\omega(C_{pg} + 2 \cdot C_{b})$$

(5)

$$Im(Y_{12}) = Im(Y_{21}) = -j\omega C_b$$

(6)

$$\operatorname{Im}(Y_{22}) = j\omega \left(C_b + C_{pd} + C_{ds}\right) \tag{7}$$

Las capacidades intrínsecas  $C_b$  y  $C_{ds}$  no introducen ningún error adicional en el cálculo. Para resolver las ecuaciones (5)-(7) se supone la relación  $C_{pd}$ =0.25 $C_{ds}$  [2]. Una vez más, la mejor forma de obtener los valores buscados es mediante un proceso de ajuste con alguna herramienta matemática.

Una vez que se llega a este punto se han obtenido los ocho parámetros extrínsecos del modelo de pequeña señal del transistor. Para determinar los siete elementos intrínsecos es necesario realizar una medida de los parámetros-S del dispositivo en el punto de polarización deseado. Después de eliminar los efectos parásitos de los elementos extrínsecos calculados previamente, se calculan los parámetros-Y del dispositivo intrínseco y finalmente se aplican las ecuaciones que aparecen en otros trabajos [5] para obtener los valores de estos elementos intrínsecos.

La parte final de este proceso de obtención del modelo en pequeña señal de un transistor es la optimización de los valores previamente calculados para ajustarlos a las medidas realizadas en un determinado punto de polarización.

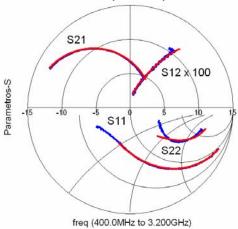

Fig. 2. Comparación entre los parámetros-S medidos (azul) y modelados (rojo) para una polarización de  $V_{ds}=2.7\ V\ e\ I_{ds}=20\ mA.$

Los datos que se muestran en la Fig. 2. se han obtenido para un punto de polarización de  $V_{ds}=2\ V$  e  $I_{ds}=20\ mA$ , el cual es un punto en la zona media del rango de polarizaciones para este dispositivo.

| Lg(nH)  | $Rg(\Omega)$ | Cpg(pF) | Ld(nH) | $Rd(\Omega)$ | Cpd(pF) | Rs(Ω)   | Ls(nH) |

|---------|--------------|---------|--------|--------------|---------|---------|--------|

| 0.99    | 0.44         | 0.18    | 1.06   | 1.45         | 0.05    | 0.5     | 0.45   |

| Cgs(pF) | Ri(Ω)        | Cgd(pF) | gm(mS) | τ(pseg)      | gds(mS) | Cds(pF) |        |

| 0.76    | 18.5         | 0.095   | 171.1  | 8.41         | 2.53    | 0.15    |        |

Tabla 1. Valores optimizados del modelo de pequeña señal para una polarización de  $V_{ds}=2.7\ V$  e  $I_{ds}=20\ mA$ .

# V. DEPENDENCIA DEL MODELO CON LA POLARIZACIÓN

Los elementos extrínsecos del modelo son independientes del punto de polarización por lo tanto no se necesita hacer una análisis sobre estos elementos. Por otro lado, los parámetros intrínsecos sí son dependientes de la alimentación y, en muchos casos, muestran una dependencia no lineal.

Para obtener el modelo del transistor en los diferentes puntos de polarización se han fijado los elementos extrínsecos a los valores que se muestran en la Tabla 1, mientras que los elementos intrínsecos se han optimizado a partir de las medidas de parámetros-S en los diferentes puntos.

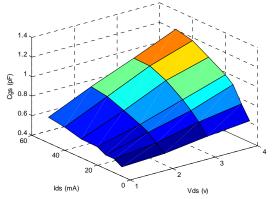

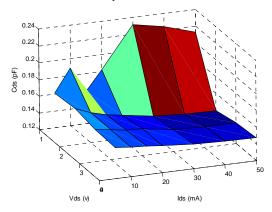

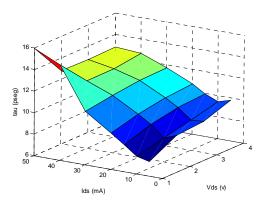

Fig. 3. Variación de C<sub>gs</sub> (pF) en función de la polarización.

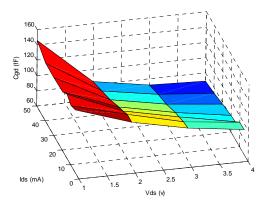

Fig. 4. Variación de C<sub>gd</sub> (fF) en función de la polarización.

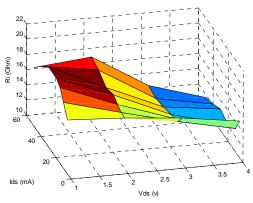

Fig. 5. Variación de  $R_i(\Omega)$  en función de la polarización.

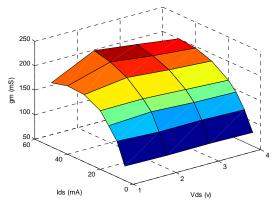

Fig. 6. Variación de la transconductancia (mS) en función de la polarización.

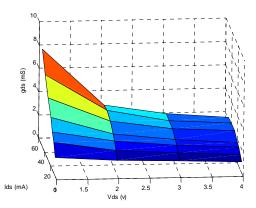

Fig. 7. Variación de la conductancia de salida (mS) en función de la polarización

Fig. 8. Variación de C<sub>ds</sub> (pF) en función de la polarización.

Fig. 9. Variación de  $\tau$  (pseg) en función de la polarización.

En las Figs. 3-9, se muestra el comportamiento de los elementos intrínsecos del modelo. Los parámetros  $g_{ds}$  y  $C_{ds}$  son poco variables con la polarización en las zonas usuales de utilización de estos dipositivos, por lo que se puede decir que la impedancia de salida de este transistor no se ve muy afectada por el punto de polarización elegido.

De acuerdo con las diferentes gráficas mostradas, se puede señalar que el comportamiento del modelo de pequeña señal de los transistores de enriquecimiento en función de la polarización está en concordancia con la teoría y expresiones, de forma cualitativa, utilizadas en los transistores de deplexión [6].

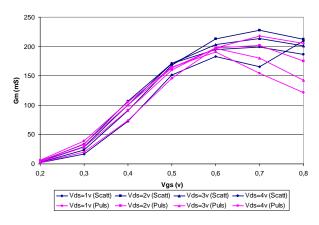

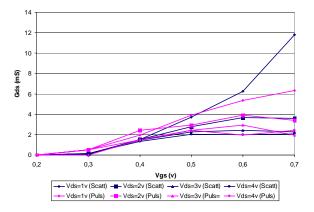

Finalmente, para validar los resultados obtenidos, se han realizado medidas pulsadas [7] de la transconductancia y conductancia de salida del transistor, permitiendo esto comparar los resultados de estas medidas con los valores extraídos.

Fig. 10. Comparación entre la transconductancia calculada a partir de las medidas de Scattering (azul) y los valores obtenidos de las medidas pulsadas (rosa).

Fig. 11. Comparación entre la conductancia de salida calculada a partir de las medidas de Scattering (azul) y los valores obtenidos de las medidas pulsadas (rosa).

Las Figs. 10 y 11 muestran los resultados de la transconductancia y conductancia de salida comparando los valores modelados y las medidas pulsadas. Las diferencias no son muy significativas por debajo de  $V_{\rm gs}\approx 0.6$  V. Por encima de este valor, hay que tener en consideración la corriente de fuga en la puerta del transistor y, por lo tanto, el modelo de circuito aplicado en este trabajo no se corresponde con el verdadero comportamiento del dispositivo.

#### VI. CONCLUSIONES

En este documento se ha presentado un método paso a paso para obtener el modelo circuital de un dispositivo E-pHMET de AsGa a partir de medidas de parámetros-S. Para realizar estas medidas se ha utilizado un útil de medida diseñado y fabricado con este propósito, el cual permite una calibración LRL en los terminales del dispositivo, mientras que para calcular y ajustar los valores de los elementos se ha hecho uso de una herramienta matemática como Matlab©.

Se ha demostrado que el modelo extraído simula adecuadamente los parámetros-S del transistor en la banda de interés. A continuación se ha mostrado, mediante diferentes gráficas, la dependencia de los parámetros intrínsecos del modelo con la polarización. Estas gráficas demuestran que el comportamiento de estos elementos en los transistores de enriquecimiento es similar al que tienen los de deplexión. Finalmente, se han usado medidas pulsadas para validar del proceso propuesto.

#### **AGRADECIMIENTOS**

Este trabajo ha sido financiado por el Ministerio de Educación y Ciencia a través del Programa Nacional de Espacio, proyecto ESP2004-07067-C03-02 y la beca FPI BES-2005-6730.

## REFERENCIAS

- G. Dambrine, A. Cappy, F. Heliodore and E. Playez, "A New Method for Determining the FET Small-Signal Equivalent Circuit", *IEEE Trans. Microwave Theory and Techniques*, Vol. 36, No.7, pp.1151-1159, July 1988.

- [2] R. Tayrani, J.E. Gerber, T. Daniel, R.S. Pengelly and U. Rohde, "A New and Reliable Direct Parasitic Extraction Method for MESFETs and HEMTs", *Proceedings of the 23<sup>rd</sup> European Microwave Conference*, Madrid, Spain, September 1993, pp 451-453.

- [3] ATF-55143 Datasheet. Disponible en: www.avagotech.com.

- [4] "Applying the 8510 TRL Calibration for Non-Coaxial Measurements", Agilent Technologies Product Note 8510-8A, 2000.

- [5] M. Berroth and R. Bosch, "Broad-Band Determination of the FET Small-Signal Equivalent Circuit", *IEEE Trans. Microwave Theory and Techniques*, Vol.38, No.7, pp.891-895, July 1990.

- [6] P.H. Ladbrooke, "MMIC Design: GaAs FETs and HEMTs", Ed. Artech House. ISBN 0-89006-314-1.

- [7] J. L. Cano, T. Fernández y E. Artal, "Medida Dinámica de la Transconductancia a Temperaturas Criogénicas en Transistores EpHEMT", XXI Simposium Nacional de la Unión Científica Internacional de Radio, Libro de Actas – URSI2006, pp. 1666-1669, Oviedo 2006.