# ESCUELA TÉCNICA SUPERIOR DE INGENIEROS INDUSTRIALES Y DE TELECOMUNICACIÓN

# UNIVERSIDAD DE CANTABRIA

# Trabajo Fin de Grado

# Amplificador de potencia clase E insensible a la carga basado en MOSFET (Load insensitive MOSFET-based class E power amplifier)

Para acceder al Título de

Graduado en Ingeniería de Tecnologías de Telecomunicación

**Autor: Rolando Borbolla Rouco**

Julio - 2020

E.T.S. DE INGENIEROS INDUSTRIALES Y DE TELECOMUNICACION

# GRADUADO EN INGENIERÍA DE TECNOLOGÍAS DE TELECOMUNICACIÓN

# CALIFICACIÓN DEL TRABAJO FIN DE GRADO

Realizado por: Rolando Borbolla Rouco Director del TFG: José Ángel García García

Título: "Amplificador de potencia clase E insensible a la carga basado

en MOSFET"

Title: "Load insensitive MOSFET-based class E power amplifier"

## Presentado a examen el día:

para acceder al Título de

# GRADUADO EN INGENIERÍA DE TECNOLOGÍAS DE TELECOMUNICACIÓN

Fdo.: El Vocal Fdo.: El Director del TFG

(sólo si es distinto del Secretario)

V° B° del Subdirector Trabajo Fin de Grado N°

(a asignar por Secretaría)

# Resumen

En la actualidad, el desarrollo de tecnologías cada vez más eficientes se viene aplicando en muchos sectores. Su objetivo, disminuir, tanto la emisión de gases de efecto invernadero, provocados en gran parte por la generación de la energía eléctrica, como los costes de operación asociados al consumo de los equipos. En especial, dentro del campo de RF/Microondas, se están desarrollando sistemas de transmisión inalámbrica eficientes que, por ejemplo, permitan reducir el elevado consumo eléctrico de las estaciones base de telefonía móvil o aumentar la duración de las baterías en los terminales.

De este contexto, surge la idea del presente Trabajo de Fin de Grado, que consiste en llevar a cabo el diseño e implementación de un **amplificador de potencia insensible a la carga**, operando en **clase E**, a una frecuencia de **2 MHz**. Para el desarrollo del proyecto, se utilizó como base, el transistor **MOSFET IRF510** a **25 V**, para el cual, fue necesario la creación de un modelo sencillo de tipo conmutación que permitiese realizar las simulaciones en condiciones de **load pull**. Como resultado final, se obtuvo una potencia de salida de hasta **39.37 dBm** y un perfil de eficiencia similar en un  $\pm 10\%$  del ancho de banda (1.8 - 2.2 MHz).

El proceso seguido para la confección de este amplificador ha estado marcado por tres hitos principales. Primero, la necesidad de crear de un modelo sencillo de tipo conmutación para el **IRF510**. Luego, es necesario realizar una simulación bajo condiciones de **load pull** con la red de salida deseada. El último paso es encontrar un inversor de impedancias inductivo para colocar en la red de salida, el cual permita obtener la trayectoria óptima de modulación de la impedancia de carga y permitir mayores **Back offs**.

Por las prestaciones del amplificador diseñado, puede ser utilizado, principalmente, para aplicaciones de transferencia de potencia inalámbrica en la **banda ICM** de **2.45 MHz**. Debido a la proximidad entre la frecuencia de trabajo (2 MHz) y los 2.45 MHz de la banda ICM, podría implementarse fácilmente con ligeras modificaciones en los componentes de las redes de entrada y salida sintonizándolos a la nueva frecuencia.

Palabras clave: amplificador; clase E; insensible a la carga; MOSFET; 2 MHz; amplificador de potencia; Back off; load pull

# **Abstract**

Nowadays, the development of increasingly efficient technologies is being applied in many sectors. Its objective is to reduce both the emission of greenhouse gases, caused in large part by the generation of electrical energy, and the operating costs associated with the consumption of equipment. Particularly, within the RF/Microwave field, efficient wireless transmission systems are being developed, which, for example, allow reducing the high electrical power consumption of mobile phone base stations, or increasing the time among mobile phone's batteries discharge.

Within this frame of reference, the idea of this Final Degree Project arises, which covers accomplishing the design and implementation of a **load insensitive power amplifier**, operating in **class E**, at a frequency of **2 MHz**. This project's development has been based on the **IRF510**, a **MOSFET** transistor which needed the creation of a switching type simple model. This model should allow the simulations under **load pull** conditions instead of the model provided by the manufacturer which was not prepared for it. The design was made using the supply voltage of **25 V**. In this framework, the prototype was able to reach an output power up to **39.37 dBm** and hold on a similar efficiency profile within  $\pm$  **10**% of the bandwidth (1.8 - 2.2 MHz).

Three main milestones shepherded the process followed for the realization of this amplifier. First, the need to create a switching type simple model for the **IRF510**. Henceforth it is necessary to perform a simulation under load pull conditions using the desired output network. Finally, the last step, is to find an inductive impedance inverter to place it at the very end of the output network. Once this inverter is set properly, allows obtaining the optimal modulation path of the load impedance and higher **back offs** operations.

Due to the performance of the designed amplifier, it can be used mainly, for wireless power transfer applications in the **2.45 MHz ISM band**. Bearing in mind the proximity between the working frequency (2 MHz) and the 2.45 MHz of the ISM band, it can be easily synthesized with slight modifications to the input and output network components tuning them to the new frequency.

Keywords: amplifier; class E; MOSFET; 2MHz; power amplifier; load insensitive; load pull; Back off

# **Índice** general

| Resumen                 |                                                                    |        |                   |                                                                     |     |  |  |  |

|-------------------------|--------------------------------------------------------------------|--------|-------------------|---------------------------------------------------------------------|-----|--|--|--|

| Abstract Índice general |                                                                    |        |                   |                                                                     |     |  |  |  |

|                         |                                                                    |        |                   |                                                                     |     |  |  |  |

| A                       | grade                                                              | ecimie | ntos              |                                                                     | IX  |  |  |  |

| $\mathbf{A}$            | brevi                                                              | aturas | y acrón           | iimos                                                               | х   |  |  |  |

| 1.                      | Intr                                                               | oducc  | ión               |                                                                     | 1   |  |  |  |

|                         | 1.1.                                                               | Impor  | tancia de         | e la eficiencia en los sistemas de comunicaciones de nueva generaci | ón. |  |  |  |

|                         |                                                                    | Comp   | romiso <i>efi</i> | iciencia - linealidad                                               | 2   |  |  |  |

|                         | 1.2.                                                               | Objeti | vos               |                                                                     | 3   |  |  |  |

|                         | 1.3.                                                               | Estado | o del arte        |                                                                     | 4   |  |  |  |

|                         | 1.4.                                                               | Estruc | tura de la        | a memoria                                                           | 5   |  |  |  |

| 2.                      | Fun                                                                | damer  | ıtos Teór         | ricos de Amplificadores de Potencia.                                | 7   |  |  |  |

|                         | 2.1.                                                               | Nivel  | Hardware.         | e. El transistor MOSTEF                                             | 7   |  |  |  |

|                         | 2.2.                                                               | Nivel  | Circuital.        | Las Clases de Amplificación                                         | 10  |  |  |  |

|                         |                                                                    | 2.2.1. | Amplific          | cadores Lineales                                                    | 10  |  |  |  |

|                         |                                                                    |        | 2.2.1.1.          | Clase A                                                             | 11  |  |  |  |

|                         |                                                                    |        | 2.2.1.2.          | Clase B                                                             | 12  |  |  |  |

|                         |                                                                    |        | 2.2.1.3.          | Clase AB                                                            | 12  |  |  |  |

|                         |                                                                    |        | 2.2.1.4.          | Clase C                                                             | 13  |  |  |  |

|                         |                                                                    | 2.2.2. | Amplific          | cadores Conmutados                                                  |     |  |  |  |

|                         |                                                                    |        | 2.2.2.1.          | Clase D                                                             | 15  |  |  |  |

|                         |                                                                    |        | 2.2.2.2.          | Clase E                                                             | 15  |  |  |  |

|                         |                                                                    |        | 2.2.2.3.          | Clase F                                                             |     |  |  |  |

| 3.                      | El amplificador de potencia clase E conmutado a tensión cero (ZVS) |        |                   |                                                                     |     |  |  |  |

|                         | 3.1.                                                               | Descri | pción del         | circuito básico                                                     | 17  |  |  |  |

|                         | 3.2.                                                               | Funcio | onamiento         | del circuito                                                        | 20  |  |  |  |

|                         |                                                                    | 3.2.1. | Suposicio         | ones de simplificación                                              | 24  |  |  |  |

|    | 3.3.  | Análisis                                                                                      | 25         |

|----|-------|-----------------------------------------------------------------------------------------------|------------|

| 4. | Dise  | eño del amplificador de potencia clase E en AWR Microwave Office                              | 28         |

|    | 4.1.  | Obtención de las curvas IV del transistor                                                     | 28         |

|    | 4.2.  | Obtención del punto de trabajo del transistor                                                 | 31         |

|    | 4.3.  | Obtención de la potencia de saturación del transistor                                         | 34         |

|    | 4.4.  | Realización de la simulación de $load~pull$                                                   | 36         |

|    |       | 4.4.1. Simulación load pull con componentes ideales                                           | 36         |

|    |       | 4.4.2. Simulación con modelos de componentes reales                                           | 39         |

|    | 4.5.  | Creación de la red de salida del amplificador                                                 | 44         |

|    |       | 4.5.1. Ajuste con componentes ideales                                                         | 44         |

|    | 4.6.  | Ajuste con modelos de componentes reales                                                      | 47         |

| 5. | Imp   | olementación y medidas del Amplificador de Potencia.                                          | <b>5</b> : |

|    | 5.1.  | Introducción                                                                                  | 5          |

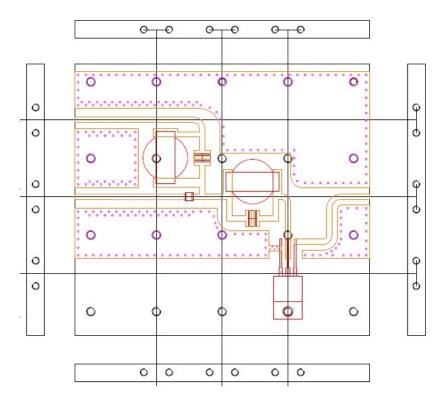

|    | 5.2.  | Diseño de la placa en AutoCad                                                                 | 5          |

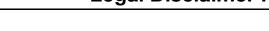

|    | 5.3.  | Síntesis de impedancias y medidas de load pull $\ \ldots \ \ldots \ \ldots \ \ldots \ \ldots$ | 52         |

|    | 5.4.  | Síntesis de impedancias                                                                       | 55         |

|    | 5.5.  | Medida de potencia y eficiencia del transistor en condiciones de $load~pull$                  | 56         |

|    | 5.6.  | Generación del fichero $load~pull~$ a partir de las medidas realizadas $\ldots \ldots \ldots$ | 57         |

|    | 5.7.  | Medidas del amplificador insensible a la resistencia de carga                                 | 58         |

|    | 5.8.  | Representación gráfica de los datos del amplificador insensible a la carga                    | 60         |

| 6. | Con   | nclusiones y Líneas Futuras                                                                   | 66         |

|    | 6.1.  | Conclusiones                                                                                  | 66         |

|    | 6.2.  | Líneas Futuras                                                                                | 67         |

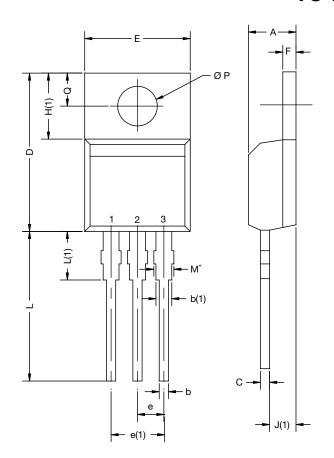

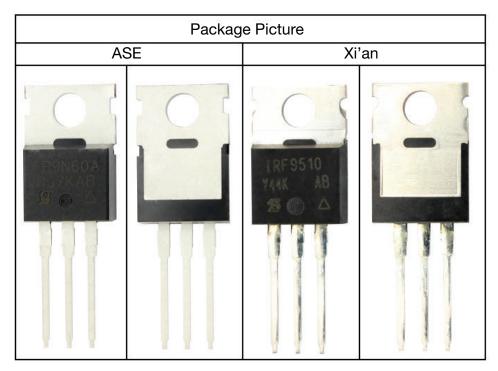

| Α. | AN    | EXO 1: Transistor MOSFET IRF510                                                               | 72         |

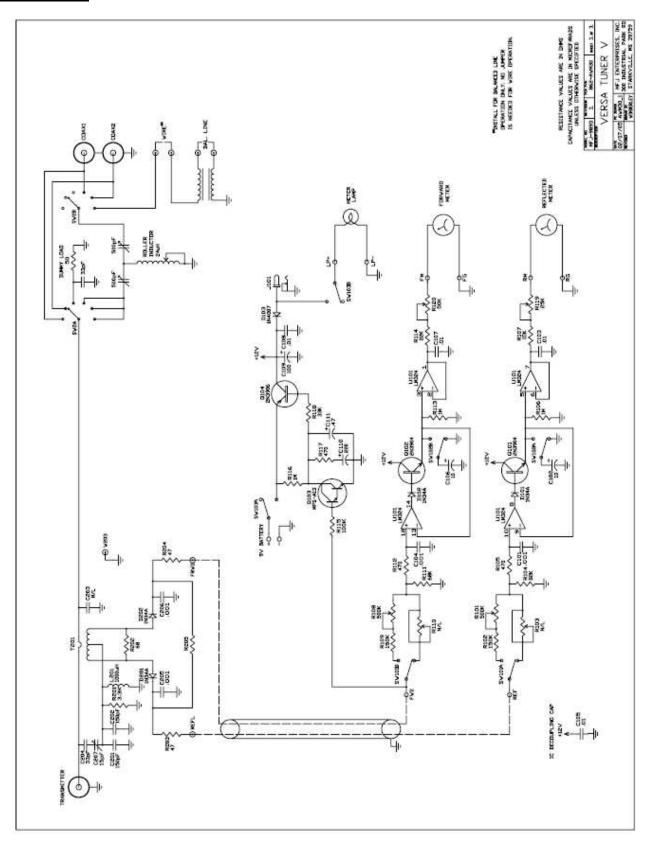

| в. | AN    | EXO 2: MFJ VERSA TUNER V                                                                      | 8          |

| C. | AN    | EXO 3: Bias Tee ZFBT-6GW-FT                                                                   | 102        |

| D. | AN    | EXO 4: Kit de bobinas Coilcraft DO5010H                                                       | 104        |

| Bi | bliog | grafía                                                                                        | 106        |

# Índice de figuras

| 1.1.  | A Google data centre. US researchers expect power consumption to triple in the next               |    |

|-------|---------------------------------------------------------------------------------------------------|----|

|       | five years as one billion more people come online in developing countries. Photograph:            |    |

|       | Google/Rex                                                                                        | 2  |

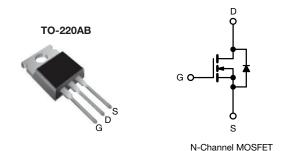

| 2.1.  | MOSFET de enriquecimiento de canal N                                                              | 8  |

| 2.2.  | MOSFET de enriquecimiento de canal N                                                              | 9  |

| 2.3.  | Principales clases de amplificación                                                               | 10 |

| 2.4.  | Definición del ángulo de conducción                                                               | 11 |

| 2.5.  | Esquema general del circuito de un amplificador de potencia clase B $\ \ldots \ \ldots \ \ldots$  | 12 |

| 2.6.  | Esquemas para modelar el transistor como conmutador                                               | 14 |

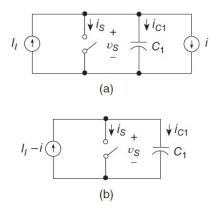

| 3.1.  | Circuito básico de un amplificador de potencia clase E                                            | 18 |

| 3.2.  | Circuito básico de un amplificador de potencia clase E $\dots \dots \dots \dots \dots$            | 19 |

| 3.3.  | Formas de onda óptimas de un clase E $(\mathbf{ZVS})$                                             | 22 |

| 3.4.  | (a) Circuito equivalente clase E con $V_I$ y $L_F$ sustituidas por la fuente de corriente $I_I$ y |    |

|       | el circuito resonante en serie sustituido por la fuente de corriente alterna $i$ . (b) Circuito   |    |

|       | equivalente con las dos fuentes de corriente $I_I$ e $i$ combinadas en una sola $(I_I-i)$         | 23 |

| 3.5.  | Circuito equivalente simplificado del amplificador y sus formas de onda                           | 24 |

| 4.1.  | Esquemático para la obtención de las curvas IV                                                    | 29 |

| 4.2.  | Representación gráfica de las curvas IV del modelo del fabricante                                 | 29 |

| 4.3.  | Modelo simplificado, tipo conmutador, del transistor IRF510                                       | 30 |

| 4.4.  | Curvas IV IRF510 vs Nuevo modelo                                                                  | 31 |

| 4.5.  | Modelo teórico del transistor IRF510                                                              | 32 |

| 4.6.  | Representación gráfica del $S_{22}$ del transistor                                                | 32 |

| 4.7.  | Modelo teórico del transistor IRF510                                                              | 33 |

| 4.8.  | Representación gráfica del $S_{22}$ del transistor                                                | 34 |

| 4.9.  | Representación gráfica del $S_{22}$ del transistor                                                | 35 |

|       | . Gráfico $P_{out}$ vs $P_{in}$ e $I_{DS}$ vs $P_{in}$                                            | 36 |

| 4.11. | . Esquemático para simulación de load pull                                                        | 37 |

| 4.12. | . Ecuaciones para la simulación de <b>load pull</b>                                               | 37 |

| 4.13. | . Contornos de load pull                                                                          | 38 |

|       | . Circuito abierto a $2f_0$                                                                       | 39 |

|       | . Circuito abierto a $2f_0$                                                                       | 40 |

| 4.16. | . Circuito resonante paralelo de alta impedancia a $f_0=2~MHz$                                    | 41 |

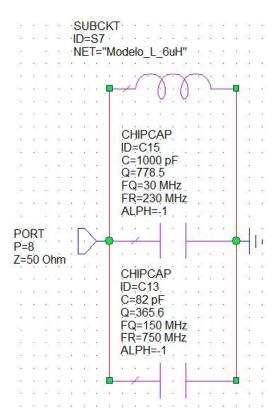

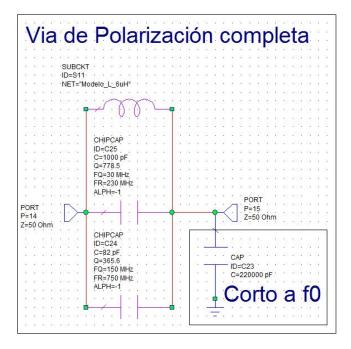

| 4.17. | Vía de polarización                                                                          | 42 |

|-------|----------------------------------------------------------------------------------------------|----|

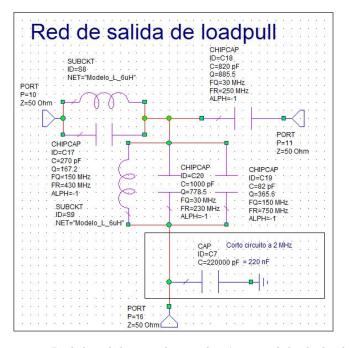

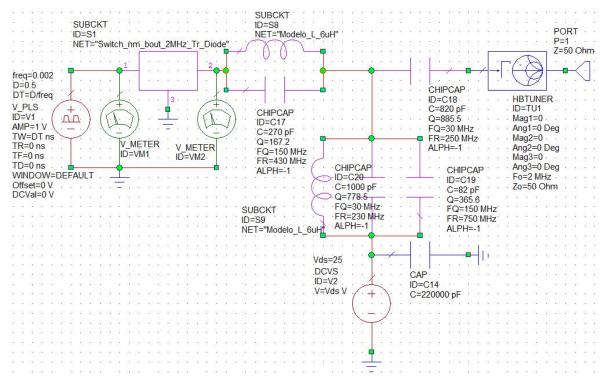

| 4.18. | Red de salida para la simulación y medida de $load~pull$                                     | 42 |

| 4.19. | Esquemático del load pull en el plano $RF_{OUT}$                                             | 43 |

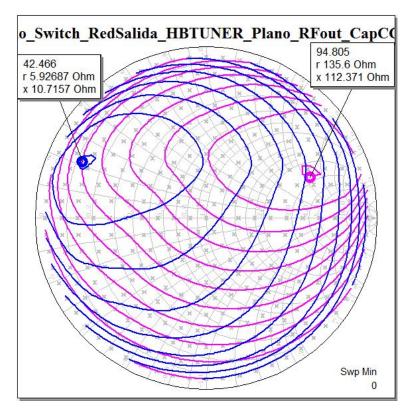

| 4.20. | Contornos de load pull en el plano $RF_{OUT}$                                                | 44 |

| 4.21. | Esquemático para ajustar la trayectoria óptima de la red de salida del amplificador          |    |

|       | insensible a la carga                                                                        | 45 |

| 4.22. | Trayectoria óptima de modulación de la resistencia de carga                                  | 47 |

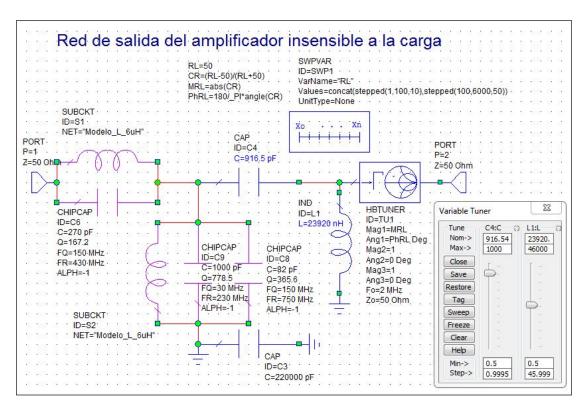

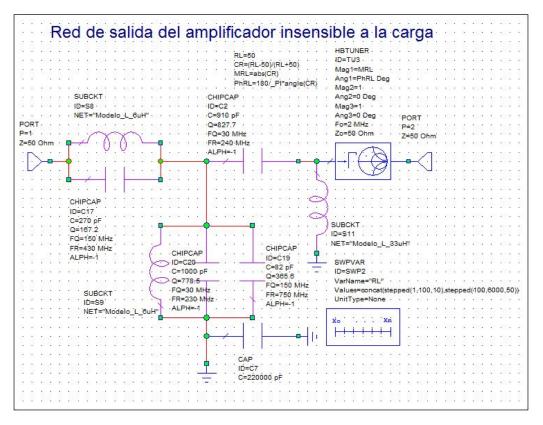

| 4.23. | Red de salida del amplificador insensible a la carga con modelos de componentes reales       | 48 |

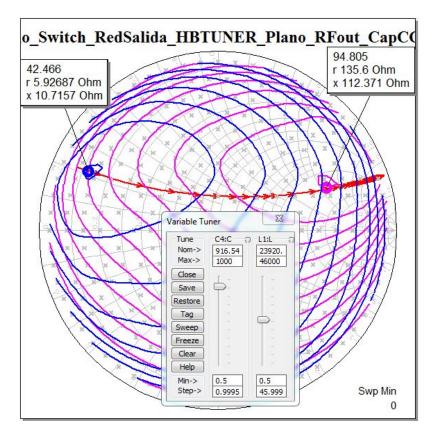

| 4.24. | Trayectoria de la red de salida del amplificador insensible a la carga ajustada con          |    |

|       | componentes reales                                                                           | 49 |

| 4.25. | Comparación de la trayectoria óptima con componentes ${f Reales}$ vs ${f Ideales}$           | 50 |

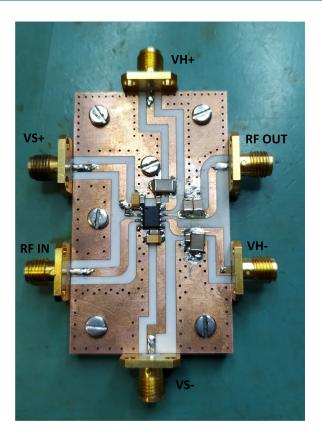

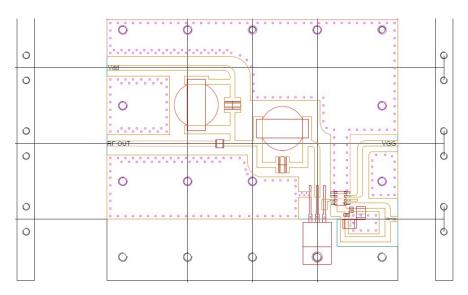

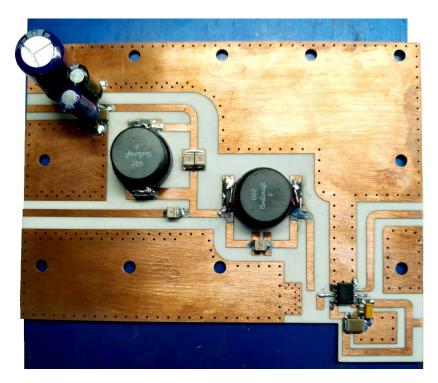

| 5.1.  | Placa de circuito impreso diseñada para la implementación y medida de la red de $load\ pull$ | 52 |

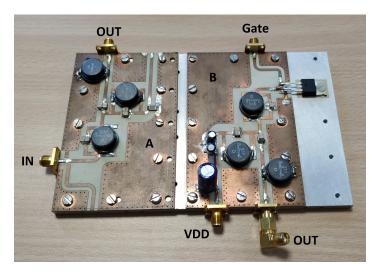

| 5.2.  | (A) Placa de síntesis de impedancias y (B) Placa de lo<br>ad pull $\ldots \ldots \ldots$     | 53 |

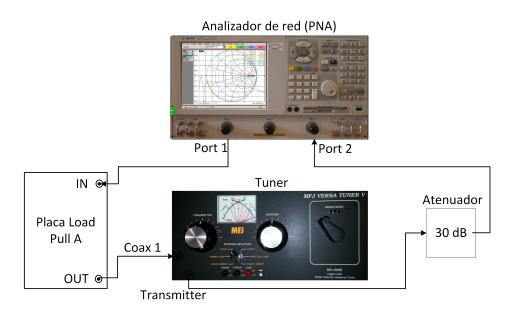

| 5.3.  | Diagrama funcional de síntesis de impedancias                                                | 53 |

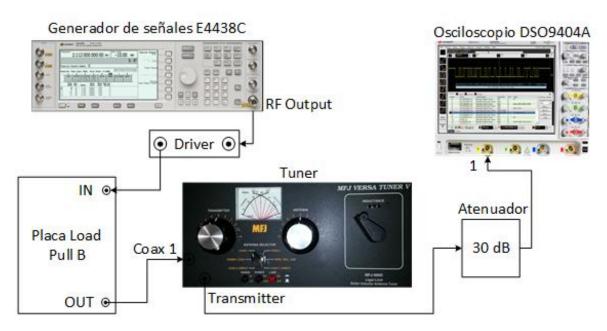

| 5.4.  | Diagrama funcional de medida de potencia y eficiencia en condiciones de $load\ pull$         | 54 |

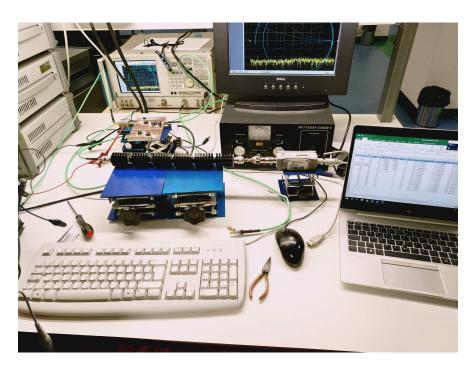

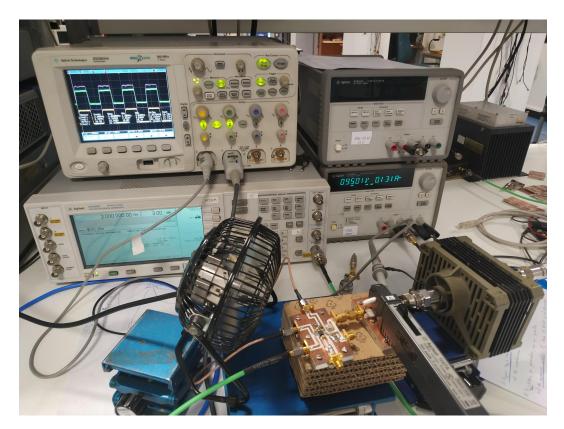

| 5.5.  | Banco de medidas para el amplificador                                                        | 55 |

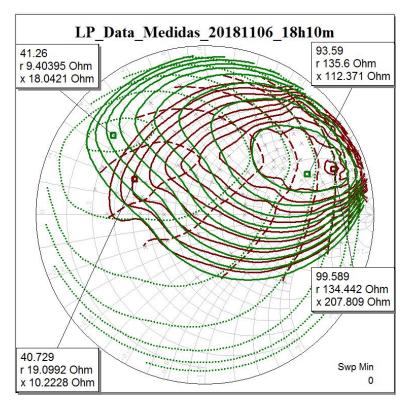

| 5.6.  | Representación gráfica LP Simulado vs LP Medidas Reales                                      | 57 |

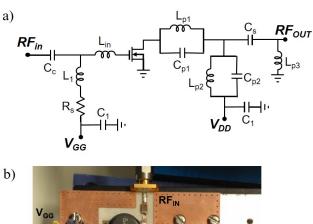

| 5.7.  | Circuito del amplificador insensible a la $R_L$                                              | 59 |

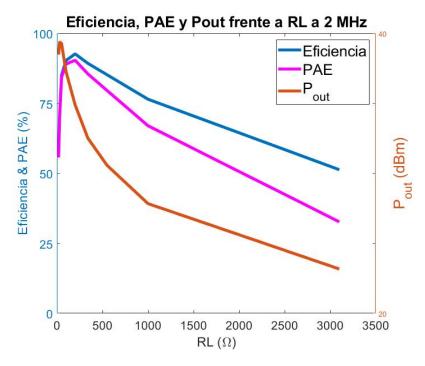

| 5.8.  | Eficiencia, PAE y $P_{OUT}$ frente a $R_L$                                                   | 60 |

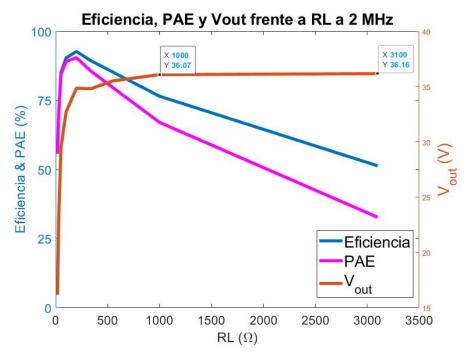

| 5.9.  | Eficiendia, PAE y $V_{OUT}$ frente a $R_L$                                                   | 6  |

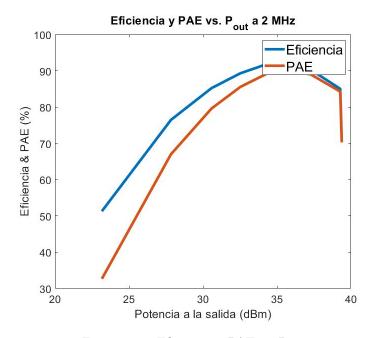

| 5.10. | Eficiencia y Power Added Efficiency (PAE) vs $P_{OUT}$                                       | 6  |

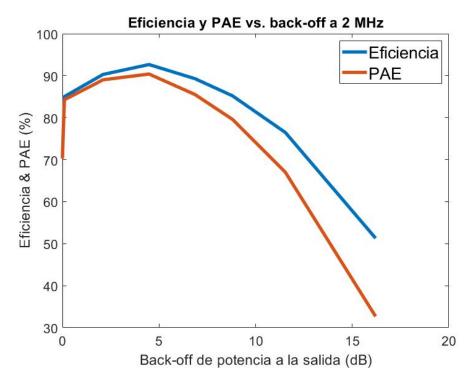

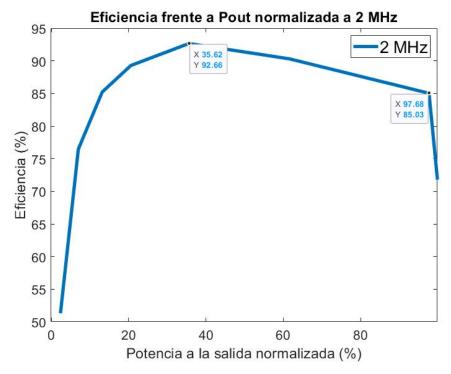

| 5.11. | Eficiencia y PAE vs Back-off                                                                 | 62 |

| 5.12. | Eficiencia vs $P_{OUT}(\%)$                                                                  | 62 |

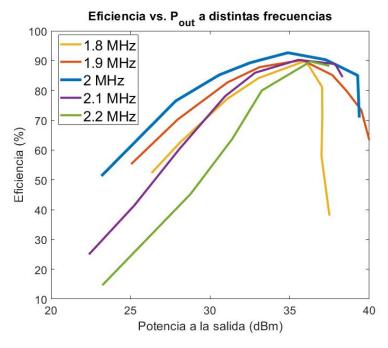

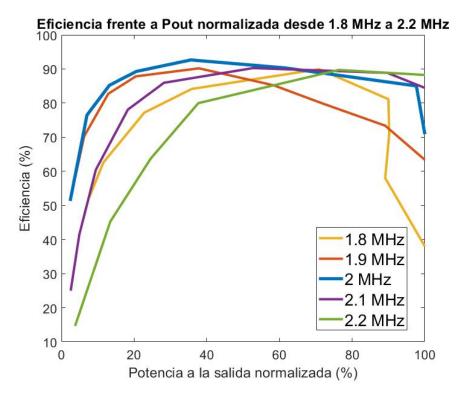

| 5.13. | Eficiencia v<br>s $P_{OUT}$ de 1.8 MHz a 2.2 MHz                                             | 63 |

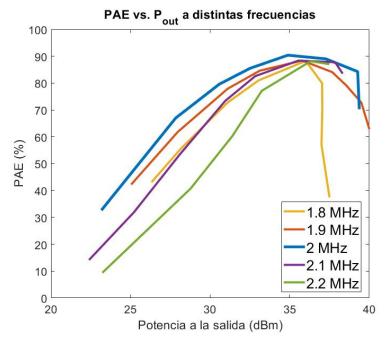

| 5.14. | PAE vs $P_{OUT}$ de 1.8 MHz a 2.2 MHz                                                        | 63 |

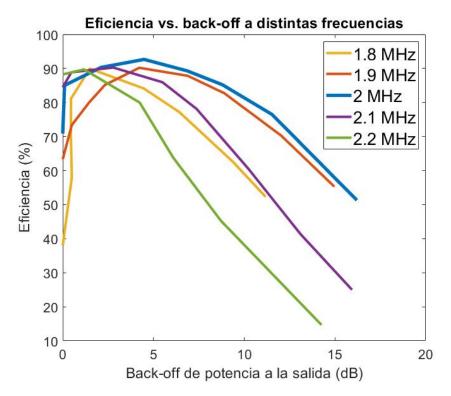

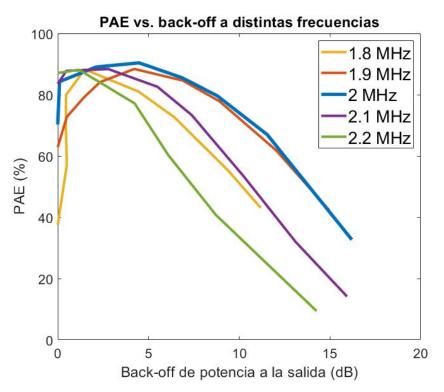

| 5.15. | Eficiencia vs Back-off de 1.8 MHz a 2.2 MHz                                                  | 64 |

| 5.16. | PAE vs Back-off de 1.8 MHz a 2.2 MHz $$                                                      | 64 |

| 5.17. | Eficiencia v<br>s $P_{OUT}(\%)$ de 1.8 MHz a 2.2 MHz                                         | 65 |

| 6.1.  | Placa prototipo para comprobar el rendimiento del Driver <b>EL7156</b>                       | 68 |

| 6.2.  | Banco de medidas para comprobar el rendimiento del Driver ${\bf EL7156}$                     | 69 |

| 6.3.  | Diseño autocad de la placa conjunta<br>Driver + Transistor                                   | 70 |

| 6.4.  | Prototipo para la integración conjunta del driver ${\bf EL7156}$ y el Metal Oxide Semicon-   |    |

|       | ductor Field-Effect Transistor (MOSFET) IRF510                                               | 70 |

Rolando Borbolla Rouco VIII

# **Agradecimientos**

Siempre faltarán palabras para agradecer a mi director de TFG, José Ángel García, por la paciencia y la dedicación que ha tenido conmigo y con este proyecto. Muchas gracias por todo lo que me has enseñado y por la oportunidad que me has dado de trabajar junto a ti durante algo más de un año tanto en este, como en otros proyectos. Gracias a tus enseñanzas me siento más preparado para comenzar a labrar mi propio futuro.

No puede faltar agradecer a todo el grupo de RF, David Vegas, María de las Nieves Ruiz y José Ramón Pérez. Aunque algunos de nuestros caminos se hayan separado, nunca olvidaré todo lo que me habéis apoyado y enseñado, lo amenas que hacíais las tardes y los descansos para tomar el café. Haber podido trabajar junto a vosotros durante tanto tiempo ha sido un placer.

Gracias a mi tía Magdalena y mis padres Mayda y Rolando por haber estado siempre pendientes y tirar de mí cuando me distraía y comenzaba a perder de vista mis obligaciones.

Gracias a Irene Martín, por estar a mi lado desde que mi vida universitaria comenzó. Gracias por celebrar conmigo las cosas buenas y apoyarme para superar lo malo. Gracias por tener la paciencia y el temple para decirme no solo lo bueno, sino también por ayudarme a rectificar mis malas decisiones.

# Abreviaturas y Acrónimos

$V_{TH}$  Tensión Threshold. 9, 23

AC Altern Current. 23, 25

ADS Advanced Design System. 51

AM Amplitud Modulation. 11, 15

AP Amplificador de Potencia. 3, 6, 11

**BJT** Bipolar Junction Transistor. 8

CW Continuous Wave. 58

**DC** Direct Current. 12, 23, 24

FET Field-Effect Transistor. 7, 8

FM Frequency Modulation. 16

**HF** High Frequency. 15

**JFET** Junction Field-Effect Transistor. 8

LF Low Frequency. 15

LNA Low Noise Amplifier. 3, 12

MOSFET Metal Oxide Semiconductor Field-Effect Transistor. 3–5, 7, 8, 27, 67, 70

PAE Power Added Efficiency. 61–64

PAPR Peak to Average Power Ratio. 2

PCB Printed Circuit Board. 51, 52, 69

TIC Tecnologías de la Información y las Comunicaciones. 1

**UHF** Ultra High Frequency. 16

VHF Very High Frequency. 16

**ZCS** Zero Current Switching. 17

**ZVDS** Zero Voltage Derivative Switching. 21, 24, 25

ZVS Zero Voltage Switching. 17, 20, 24, 25

CAPITULO

# Introducción

Según los alarmantes datos estadísticos recogidos por estudios realizados en diferentes medios técnicos del sector de las telecomunicaciones, para el año 2020 se estima que los miles de millones de dispositivos electrónicos conectados a la red generarán un aproximado de 3.5% de las emisiones de  $CO_2$  a la atmósfera, pudiendo llegar a ser hasta un 14% para el año 2040 [1] y [2].

Por otro lado, las predicciones indican que toda la industria de las telecomunicaciones será responsable del 20% del consumo de electricidad a nivel mundial, lo cual supera considerablemente sectores como el transporte marítimo y aéreo.

Dentro de todo lo concerniente a las **Tecnologías de la Información y las Comunicaciones (TIC)**, los centros de procesamiento de datos, denominados también Data Centre pueden llegar a consumir por sí mismos aproximadamente 1.9 Gt de carbón, lo que representa un 3.2% de las emisiones globales.

A partir de todos estos datos, la comunidad científica internacional está abocada a la necesidad de buscar sistemas y dispositivos cada vez más eficientes que ayuden a reducir el consumo energético.

Figura 1.1: A Google data centre. US researchers expect power consumption to triple in the next five years as one billion more people come online in developing countries. Photograph: Google/Rex

Como parte de este contexto de investigación e innovación, surge la posibilidad de emplear las diferentes clases de amplificadores. En el presente trabajo, se ha decidido utilizar un amplificador de potencia clase E debido a que este ofrece un mejor rendimiento en potencia y en el uso de los recursos energéticos; por eso se ajusta a los objetivos trazados en la sección 1.2.

# 1.1. Importancia de la eficiencia en los sistemas de comunicaciones de nueva generación. Compromiso eficiencia - linealidad

El paso de los años y el vertiginoso avance de las tecnologías de comunicaciones móviles, ha desembocado en un afán de conseguir velocidades de transmisión de datos cada vez más elevadas. A su vez, los retos que supone esta meta aumentan exponencialmente. Para lograr estos retos cada vez surgen señales mucho más complejas (LTE 4G) las cuales contienen un gran volumen de datos en un ancho de banda muy reducido (eficiencia espectral alta) y presentan elevados valores de relación entre su potencia pico y su potencia promedio o **Peak to Average Power Ratio (PAPR)**. Esto significa que este tipo de señales de nueva generación hacen que los sistemas de comunicaciones que trabajan con ellas, deban operar, de media, a niveles de potencia de varios **dB** por debajo de su máximo por diseño (típicamente entre 10 y 12 dB para señales LTE). A este hecho es a lo que se le llama trabajar en **Back-off**.

Esta cuestión conlleva la necesidad de crear nuevos equipos con una alta eficiencia a dichos niveles de Back-off y que, a su vez, sean capaces de responder a los picos de potencia de la señal de comunicaciones procurando su mínima distorsión posible.

Es en este punto donde entra en juego el compromiso entre eficiencia y linealidad. Es bien conocido que los amplificadores de bajo ruido (Low Noise Amplifier (LNA)), son dispositivos muy lineales, pero que no son nada eficientes. Sin embargo, esto no representa un problema relevante en su diseño debido a que se utilizan para operar con señales de muy baja potencia, por lo que su consumo de energía no es elevado, a pesar de la poca eficiencia. En cambio, para el diseño de un Amplificador de Potencia (AP) se necesita que este sea lo más eficiente posible aún a costa de sacrificar su linealidad. Esto se debe a que las señales con las que típicamente opera, presentan elevados niveles de potencia, lo que se traduce en altos niveles de potencia disipada en forma de calor. Por esta razón, eficiencias pobres pueden provocar fallos y averías graves de los componentes internos, o la necesidad invertir en fuentes de refrigeración superiores.

# 1.2. Objetivos

Con el presente Trabajo de Fin de Grado se han trazado varios objetivos. Como cuestión fundamental se define el diseño e implementación de un amplificador de potencia clase E insensible a la modulación de la impedancia de carga en la banda 160 metros. En este caso concreto, se trabaja a la frecuencia de 2 MHz utilizando un transistor de tecnología MOSFET.

Para conseguir los objetivos de eficiencia y linealidad que se pretenden, es de vital importancia tener en cuenta el uso de condensadores y bobinas de alto factor de calidad en las redes de entrada, salida, y vía de polarización. De esta manera se podrá obtener un diseño mucho más compacto.

Además de los aspectos anteriormente planteados, se pueden definir otras cuestiones no menos importantes como objetivos particulares:

- Estudio de las características de los transistores MOSFET.

- Análisis teórico del comportamiento de los amplificadores clase E.

- Modelización sencilla del funcionamiento del transistor MOSFET IRF510.

## 1.3. Estado del arte

A nivel mundial, estudiosos del tema han realizado proyectos de características similares al presentado en este Trabajo de Fin de Grado. La intención de esta sección es la de dar al lector, a través de unos pocos ejemplos, una visión aproximada que le permita comparar los resultados obtenidos tras la finalización de este proyecto, con los conseguidos por expertos de renombre en algunas publicaciones que se detallarán a continuación.

Los resultados que se mostrarán a continuación son un breve resumen de las prestaciones principales del amplificador diseñado. Para obtener más información acerca del proceso de medidas y el total de los resultados, será neccesario leer el Capítulo 5.

Como primer objeto de contraste, se va a tomar el trabajo realizado por Frederick H. Raab [3], quien es ingeniero jefe y propietario de la firma de consultoría e I+D, Green Mountain Radio Research. En [3], Raab propone un circuito amplificador clase E de banda ancha, utilizando un transistor MOSFET, que puede operar entre 1.8 MHz y 128 MHz. Los resultados de eficiencia en drenador que obtuvo con su trabajo fueron de 90 % a 1.8 MHz y 70 % a 128 MHz, siendo 90 % su pico de eficiencia a las frecuencias mas bajas. Por otro lado, la potencia de drenador medida para el mismo rango fue de entre 200 W a frecuencias bajas  $f \ge 1.8$  MHz; y 175 W a frecuencias cercanas al límite superior ( $f \le 128$  MHz). No debe pasarse por alto el mérito que tiene conseguir eficiencias superiores al 70 % en un ancho de banda tan grande, sabiendo que este tipo de dispositivos es sumamente sensible a los cambios de frecuencia.

En segundo lugar, se ha tomado como referencia "2.65 MHz High Efficiency Soft-Switching Power Amplifier System" [4]. Este trabajo fue realizado por Jinrong Qian y Gert Bruning y se utiliza el MOSFET de potencia MTP3N50E para conseguir un pico de eficiencia de 92.6 % y 100 W de potencia de salida. Este transistor es capaz de llegar hasta los 500 V de tensión de ruptura, lo que lo hace muy eficaz a la hora de entregar grandes potencias a la carga.

Para finalizar, es igual de importante destacar el trabajo de John F. Davis y David B. Rutledge [5]. En este artículo presentan su amplificador clase E a 13.65 MHz utilizando el transistor MOSFET IRFP450LC. Al igual que el transistor utilizado en el segundo ejemplo comparativo, este también es un MOSFET de potencia que soporta elevados valores de tensión de ruptura de drenador. Los resultados obtenidos por

estos dos investigadores son de un 86% de eficiencia y una potencia de salida de  $400~\mathrm{W}$ .

En contraste con estos tres trabajos citados, el transistor utilizado para este proyecto, es el MOSFET IRF510. Es un transistor que soporta una tensión de ruptura de drenador de 100 V y una frecuencia máxima de operación de entre 5 MHz y 10 MHz limitada por el tiempo de recuperación del diodo en antiparalelo. Teniendo en cuenta las características del transistor en cuestión, fue posible conseguir unos valores de 95.71 % de eficiencia, 20 dB de ganancia máxima y 40.56 dBm que equivale a 11.37 W de potencia entregada a la carga.

# 1.4. Estructura de la memoria

A continuación se indican brevemente los pasos seguidos en el diseño de este AP:

• Capítulo 2: Fundamentos Teóricos de los Amplificadores de Potencia.

En este capítulo, se tratan los temas de los transistores **MOSFET**, cómo surgieron, su funcionamiento, circuito equivalente y materiales de fabricación. Además, se comentan las diferentes clases de amplificación, haciendo especial mención a las clases de conmutación.

• Capítulo 3: El amplificador de potencia Clase E.

Este capítulo, como su nombre indica, se centra en los fundamentos teóricos de la clase E de amplificadores de potencia conmutados. Se presta especial atención a las formas de onda de la tensión y la corriente en distintos puntos del circuito clásico del amplificador clase E. Por último se presenta un breve resumen de las ecuaciones principales que describen el comportamiento de este tipo de amplificadores.

• <u>Capítulo 4</u>: Diseño del circuito del amplificador de potencia en el entorno de simulación AWR Design Environment.

Este capítulo aborda la simulación del comportamiento del transistor real, modelado del mismo y simulación en condiciones de *load pull*. Además, se simula la red de salida del amplificador invariante con la carga junto con su red de entrada.

• Capítulo 5: Implementación y medidas del AP.

En esta parte se describe desde el diseño de la placa de circuito impreso en Autocad, hasta el proceso de medición del amplificador completo. Además, se incluyen los resultados adjuntos en los anexos como hojas de Microsoft Excel.

• Capítulo 6: Conclusiones y líneas futuras.

Este capítulo resume todo lo conseguido con este Trabajo de Fin de Grado y además propone unas modificaciones que pueden conseguir mejorar el rendimiento del amplificador implementado.

CAPÍTULO CAPÍTULO

# Fundamentos Teóricos de Amplificadores de Potencia.

El avance de la tecnología, la aparición de señales espectralmente más eficientes y la evolución hacia sistemas **eco-friendly**, ha dado lugar al desarrollo de nuevas arquitecturas capaces de optimizar mejor el uso de los recursos disponibles en el ámbito de las comunicaciones y los sistemas de alimentación inalámbricas. Sin embargo, no menos importante es el progreso a nivel de hardware como el transistor de RF/microondas y a nivel de circuito, con el descubrimiento de las clases de amplificación conmutada.

## 2.1. Nivel Hardware. El transistor MOSTEF

El transistor MOSFET, por sus siglas del inglés Metal-Oxide-Semiconductor Field-Effect Transistor, es uno de los dispositivos más utilizados en la integración de sistemas digitales. Esta tecnología revolucionó la década de los 70 en aplicaciones de electrónica de potencia, ordenadores y en procesamiento de señales.

El principio básico de funcionamiento de la tecnología de transistores de efecto de campo, por sus siglas del inglés Field-Effect Transistor (FET), se remonta a la década de los años 1930, cuando Lilienfeld [6] y Heil [7] lo propusieron y patentaron. Los primeros intentos posteriores de explotar esta tecnología fueron fracasos, debido a la existencia de impurezas en la superficie de los materiales. Estas obstruían el flujo normal de los electrones a través del semiconductor, dificultando el funcionamiento de la mayoría de los dispositivos electrónicos basados en esta tecnología de materiales.

Dentro del marco de investigación y desarrollo, en aras de conseguir aplicar el concepto planteado previamente por [6] y [7], es cuando Bardeen y Brittain [8], descubren el transistor de unión bipolar (Bipolar Junction Transistor (BJT)) en el año 1947, al juntar dos uniones PN adyacentes en un único cristal de Germanio. En los años venideros, los avances en la tecnología de materiales semiconductores y el control de las impurezas de los mismos, alcanzados para conseguir mejorar las prestaciones de los ya mencionados BJT, permiten retomar el concepto de efecto de campo, inviable en sus inicios. Así, en 1952, Shockley propone por fin el primer dispositivo que seguía un principio de funcionamiento basado en las ideas planteadas originalmente por [6] y [7]. Este es el transistor de unión de efecto de campo (Junction Field-Effect Transistor (JFET)). Sin embargo, no es hasta principios de la década de los 60, cuando realmente los avances tecnológicos hicieron realidad la idea original de [6] y [7] al fabricar una variante de FET: el MOSFET.

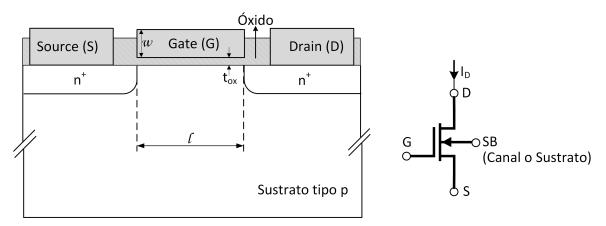

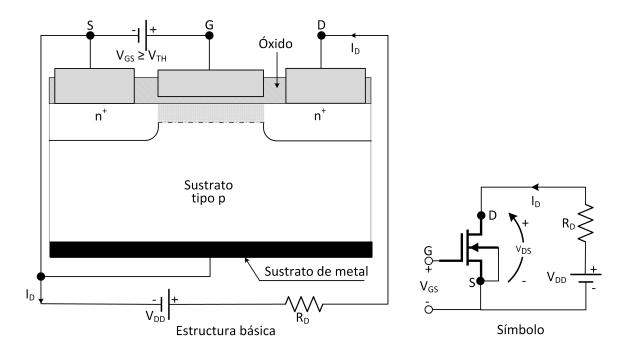

Existen diferentes variantes de este transistor. Una de sus clasificaciones se hace por el tipo de canal. Los hay que son de canal N, en los que los electrones circulan desde el terminal drenador (**D**) hacia el terminal fuente (**S**); y los hay de canal P, que funcionan a la inversa. La segunda distinción que existe entre ellos es por la forma en la que se controla el flujo de la corriente que circula por el canal. En este sentido existen dos subclases, los de enriquecimiento y los de empobrecimiento. El modelo de transistor utilizado para este proyecto es de **enriquecimiento de canal N**. Por consiguiente, se hace referencia a éste en la estructura básica y simbología que se muestran en la **Figura 2.1** a continuación.

Figura 2.1: MOSFET de enriquecimiento de canal N

En todos los transistores **MOSFET**, el electrodo de control de puerta se encuentra aislado del semiconductor por una fina capa de dióxido de silicio como se muestra en la **Figura 2.1**. Los parámetros de fabricación más importantes en este tipo de dispositivos

son los que se encuentran acotados en la misma figura. La longitud l representa la longitud del electrodo de puerta y coincide con la longitud del canal de conducción de portadores libres. El parámetro w es el ancho que tiene el electrodo metálico de la puerta del transistor. Finalmente,  $t_{OX}$  se corresponde con el parámetro que representa la anchura de la capa de óxido que se encuentra entre el terminal metálico de la puerta y el sustrato del transistor.

El funcionamiento de este tipo de transistores es relativamente sencillo de explicar y entender. La aplicación de un potencial positivo en el terminal ( $\mathbf{G}$ ), produce una reacción en los portadores del sustrato tipo  $\mathbf{p}$ , tal que los repele fuera de la zona cercana a la frontera entre la capa de óxido y el propio sustrato, formando una pequeña región de inversión (**portadores de tipo n**). A medida que el potencial positivo aumenta, la capa de inversión lo hace por igual, hasta que llegado un cierto umbral Tensión Threshold ( $V_{TH}$ ), la región de inversión es lo suficientemente grande como para permitir el paso de los portadores libres en la dirección drenador-fuente. En la **Figura 2.2** a continuación se muestra lo que sucede dentro del transistor cuando se supera el nivel de tensión umbral en el electrodo de puerta

Figura 2.2: MOSFET de enriquecimiento de canal N

# 2.2. Nivel Circuital. Las Clases de Amplificación

Partiendo de los conceptos abordados anteriormente, en esta sección se abordan las distintas técnicas de amplificación de radiofrecuencia a nivel de circuito. Las bases teóricas que se van a tratar en este epígrafe han sido extraídas del libro de Marian K. Kazimierczuk [9] y, de la Tesis Doctoral de Reinel Marante Torres [10] dado que están basados en los mismos fundamentos.

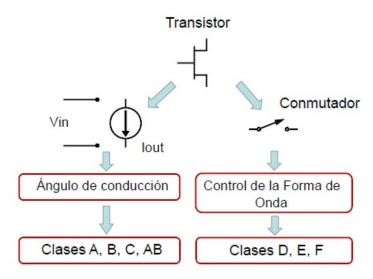

Dentro de lo que son los amplificadores, existen dos grandes grupos en los que se pueden separar este tipo de circuitos. En una de ellas el amplificador se comporta como un elemento de transconductancia, es decir, una fuente de corriente controlada por la tensión de puerta y se conocen como **amplificadores lineales**. En la otra rama los transistores operan como conmutadores y por tanto se denominan **amplificadores conmutados**. Esta clasificación se muestra en la **Figura 2.3**.

Figura 2.3: Principales clases de amplificación

### 2.2.1. Amplificadores Lineales

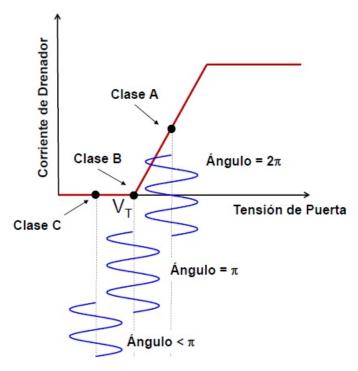

La clasificación de los amplificadores lineales, también llamados amplificadores modo fuente de corriente controlada, como lo son las clases A, B, C y AB, se hace en función del ángulo de incidencia de la forma de onda de la tensión de entrada. Este ángulo es el que define qué parte del ciclo de la señal de RF de entrada es la que se transforma en corriente a la salida del transistor [11]. En la **Figura 2.4** se muestra de manera gráfica este concepto.

Figura 2.4: Definición del ángulo de conducción

#### 2.2.1.1. Clase A

Un transistor funciona como un amplificador de potencia clase A cuando se encuentra polarizado de forma que siempre está en su región de saturación. En esta zona, la corriente de drenador es linealmente dependiente de la tensión aplicada en la puerta. Por esta razón los **AP clase A** se utilizan como fuentes de corriente controladas por la tensión de entrada.

En esta clase de operación, el ángulo de conducción de la corriente de drenador es  $2\pi$ , o lo que es lo mismo, conduce durante todo el período de la forma de onda de entrada. Así pues, se puede conseguir una amplificación muy lineal que da lugar a una réplica amplificada del voltaje o de las formas de onda de la corriente de entrada. Esta condición se consigue cuando la tensión de puerta  $(V_{GS})$  es mayor que el voltaje umbral del transistor  $(V_{TH})$ .

Este tipo de amplificador tiene una eficiencia ideal máxima del 50 % debido a que, incluso en ausencia de señal de entrada, el transistor se encuentra en estado de saturación, disipando cierta cantidad de potencia. Típicamente, estos amplificadores se utilizan tanto en etapas de pre-amplificación, como para trabajar con señales de radio moduladas en amplitud (Amplitud Modulation (AM)), por su bajo grado de componentes

armónicas. Un ejemplo de ello es el amplificador LNA de un receptor de comunicaciones.

#### 2.2.1.2. Clase B

El circuito de un amplificador de potencia RF clase B está formado por un transistor, un circuito resonante en paralelo y un bloqueador (choke) de RF a la frecuencia de trabajo (**Figura 2.5**). En este caso, el punto de trabajo se encuentra justamente en el límite entre la región activa o lineal y la región de corte ( $V_{GS} = V_{TH}$ ). Esta condición supone ciclos de conducción de corriente de drenador de medio período de onda ( $\pi$ ). En caso de no haber conducción, la corriente es cero. Este último hecho permite que no exista consumo en ausencia de señal de entrada, aumentando la eficiencia en condiciones ideales hasta un 78.5 %.

Figura 2.5: Esquema general del circuito de un amplificador de potencia clase B

La operación en clase B se caracteriza por una tensión promedio (**Direct Current** (**DC**)) de drenador constante y, a diferencia del clase A, una corriente media de drenador creciente con el aumento de potencia, y proporcional a la amplitud de la señal de entrada. Debido a esto, el amplificador clase B tiene un comportamiento lineal aunque no tanto como el clase A, por la generación de componentes de distorsión de orden par fuera de banda.

#### 2.2.1.3. Clase AB

Es un compromiso entre la clase A y la clase B, tanto desde el punto de vista de eficiencia como de ganancia en potencia y linealidad. El punto de trabajo, en este caso, es tal que el ángulo de conducción está comprendido entre algo más de  $180^{\circ}$  y bastante menos de  $360^{\circ}$ .

La operación en clase AB proporciona, al igual que la clase A, una señal de salida altamente lineal con respecto a la señal de entrada, ya que, durante la conducción, el comportamiento del dispositivo es bastante lineal. En sistemas de banda ancha, usualmente se configuran como un par *push-pull*, el cual combina medias sinusoides desde cada amplificador, formando a la salida una onda sinusoidal.

Su comportamiento en distorsión, es diferente y algo inferior al de clase A. Por ello, esta modalidad de amplificación se emplea en amplificadores lineales con no tan severas exigencias de linealidad como las aplicaciones que requieren clase A pura.

### 2.2.1.4. Clase C

En el amplificador clase C, el transistor se polariza en la región de corte o pinch-off  $(V_{GS} < V_{TH})$ , y la carga se acopla mediante un circuito LC en paralelo, sintonizado a la frecuencia de la señal de entrada. Para ello, se sigue el mismo esquema que circuito equivalente del amplificador de potencia clase B mostrado en la **Figura 2.5**. El transistor se encuentra en estado de corte la mayor parte del período de la señal de entrada, amplificando solamente durante cortos intervalos de tiempo (ángulo de conducción de la corriente de drenador menor que  $\pi$ ). Se puede decir que el transistor funciona prácticamente como un conmutador.

Esta clase es más eficiente que las anteriormente descritas a costa de reducir la linealidad. Puede llegarse teóricamente a eficiencias del 100%, a medida que el ángulo de conducción se aproxima a cero. Sin embargo, esto conlleva una disminución de ganancia al tiempo que la potencia de excitación necesaria para que el transistor conduzca aumenta. La respuesta de un clase C es esencialmente no lineal, incluso para la frecuencia fundamental.

#### 2.2.2. Amplificadores Conmutados

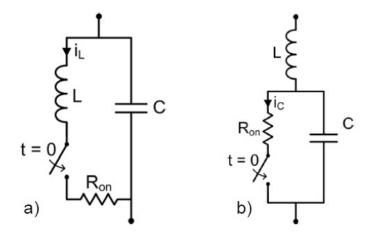

La principal diferencia distinguible entre estas clases de amplificación y las mencionadas en el apartado anterior, es que las clases conmutadas se utilizan, como su nombre bien indica, como conmutadores de muy alta velocidad en lugar de como fuentes de corriente controlada. El modelo de topología circuital propuesta por numerosos autores para este tipo de amplificadores se presenta en la **Figura 2.6**. La inductancia y la capacidad presentes en ambos modelos, hacen referencia a la propia inductancia del hilo de *bonding* y la capacidad de salida. Ambas están presentes en todos los transistores

por fabricación.

Figura 2.6: Esquemas para modelar el transistor como conmutador

Mayormente, los dispositivos de microondas se describen mucho mejor con el modelo de la **Figura 2.6b**. En este caso, la capacidad aparece en paralelo con el elemento de conmutación, mientras que la inductancia en serie, que no es más que un parásito extrínseco fundamentalmente debido al empaquetado, se encuentra fuera de la sección que representa al transistor real. Ambos modelos incluyen una resistencia de conducción finita  $(R_{ON})$ , que modela la pendiente de la región lineal que se puede observar en los gráficos característicos de Corriente-Tensión de un transistor.

En amplificadores de potencia conmutados, el conmutador se abre y se cierra periódicamente con la señal de entrada de RF como estímulo. Para el modelo b) de la **Figura 2.6**, cualquier tensión presente sobre el conmutador cuando éste se cierra, resultaría en una potencia disipada en la resistencia Ron ([9],[10]) que responde a la ecuación:

$$P_{C,Loss} = \frac{1}{2}CV_{DD}^2f \tag{2.1}$$

Donde  $P_{C,Loss}$  es la potencia disipada en  $R_{ON}$  y las variables que influyen en ella, C=Capacidad de salida del transistor,  $V_{DD}=$  Tensión en drenador y por último f=frecuencia de trabajo

De cara a maximizar la eficiencia y asegurar una correcta operación en alta frecuencia, es crucial asegurar que Vc sea cero al cerrar el conmutador para evitar los efectos descritos en la ecuación 2.1. Mediante un diseño cuidadoso de la red de salida del transistor, se puede lograr la conmutación a tensión nula. En ese sentido, se han desarrollado varias clases de amplificadores de potencia en modo conmutado.

#### 2.2.2.1. Clase D

Esta modalidad de amplificador fue inventada por Baxandall en 1959 [12]. A este tipo de amplificadores también se les llama inversores resonantes de potencia, del inglés dc-ac resonant power inverters como bien se indica en el capítulo 4.1 de [9]. Además de ser utilizados como conversores de energía de continua a alterna, también son utilizados en los transmisores de radio, como convertidores **DC-DC** y en lámparas fluorescentes.

La señal de entrada es una sinusoide con amplitud suficiente para producir la saturación y el corte de los transistores en el momento adecuado. Las formas de onda de tensión y corrientes están desfasadas 180°. Esto permite que sólo circule corriente cuando la tensión en el transistor es nula, y viceversa. Este es el principio básico de funcionamiento en modo conmutado y con él se permite conseguir, de manera ideal, que no existan pérdidas por disipación de potencia por la conducción en el transistor.

#### 2.2.2.2. Clase E

Esta clase de amplificadores de potencia, es la base en la que se fundamenta este Trabajo de Fin de Grado en cuanto a nivel de circuito se refiere. Es una de las clases de conmutación más utilizada a nivel global en el campo de las telecomunicaciones, especialmente para radiodifusión, fabricación de inversores **DC-DC** y otras muchas aplicaciones.

De manera que la explicación de los fundamentos teóricos de esta tecnología sea lo suficientemente consistente, en esta subsección del Capítulo 2 simplemente se va a hacer referencia a estos amplificadores. En cambio, el Capítulo 3 se va a centrar específicamente en esta clase, intentando exponer sus principios básicos de funcionamiento, descripción circuital, y un análisis de sus formas de onda.

#### 2.2.2.3. Clase F

Los amplificadores clase F utilizan circuitos resonantes multiarmónicos en la red de salida del amplificador con el objetivo de dar forma a la tensión drenador-fuente ( $V_{DS}$ ) de manera que se reduzcan las pérdidas del transistor y se maximice la eficiencia. A este tipo de circuitos también se le conoce con el nombre de amplificadores de potencia multiresonantes. Esta clase ha sido ampliamente utilizada para transmisores de radio AM de alta potencia desde las bandas de baja frecuencia (Low Frequency (LF)), que comprende el rango 30-300 kHz, hasta alta frecuencia (High Frequency (HF)), cuyo rango es 3-30 MHz. Para su uso en estas aplicaciones, la red resonante multiarmónica

de la clase F se basaba en la utilización de elementos concentrados para la construcción de los filtros de bloqueo del tercer armónico, o de los armónicos tercero y quinto.

Esta tecnología es igualmente aplicable para su inclusión en transmisores de radio Frequency Modulation (FM) en bandas que abarcan desde Very High Frequency (VHF)[13] (30 – 300MHz), hasta Ultra High Frequency (UHF) en el rango 0.3 - 3GHz [14]. Sin embargo, para estas aplicaciones a mayor frecuencia se utilizaban con una variación en su red de salida. En estos casos se utilizaban líneas de transmisión de cuarto de longitud de onda  $(\frac{\lambda}{4})$  para el control de los armónicos.

CAPÍTULO

# El amplificador de potencia clase E conmutado a tensión cero (ZVS)

Existen dos tipos de amplificadores de potencia clase E: el de conmutación a tensión cero (**Zero Voltage Switching (ZVS)**) y el de conmutación a corriente cero (**Zero Current Switching (ZCS)**). Estos amplificadores son los que mayor eficiencia ofrecen en comunicaciones. Sus formas de onda de tensión y corriente, desfasadas **180º**, permiten conmutaciones con mínimos de disipación de potencia en el transistor. Dicho desfase permite que no exista solapamiento entre ambas formas de onda.

La potencia instantánea consumida o disipada por cualquier dispositivo electrónico no es más que el producto de las formas de onda de la tensión por la corriente. Esto quiere decir que, si para cada instante de tiempo, sólo una de las dos formas de onda es distinta de cero, la potencia media disipada por el dispositivo en cuestión (el transistor **MOSFET** en este caso) será nula. Este planteamiento sólo se cumple de manera teórica, puesto que no es posible conseguirlo con componentes reales debido a las pérdidas físicas de los materiales, pero sí es posible asegurar que se minimiza el tiempo en el que existe solapamiento para alcanzar elevados valores de eficiencia.

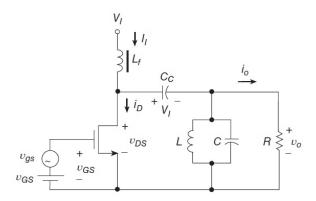

# 3.1. Descripción del circuito básico

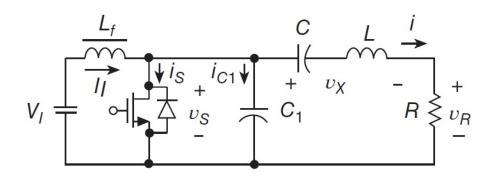

Introducidos por N. Sokal y A. Sokal en 1975 [15], esta clase de amplificadores de potencia presenta un circuito como el mostrado en la **Figura 3.1** [9]. En dicha figura, el transistor representa un conmutador seguido de una red de carga compuesta por

un condensador en paralelo  $C_1$  (que puede ser la capacidad de salida inherente del transistor) y un filtro serie (C + L) adaptado a la frecuencia fundamental de modo que ofrezca una condición de circuito abierto a los armónicos superiores. Por otro lado,  $L_f$  es la bobina de *choke* que se utiliza en la polarización para bloquear cualquier componente de alterna y dejar pasar solamente  $\mathbf{DC}$ .

Figura 3.1: Circuito básico de un amplificador de potencia clase E

El transistor trabaja solamente en los estados de conducción (ON) y corte (OFF). Cuando se encuentra conduciendo, el circuito resonante se convierte en un circuito L, C y R porque la capacidad  $C_1$  se encuentra en corto circuito por el conmutador. Sin embargo, cuando el transistor se encuentra operando en la región de corte, el circuito cambia. En este caso el circuito resonante se compone de todos los elementos de la red  $(C_1, C, L y R)$ , de donde la capacidad equivalente del circuito resonante sería inferior tanto a C como a  $C_1$ .

$$C_{eq} = \frac{CC_1}{C + C_1} \tag{3.1}$$

La red de carga del transistor presenta dos frecuencias de resonancia y factor de calidad. Uno es cuando el transistor se encuentra conduciendo y el otro cuando está en corte [9].

- 1. Cuando el transistor se encuentra conduciendo:

- la frecuencia de resonancia se obtiene según la expresión:

$$f_{o1} = \frac{1}{2\pi\sqrt{LC}}\tag{3.2}$$

• y el factor de calidad asociado a dicho estado:

$$Q_{L_1} = \frac{\omega_{o1}L}{R} = \frac{1}{\omega_{o1}CR}$$

(3.3)

- 2. mientras que cuando está en corte

- la frecuencia de resonancia es

$$f_{o2} = \frac{1}{2\pi \sqrt{\frac{LCC_1}{C+C_1}}} = \frac{1}{2\pi \sqrt{LC_{eq}}}$$

(3.4)

• y el factor de calidad

$$Q_{L_2} = \frac{\omega_{o2}L}{R} = \frac{1}{\omega_{o2}RC_{eq}}$$

(3.5)

Una vez analizadas las ecuaciones presentadas (Ec 3.1–Ec 3.5), es relativamente fácil encontrar la relación que existe entre ellas:

$$\frac{f_{o1}}{f_{o2}} = \frac{Q_{L_1}}{Q_{L_2}} = \sqrt{\frac{C_1}{C_1 + C}} \tag{3.6}$$

Para una operación a una frecuencia superior a la de resonancia  $f > f_{o1}$ , el circuito equivalente del **AP** se comporta como una carga inductiva como se muestra en la **Figura 3.2**. Debido a que a medida que se aumenta la frecuencia de trabajo, la reactancia inductiva también lo hace, es que la bobina (L) representada en la **Figura 3.1** se puede dividir en dos elementos  $L_a + L_b$  [9].

Figura 3.2: Circuito básico de un amplificador de potencia clase E

Cuando se trabaja en este caso, la frecuencia de resonancia y el factor de calidad de la carga cambian respecto a los que se obtienen con las ecuaciones anteriores.

• Primero, la frecuencia de resonancia no es la que era, sino

$$f_{o_a} = \frac{1}{2\pi\sqrt{L_aC}}\tag{3.7}$$

• y el nuevo factor de calidad es

$$Q_L = \frac{\omega L}{R} = \frac{\omega (L_a + L_b)}{R} = \frac{1}{\omega CR} + \frac{\omega L_b}{R}$$

(3.8)

# 3.2. Funcionamiento del circuito

En la sección 2.2.2 del Capítulo 2, se mencionó que en el caso de los amplificadores de conmutación, existen ciertas pérdidas debido precisamente al hecho de conmutar entre los estados de corte y conducción. Como se ha explicado en la sección 3.1, existe una capacidad de salida en paralelo con los terminales drenador y fuente del transistor, que almacena energía durante el estado de corte según [9]:

$$W = \frac{1}{2}CV_{DD}^2 (3.9)$$

En el momento de la transición de corte a conducción, la energía anteriormente almacenada es abruptamente disipada en forma de calor en la resistencia  $r_{DS}$  del transistor. Por esta razón las pérdidas de conmutación son como las mencionadas en 2.2.2 en la que la frecuencia toma lugar por ser la que marca el número de conmutaciones que hace el transistor en un período de tiempo dado (período de la forma de onda):

$$P_{C,Loss} = \frac{1}{2}CV_{DD}^{2}f (3.10)$$

La forma de evitar estas pérdidas es relativamente fácil. De lo que se trata es de conseguir que la tensión en el terminal drenador del transistor sea cero en el instante en que éste entra en conducción. Para que esto ocurra, no puede haber energía almacenada en ningún otro componente de la red resonante. Si se observa el circuito de la **Figura 3.2**, esto es lo mismo que hacer que la tensión:

$$v_S(t_{turn-on}) = 0 (3.11)$$

Este es uno de los principios fundamentales de un amplificador clase E. La expresión matemática que describe este comportamiento se representa de la siguiente forma:

$$v(\omega t)|_{\omega t = 2\pi} = 0 \tag{3.12}$$

Es importante tener en cuenta que para conseguir la condición **ZVS**, es necesario que la frecuencia de operación (f) sea superior a la frecuencia de resonancia  $(f_{o1} = \frac{1}{2\sqrt{LC}})$ , cosa que no siempre sucede. Según [9], la forma de onda de la corriente (i) que circula

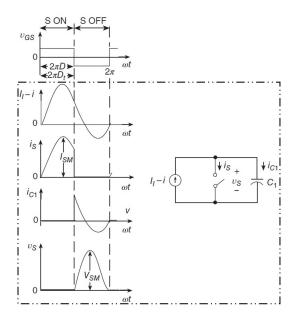

por el circuito resonante de carga, mantiene una estrecha relación con el factor de calidad del mismo  $(Q_L)$ . En [9] también se pone como ejemplo el caso de, si el factor de calidad es bueno  $(Q_L \ge 2,5)$ , la forma de onda de la corriente es aproximadamente sinusoidal como la que se aprecia en el gráfico número 2 de la **Figura 3.3**. En cambio, cuando se tiene el caso contrario y  $Q_L$  es bajo, entonces la forma de onda de la corriente se asemeja a la forma de una función exponencial [16].

Existe una segunda condición que también cumple la clase E. La condición de conmutación a derivada de la tensión igual a cero, de sus siglas en inglés Zero Voltage Derivative Switching (ZVDS). Esta evita los cambios bruscos de la forma de onda de la tensión en el terminal drenador, asegurando una transición suave entre los dos estados de conmutación,

$$\left. \frac{dv(\omega t)}{d\omega t} \right|_{\omega t = 2\pi} = 0 \tag{3.13}$$

en consecuencia, el condensador no transfiere corriente al transistor hasta que éste no está completamente conduciendo.

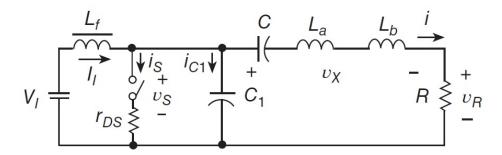

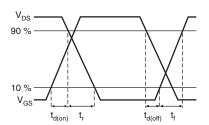

Al cumplirse estas dos condiciones (ecuaciones 3.12 y 3.13), se consiguen unas formas de onda como las que se muestran en la **Figura 3.3**.

Figura 3.3: Formas de onda óptimas de un clase  $E(\mathbf{ZVS})$

Analizando los gráficos de las formas de onda que aparecen en la **Figura 3.3**, se hacen notar las dos condiciones mencionadas con anterioridad. En el primer gráfico de la figura, se representa la forma de onda de la tensión en puerta. Dado que se está utilizando el transistor como un conmutador, basta con aplicar una excitación en la entrada que consiga hacer que el transistor conmute entre los dos estados posibles  $(\mathbf{ON}/\mathbf{OFF})$  y es por esto que la forma de onda de la tensión  $v_{GS}$  es cuadrada.

Posteriormente, en el tercer gráfico, se representa la forma de onda de la corriente en el terminal de drenador. Esta forma de onda está formada por dos componentes. Una de ellas es la corriente que proviene de la fuente de alimentación  $(I_I)$ , representada en el segundo gráfico. La localización y sentido de esta variable se puede ver en la

Figura 3.2. Observando en detalle la forma de onda sinusoidal de dicho gráfico, es destacable que ésta se encuentra montada sobre un cierto valor de  $\mathbf{DC}$ . Este valor de es la consecuencia de la  $I_I$  mencionada anteriormente. Entonces, ¿a qué se debe la forma de onda sinusoidal? Esta forma de onda se debe a que el circuito resonante de carga (LCR) se comporta como una fuente de corriente adicional de tipo alterna (Altern Current (AC)). De ahí que ambas fuentes de corriente se combinen dando lugar a una onda sinusoidal (i) desplazada con un offset equivalente a la corriente de continua  $I_I$ . El circuito equivalente que se corresponde con esta explicación se puede ver en la Figura 3.4(a) que se muestra a continuación.

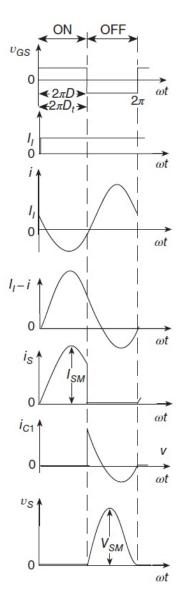

Figura 3.4: (a) Circuito equivalente clase E con  $V_I$  y  $L_F$  sustituidas por la fuente de corriente  $I_I$  y el circuito resonante en serie sustituido por la fuente de corriente alterna i. (b) Circuito equivalente con las dos fuentes de corriente  $I_I$  e i combinadas en una sola  $(I_I - i)$

La **Figura 3.4(b)** se corresponde con el gráfico número 4 de la **Figura 3.3**. Al hacer  $I_I - i$ , se obtiene una forma de onda igual a la que describe el gráfico 3 de la misma figura, pero desplazada (offset= 0) e invertida. Partiendo del circuito de la **Figura 3.4(b)**, se va a dar paso al análisis de las formas de onda  $I_I - i$ ,  $i_S$ ,  $I_{C1}$  y  $v_S$ . Para ello se presenta la **Figura 3.5** que agrupa los elementos necesarios.

Al comparar las formas de onda  $I_I - i$  con  $i_S$  de la **Figura 3.5**, se puede observar que son iguales durante parte del ciclo positivo, hasta que abruptamente, la corriente  $i_S$  se hace cero. La razón por la que pasa esto se muestra en la forma de onda de la tensión de entrada  $v_{GS}$  de la misma figura. Mientras  $v_{GS}$  se encuentra en un valor de tensión alto, entiéndase por alto cualquier valor de tensión lo suficientemente elevado para superar la tensión umbral  $(V_{TH})$  y llevarlo a plena conducción, el *switch* está cerrado (transistor conduciendo). Cuando esto pasa, la tensión entre los terminales del *switch* es  $v_S = 0$  y además, la capacidad de salida  $C_1$  es cortocircuitada a tierra, haciendo nula su corriente  $(i_{C1} = 0)$ . En cambio, cuando la tensión de entrada  $v_{GS}$  cambia a un valor bajo, el efecto

Figura 3.5: Circuito equivalente simplificado del amplificador y sus formas de onda

es distinto. En este segundo caso el comportamiento del transistor es entrar en estado de corte (switch abierto). Cuando esto sucede, la corriente no tiene un camino directo a tierra, por lo que circula hacia la capacidad  $C_1$ . Por esa razón la forma de onda de la corriente que circula por la capacidad ( $i_{C1}$ ) se corresponde con la sección en la que  $i_S = 0$  y combinadas las dos ( $i_S + i_{C1}$ ) dan lugar a la forma de onda de la corriente  $I_I - i$ . De aquí se deriva la forma de onda de la tensión en el switch ( $v_S$ ). Éste no más que el nivel de voltaje acumulado en la capacidad  $C_1$  durante los períodos en que, al mismo tiempo, el transistor está en estado de corte y la forma de onda de la corriente  $i_{C1}$  es positiva.

# 3.2.1. Suposiciones de simplificación

Para lograr un funcionamiento lo más eficiente posible, las redes del amplificador clase E se tienen que diseñar específicamente para cumplir ambas condiciones (**ZVS** y **ZVDS**). En [9] se asumen varias condiciones en los circuitos de operación con el objetivo de simplificar el análisis.

- El transistor y el diodo en antiparalelo conforman un *switch* ideal cuya resistencia  $r_{DS}=0$ .

- La tensión de saturación del transistor es **0 Volts** y en consecuencia, una  $R_{ON} = \infty$  y una conmutación instantánea.

- $\bullet$  La capacidad C se asume ideal.

- La bobina de *choque* se asume ideal, por lo que sólo deja pasar **DC**.

• El resto de elementos reactivos se suponen sin pérdidas. La carga  $R_L$  es el único elemento de la red que disipa potencia.

## 3.3. Análisis

Una vez explicado el comportamiento, el circuito, y las formas de onda de esta clase de amplificadores de potencia conmutados, se da paso al análisis matemático que fundamenta los conceptos teóricos previamente explicados. La ubicación de las variables que se exponen en las ecuaciones siguientes se pueden encontrar en el esquemático de la **Figura 3.1**

Han sido varias las veces en las que se ha hecho referencia a la forma de onda de la corriente AC (i) que circula a través de la carga colocada a la salida de la red del amplificador. Su forma de onda se rige por la expresión descrita por la ecuación

$$i = I_m \sin\left(\omega t + \phi\right) \tag{3.14}$$

donde  $I_m$  representa el valor de su amplitud,  $\omega = 2\pi f$  y  $\phi$  es la fase de la forma de onda. Por otro lado, idealmente se tiene que la impedancia óptima que la red de carga presenta al armónico fundamental y a los superiores viene dada por la ecuación (3.14) [10].

$$Z(\eta f_0) = \begin{cases} \frac{0.28}{\omega_S C} e^{j49.0524^{\circ}} &, n = 1\\ \infty &, n > 0 \end{cases}$$

(3.15)

La ecuación (3.15) representa la impedancia en la cual se tiene el valor máximo de eficiencia, que teóricamente es del 100 %. Partiendo de este punto, y habiendo cumplido las condiciones ZVS y ZVDS, se deduce que el ángulo óptimo de la corriente debe ser como muestra la ecuación (3.16)

$$\phi = \arctan(-\frac{\pi}{2}) = -32,482^{\circ} \tag{3.16}$$

y que las expresiones de sus formas de onda en función del intervalo de conducción  $0 \le \omega t < 2\pi$  son como las que se describen en las ecuaciones **3.17** y **3.18**.

$$\frac{v_S}{V_I} = \begin{cases} \pi \left( \omega t + \frac{3\pi}{2} - \frac{\pi}{2} \cos \omega t - \sin \omega t \right) &, \quad \pi \le \omega t < 2\pi \\ 0 &, \quad 0 \le \omega t < \pi \end{cases}$$

(3.17)

$$\frac{i_S}{I_I} = \begin{cases}

0, & \pi \le \omega t < 2\pi \\

i(\omega t) = \frac{\pi}{2} \sin \omega t - \cos \omega t + 1, & 0 \le \omega t < \pi

\end{cases}$$

(3.18)

Si se analizan con detenimiento las dos últimas ecuaciones, se puede notar que describen el comportamiento de las formas de onda descritas en las **Figuras 3.3** y **3.5**.

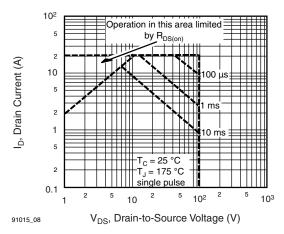

Para alguien que diseña amplificadores de potencia es muy importante el conocimiento de la máxima tensión de drenador que puede soportar el transistor que se desea utilizar como base para la construcción del circuito del amplificador. Los cálculos teóricos indican que generalmente, esta tensión en el punto de impedancia óptimo, que no es más que la "Z" de la ecuación (3.15), toma un valor de  $v_{DS_{MAX}}=3{,}56V_{DD}.$  Esto significa que el transistor que se va a utilizar para construir el amplificador debe tener una tensión de ruptura (break down en inglés) superior a  $3,56V_{DD}$ . Dicho valor de tensión, también implica una corriente de drenador máxima para dicho valor de impedancia. El valor máximo de amplitud de la corriente que circula por el switch bajo la condición que supone la impedancia de carga óptima, toma un valor de  $i_{DS_{MAX}}=2,86I_{DD}$ . Es importante mantener una visión clara de los valores que toman las formas de onda de la corriente y la tensión en el terminal de drenador del switch para cualquier valor de impedancia de carga que se vaya a utilizar. Si no se controlan estos parámetros, es posible colocar puntos que disparen los picos de corriente y tensión por encima de los máximos absolutos expresados en el datasheet, provocando que el transistor se deteriore o incluso se llegue a quemar.

Otro parámetro importante en cuanto al diseño de amplificadores de potencia se refiere, es su límite frecuencial. En otras palabras, la frecuencia máxima en la que se puede utilizar un modelo específico de transistor para diseñar un amplificador. El cálculo de este parámetro incluye varias características específicas propias de cada transistor como la tensión de ruptura  $(V_{break})$ , la capacidad de salida  $(C_{OUT})$ , o la corriente máxima que soporta el dispositivo  $(I_{MAX})$ . En la ecuación (3.19) que se

muestra a continuación, se muestra cómo calcular esta frecuencia:

$$f_{MAX} = 0.063 \frac{I_{MAX}}{C_{OUT} V_{break}} \tag{3.19}$$

Para el caso del transistor que se ha utilizado en este proyecto, es importante destacar que se ha trabajado muy cerca de su frecuencia máxima de operación. Sin embargo, en este caso, quien limita el comportamiento frecuencial de este transistor es el diodo en anti-paralelo intrínseco que posee entre los terminales drenador-fuente. Este diodo es un efecto que se produce en algunos transistores MOSFET por la forma de fabricarlos. Como todo diodo, este posee un cierto tiempo de recuperación que limita su propia utilización frecuencial hasta un cierto punto. De acuerdo con la hoja de características del IRF510 el tiempo de recuperación de su diodo intrínseco es de entre 100 ns y 200 ns. Estos tiempos limitan su funcionamiento a frecuencias f < 5 MHz en el peor de los casos, y como ya se ha mencionado anteriormente, en este proyecto se está trabajando a f = 2 MHz que está muy cerca de este límite.

Con todos los fundamentos teóricos ya explicados, se da paso al siguiente capítulo, el cual aportará todos los detalles y pasos seguidos en el proceso de diseño con el simulador.

CAPITULO

# Diseño del amplificador de potencia clase E en AWR Microwave Office

#### 4.1. Obtención de las curvas IV del transistor

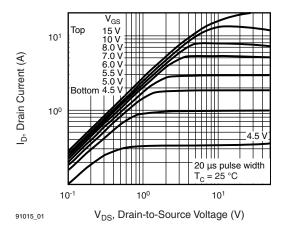

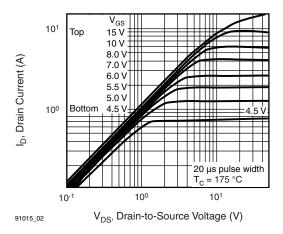

Lo primero a tener en cuenta a la hora de diseñar un amplificador de potencia (AP), es conocer cómo son las curvas I-V (corriente - tensión) del transistor. Con la ayuda de estas curvas, se determina el punto de trabajo óptimo del transistor en función de la aplicación para la que se pretenda utilizar.

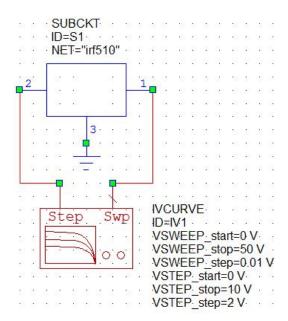

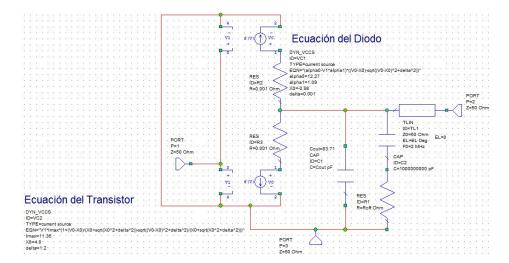

El procedimiento para encontrar el punto de trabajo se hace a partir de los modelos funcionales creados por los fabricantes. En la **Figura 4.1** se muestra el esquemático creado en el simulador donde se ha importado el modelo del **MOSFET IRF510** para obtener las curvas IV deseadas.

Figura 4.1: Esquemático para la obtención de las curvas IV

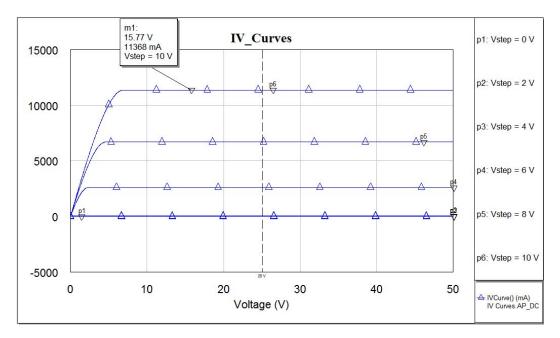

Una vez creado el esquemático, se representan las curvas obtenidas en una gráfica (Figura 4.2).

Figura 4.2: Representación gráfica de las curvas IV del modelo del fabricante

A partir de estas curvas, dado que el modelo que ofrece el fabricante conduce a problemas de convergencia al simular en condiciones de carga variable (load pull) así como por la conveniencia de poder identificar los mecanismos de pérdidas, se crea un modelo propio, que se puede ver en la **Figura 4.3**, de manera que sus curvas IV se

asemejen lo más posible a las obtenidas del modelo del fabricante.

Figura 4.3: Modelo simplificado, tipo conmutador, del transistor IRF510

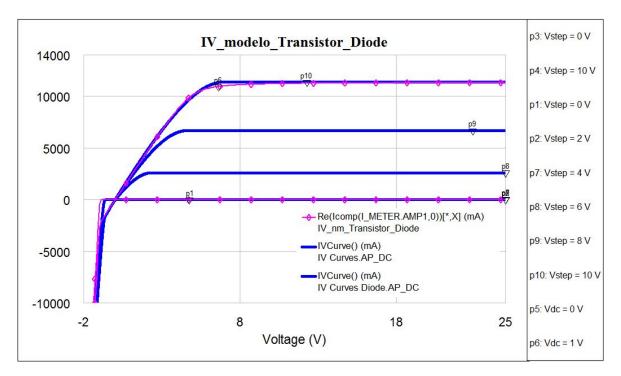

Con la herramienta de ajuste (tune) del simulador, se modifican los parámetros de las ecuaciones del diodo y del transistor que se observan en la **Figura 4.3**, hasta conseguir curvas IV lo más parecidas posibles a las del fabricante en el punto de trabajo escogido. A continuación se presenta la gráfica en la que se superponen tanto las curvas IV del modelo del **IRF510** proporcionado por el fabricante, como las obtenidas del nuevo modelo creado (**Figura 4.4**).

Figura 4.4: Curvas IV IRF510 vs Nuevo modelo

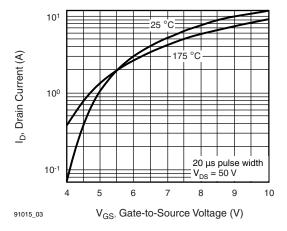

### 4.2. Obtención del punto de trabajo del transistor

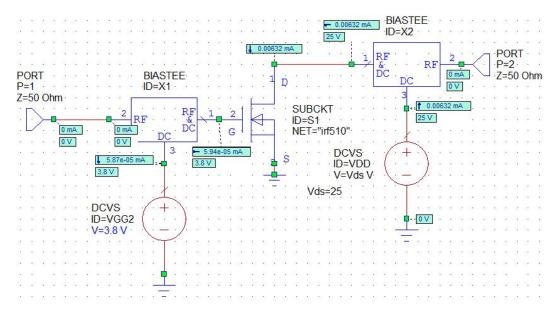

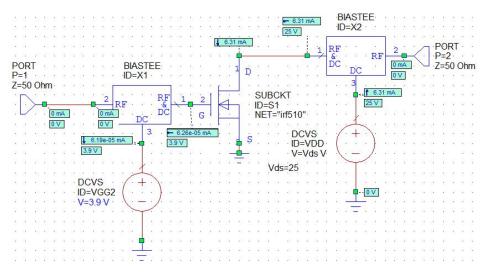

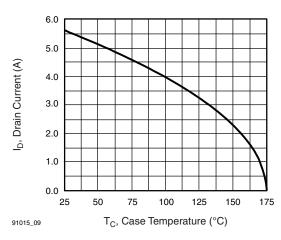

Se procede entonces a la búsqueda del punto de trabajo del transistor. Tras analizar la hoja de características del **IRF510** se decidió utilizar la tensión de polarización de drenador a  $V_{DS} = 25V$ . Posteriormente se crea un esquemático para comprobar el parámetro  $S_{22}$  (coeficiente de reflexión a la salida) mientras se va cambiando lentamente la tensión de puerta hasta encontrar la tensión que hace que el transistor entre en estado de conducción.

A continuación, en la **Figura 4.5**, se muestra el esquemático que se crea para esta simulación. Este esquemático presenta la peculiaridad que la frecuencia a la que se simula, no es estrictamente 2MHz, sino que se hace un pequeño barrido de frecuencia para comprobar que realmente el transistor no se encuentra en estado de conducción. Se ha utilizado el modelo del **IRF510** del fabricante y no nuestro modelo de transistor porque este se ha hecho lo más sencillo posible con el fin de realizar la simulación de load pull, por lo que, para este tipo de simulaciones no es lo suficientemente bueno.

La tensión de drenador que se ha utilizado es  $V_{DS} = 25V$ . Esta es la tensión que se utiliza en el datasheet del transistor para realizar todas las medidas. El otro punto importante a tener en cuenta es la tensión de la fuente de alimentación de puerta.

Figura 4.5: Modelo teórico del transistor IRF510

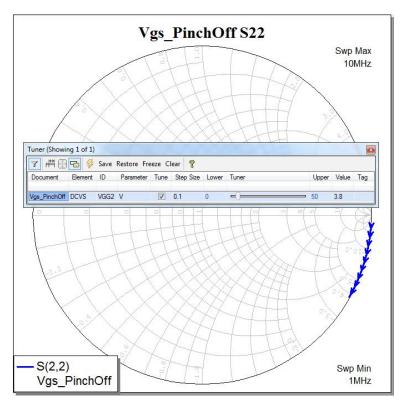

Para encontrar la tensión  $V_{GS}$  a la que el transistor comienza a conducir, se designa el valor de dicha tensión como un valor dinámico que se cambia manualmente al tiempo que se observa el  $S_{22}$  en el **Puerto 2** en la *Carta de Smith*. Ver en la **Figura 4.6**.

Figura 4.6: Representación gráfica del  $\mathcal{S}_{22}$  del transistor

Las modificaciones de la tensión  $V_{GS}$  se hacen con un paso muy pequeño, concretamente 0,1V. Al mismo tiempo se monitoriza el coeficiente  $S_{22}$  en la **Figura 4.6** hasta observar que este pasa de estar en el borde de la Carta de Smith (estado de alta impedancia o circuito abierto) a estar más adentro. Cuando esto sucede, significa que se ha alcanzao la mínima tensión necesaria para formar el canal por el que circulan los electrones en el transistor. Esta tensión, de tratarse de un transistor idealizado con un perfil Ids(Vgs) lineal a tramos, sería la tensión umbral o **threshold**. Sin embargo, en un transistor real con una entrada en conducción paulatina, la tensión umbral es algo superior, el valor en que se produce la mayor variación de la transconductancia con la tensión aplicada en puerta.

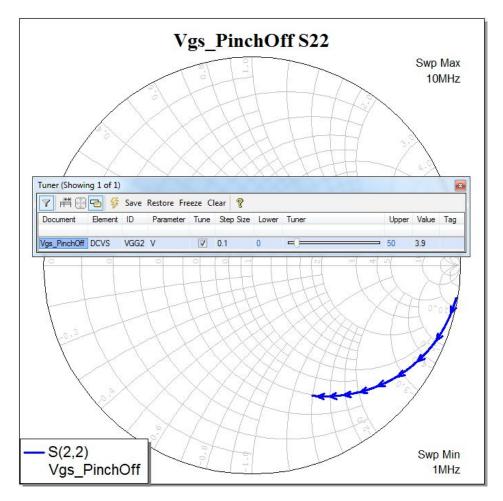

En las dos últimas figuras mostradas anteriormente se muestra un estado en el que el transistor se encuentra en estado de corte a una tensión de puerta  $V_{GS} = 3.8V$  como indica la ventana Tuner superpuesta en la gráfica de la **Figura 4.6** y el valor de la fuente de tensión colocada en el terminal de puerta del transistor en la **Figura 4.5**. Se ha decidido mostrar dicho estado a modo de comparación con lo que sucede a una tensión  $V_{GS} = 3.9V$  (**Figura 4.7** y **Figura 4.8**).

Figura 4.7: Modelo teórico del transistor IRF510

Tal y como se puede ver en la Figura 4.7, el circuito no ha cambiado en nada salvo por el valor de tensión que presenta la fuente  $V_{GG2}$ . En el caso de la **Figura 4.5** este valor era de 3,8V. Este pequeño incremento en el valor de la tensión  $V_{GS}$  provoca el cambio del coeficiente  $S_{22}$  que se puede observar en la **Figura 4.8**.

Figura 4.8: Representación gráfica del  $S_{22}$  del transistor

Una vez encontrado el valor más alto de tensión al cual el transistor no conduce, se vuelve a dejar el esquemático con el valor de tensión inmediatamente inferior a esta, es decir, se vuelve a fijar  $V_{GS}=3.8V$  y se da por finalizado este procedimiento.

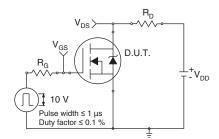

## 4.3. Obtención de la potencia de saturación del transistor

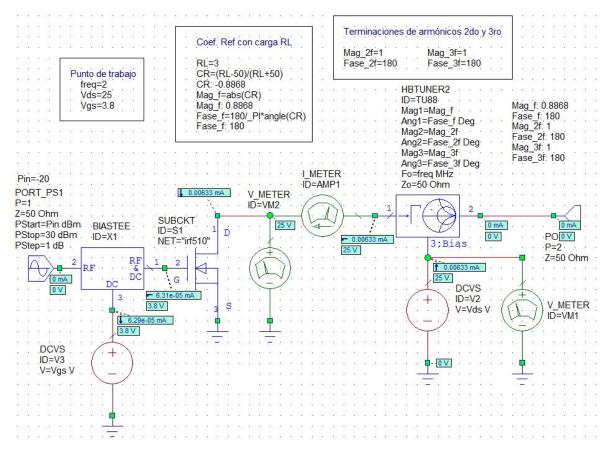

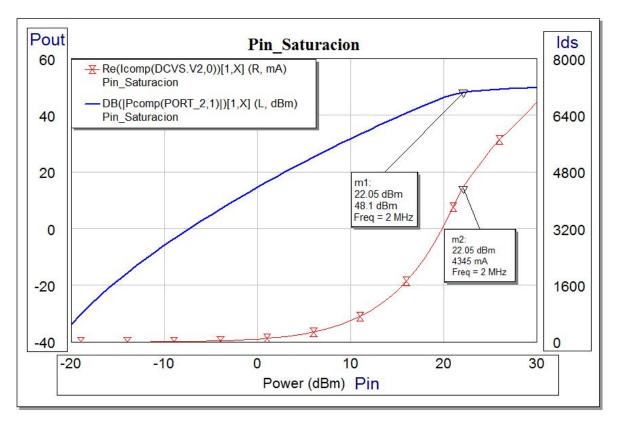

En este apartado se comenta cómo se realiza la simulación para encontrar la potencia de saturación del transistor. El objetivo de esta simulación es encontrar cuál es la potencia de entrada  $(P_{in})$  que hace que el transistor se sature de forma profunda y con ello aproxime su operación a la de un conmutador. Conociendo este dato, se puede estudiar su funcionamiento como amplificador manteniendo potencias iguales o inferiores a esta, pues, no tendría sentido utilizar más potencia de entrada, si la potencia de salida  $(P_{out})$  no va a cambiar por haber llegado a su máximo posible.

Para el esquemático de esta simulación se necesita polarizar el transistor en el punto de trabajo determinado en el apartado anterior, es decir, fijar  $V_{GS} = 3.8V$  y  $V_{DS} = 25V$  para luego añadir un generador de señal con un barrido de potencia en la puerta del transistor (**Figura 4.9**).

Figura 4.9: Representación gráfica del  $S_{22}$  del transistor

Para el barrido de la potencia se comienza desde un valor  $P_{in} = -20 \ dBm$  hasta un valor  $P_{in} = 30 \ dBm$ . La respuesta del transistor ante esta simulación se presenta en la **Figura 4.10**

Analizando la Figura 4.10 cabe destacar que cuando  $P_{in}=22.05\ dBm$ , la potencia de salida apenas cambia tras alcanzar el valor  $P_{out}=48.1\ dBm$ . Conocida esta potencia se procede con la realización de la simulación de load pull utilizando como potencia de entrada los  $22\ dBm$  obtenidos de este apartado.

Figura 4.10: Gráfico  $P_{out}$  vs  $P_{in}$  e  $I_{DS}$  vs  $P_{in}$

### 4.4. Realización de la simulación de load pull

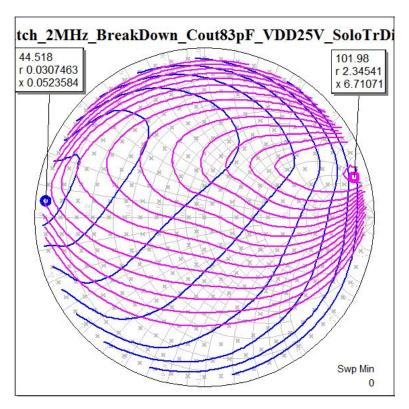

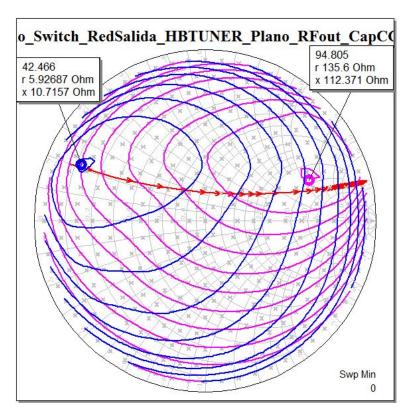

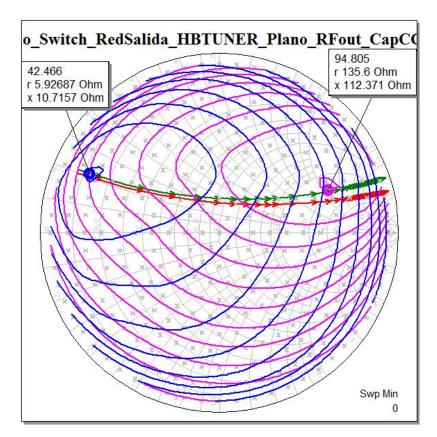

Esta simulación es de vital importancia en el diseño de este tipo de amplificadores. Lo que se busca con esta simulación es encontrar las regiones de la Carta de Smith que presentan círculos tanto de potencia de salida como de eficiencia constantes, además de los puntos de impedancia a los cuales se obtiene la máxima potencia de salida y la máxima eficiencia.

#### 4.4.1. Simulación load pull con componentes ideales

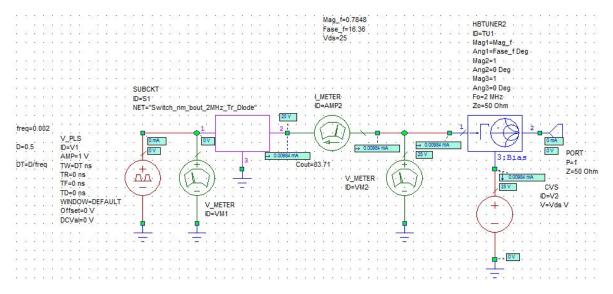

Para realizar esta simulación se necesita crear un nuevo esquemático en el que se incluyan los siguientes componentes:

- 1. Nuestro modelo del IRF510.

- 2. Un generador de señal pulsada.

- 3. El componente **HBTUNER2** del simulador

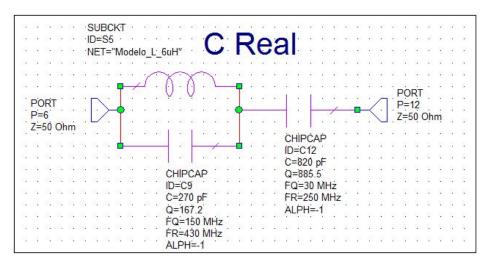

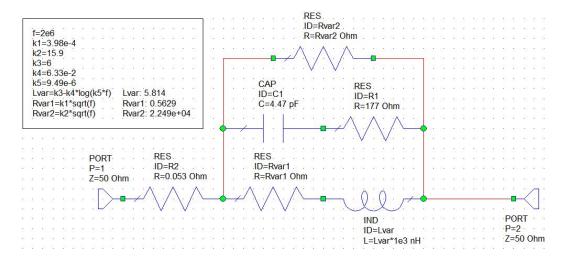

El esquemático creado para esta simulación que se muestra en la **Figura 4.11** realiza un barrido tanto de la magnitud como de la fase al armónico fundamental. Esto es

Figura 4.11: Esquemático para simulación de load pull