# UNIVERSIDAD DE CANTABRIA

Departamento de Ingeniería Informática y Electrónica

Programa de Doctorado en Ciencia y Tecnología

Tesis Doctoral

# Soporte para co-ejecución eficiente en sistemas heterogéneos

PhD Thesis

# Efficient co-execution support in heterogeneous systems

Borja Pérez Pavón

## Dirigida por Jose Luis Bosque Orero

Escuela de Doctorado de la Universidad de Cantabria

Santander 2019

### Agradecimientos

Este documento representa el trabajo de 5 años, fruto del esfuerzo y apoyo de muchas más personas de las que podrían aparecer en la portada. Las siguientes líneas son para reconocer su importancia en esta tesis.

- A Jose Luis, mi director de tesis. Gracias por tus esfuerzos, por haber confiado en mi y por haberme infundido el gusto por la investigación e, incluso, por la docencia.

- A todos los miembros del grupo de investigación de Arquitectura y Tecnología de Computadores. Vuestro trabajo diario hace posible que sigamos investigando. Especialmente a Esteban, por estar siempre dispuesto a echarme una mano, y a Mon, por su apoyo y sus lecciones que van más allá de lo académico.

- A mis padres, abuelas y abuelos. Este camino empezó hace mucho tiempo y vuestra ilusión, cariño y apoyo constantes son los que han permitido que llegue a la meta.

- A mis amigos de siempre. Porque, pese a que nuestras vidas nos alejen, el tiempo no pasa, y se que siempre estaréis ahí.

- A mis amigos nuevos, en sus encarnaciones musicales y carpinteras. Porque el verdadero cariño se expresa en la descalificación continua. Si esta tesis es prácticamente un tema de hip-hop es por vosotros.

- A ti, porque aunque algunas cosas cambien, las más importantes siguen igual.

#### Abstract

Heterogeneous architectures have become prevalent due to their outstanding performance and energy efficiency. However, programming these systems is far from trivial. Current heterogeneous programming models impose a host-device approach and favour task-parallelism. Applications developed following these kind of models are executed in the CPU and only certain compute intensive parts are explicitly offloaded to accelerators. On the contrary, co-execution, the cooperative operation of all the available devices computing for a single workload in a data-parallel manner, is overlooked. If desired, the programmer will be in charge of manually managing the devices, the data distribution and the division of the workload, effectively expressing co-execution in terms of task-parallelism and representing a significant amount of work.

For co-execution to be useful it has to be effortless. This means that using every device in the computation of a single kernel should represent the same work as using a single device. To achieve this, the programmer needs to be abstracted from the underlying hardware and spared load balancing decisions. The former enables a transparent use of the whole system that eases programming and guarantees portability, as the programmer no longer has to worry about the devices. The latter aids the programmer to obtain good performance from co-execution, as these decisions are complex, depending on both the irregularity of the co-executed workload and the heterogeneity of the system itself.

This dissertation makes several contributions towards effortless co-execution in heterogeneous systems, tackling abstraction and load balancing from both the software and hardware angles. HGuided and Sigmoid, two novel load balancing algorithms specially designed for co-execution, are proposed and evaluated, achieving outstanding performance. Maat, a new OpenCL-based load balancing library has been designed and implemented. It enables the abstract management of the whole system by providing the illusion of a single device representing all the available resources. Taking abstraction even further, co-execution and load balancing have also been implemented in OmpSs, as an evaluation of the interest of co-execution in task-based programming models. Lastly, a design for a dispatcher that enables hardware supported co-execution in integrated heterogeneous systems is presented and evaluated. These contributions ease the programming of heterogeneous systems and represent a significant improvement on both performance and energy efficiency.

#### Resumen

Gracias a su rendimiento y eficiencia energética, las arquitecturas heterogéneas se han convertido en un elemento común en cualquier sistema de cómputo. Desde el supercomputador hasta los dispositivos móviles, todos los sistemas actuales integran CPUs tradicionales y aceleradores especializados en ciertas cargas de trabajo. La aparición de este tipo de arquitecturas también supuso el desarrollo de nuevos modelos de programación que permitieran aprovechar sus capacidades. Estos modelos parten de que una aplicación heterogénea se ejecutará principalmente en la CPU, mientras que ciertas funciones especialmente intensivas en cómputo y masivamente paralelas en datos, serán descargadas en los aceleradores. Esta descarga debe ser realizada explícitamente por el programador, el cual es responsable de gestionar manualmente cada uno de los dispositivos disponibles, las tareas que ejecutarán y los datos que utilizarán. A esta forma de operar se le suele llamar modelo *host-device* y favorece el paralelismo de tareas, pero también desaprovecha la capacidad de cómputo y la energía de la CPU cuando se ejecuta sólo en la GPU. Sin embargo, otra forma de paralelismo también es posible: la co-ejecución.

La co-ejecución se define como la cooperación de todos los dispositivos disponibles en el sistema, ejecutando la carga de trabajo asociada a una sola tarea y aprovechando el paralelismo de datos. Esto quiere decir que todos los dispositivos ejecutarán el mismo código, pero producirán porciones de los resultados disjuntas. Esta aproximación al paralelismo, además, se ajusta a las características de las aplicaciones que habitualmente se descargan en aceleradores, pues estos basan sus capacidades en el paralelismo de datos. Sin embargo, los modelos de programación actuales no tienen ningún soporte para co-ejecución. Si se desea que los dispositivos cooperen en la ejecución de una única tarea, el programador tendrá que repartirla manualmente entre los dispositivos, gestionándolos individualmente y transfiriendo los datos que necesiten. En definitiva, los modelos de programación obligan a expresar la co-ejecución utilizando paralelismo de tareas.

Para que la co-ejecución sea una opción verdaderamente útil, los modelos de programación tienen que ofrecer las capacidades necesarias para que los dispositivos cooperen sin precisar trabajo adicional por parte del programador. Una co-ejecución que no requiera esfuerzos se construye sobre dos pilares: la abstracción y el equilibrio de carga.

La abstracción se refiere a la interacción del programador con el sistema, que debe realizarse a

través de interfaces de alto nivel, que eviten que el programador tenga que preocuparse de la gestión individual de los dispositivos. Esto no sólo facilita la co-ejecución, sino que garantiza la portabilidad de las aplicaciones, pues al abstraer la programación de los dispositivos subyacentes, un código desarrollado en un sistema usará todos los dispositivos disponibles en cualquier otro.

El equilibrio de carga está relacionado con la división de la carga de trabajo entre los dispositivos disponibles, con lo cual es fundamental para obtener un buen rendimiento. En general, las decisiones de equilibrio de carga son complejas, pues dependen tanto del comportamiento de la carga a distribuir como de los propios dispositivos. La carga de trabajo puede tener un comportamiento variable o irregular a lo largo de su ejecución, con tiempos de ejecución diferentes para porciones de trabajo con el mismo tamaño a priori. Este tipo de cargas requieren que los algoritmos puedan adaptarse para obtener buenos rendimientos. Sin embargo, esta capacidad de adaptación no representa más que una sobrecarga para las cargas regulares que no la requieren. Por otro lado, los sistemas heterogéneos incluyen dispositivos con arquitecturas y capacidades de cómputo muy diferentes. Por tanto, el balanceo de carga tendrá que tener en cuenta las características del dispositivo que recibirá cada porción de trabajo. En definitiva, este tipo de decisiones deben facilitarse al programador lo más posible. Idealmente, la co-ejecución debe ir acompañada de algoritmos de balanceo de carga que obtengan buen rendimiento sin requerir ninguna información al programador. Estos son los algoritmos no informados, en contraposición con los que sí que la requieren, llamados informados.

Esta tesis presenta una serie de contribuciones que posibilitan la co-ejecución eficiente y sin esfuerzo en sistemas heterogéneos, abordando la abstracción y el equilibrio de carga, tanto desde un punto de vista software como hardware. En otras palabras, el objetivo de la tesis es ofrecer los medios necesarios para que ejecutar una tarea colaborativamente, aprovechando todos los dispositivos del sistema, represente el mismo trabajo para el programador que utilizar uno sólo de los dispositivos. Para desarrollar esta investigación, se ha recurrido tanto a ejecuciones reales, como a simulaciones utilizando gem5, la herramienta de simulación estándar de facto en la investigación en arquitectura de computadores. Para realizar las evaluaciones, se han utilizado los sistemas de cómputo del grupo de investigación de Arquitectura y Tecnología de Computadores (ATC) de la Universidad de Cantabria, así como una máquina del grupo TRASGO de la Universidad de Valladolid para realizar pruebas de escalabilidad.

En primer lugar, se proponen HGuided y Sigmoid, dos nuevos algoritmos de balanceo de carga especialmente diseñados para co-ejecución en sistemas heterogéneos. HGuided es un algoritmo dinámico que utiliza tamaños de paquete decrecientes, de modo que se reducen las sobrecargas sin perder capacidad de adaptación cerca del final de la ejecución, que es cuando realmente es necesaria. Este algoritmo también considera la velocidad de cómputo de cada dispositivo, de modo que no se asignen paquetes demasiado grandes a dispositivos lentos que generen desequilibrios. De esta manera, HGuided consigue equilibrar satisfactoriamente la carga tanto de aplicaciones regulares como irregulares, obteniendo un rendimiento y eficiencia energética excelentes. Sin embargo, este algoritmo es informado, pues recibe la velocidad de cómputo y el tamaño mínimo hasta el que menguarán los paquetes como parámetros. Esto requiere un esfuerzo al programador, pues los valores óptimos para los parámetros varían entre sistemas y aplicaciones. Por el contrario, Sigmoid es un algoritmo no informado, capaz de monitorizar la co-ejecución y de adaptar sus parámetros internos al comportamiento de las cargas de trabajo. Internamente, utiliza una función derivada de la sigmoide para controlar el tamaño de los paquetes que genera, de modo que tengan tamaños menores si se necesita mayor adaptabilidad. El resultado es un rendimiento y una eficiencia excelentes, sin requerir ningún esfuerzo por parte del programador.

Respecto a la abstracción, esta tesis presenta Maat, una librería de co-ejecución en sistemas heterogéneos basada en OpenCL. Maat simplifica la co-ejecución significativamente, creando la ilusión de que el sistema dispone de un único dispositivo que representa la capacidad de cómputo agregada de todos los recursos disponibles. Esta ilusión se construye a través de abstracciones implementadas respetando la filosofía de programación de OpenCL. De esta manera, se facilita la adaptación de aplicaciones pre-existentes para que aprovechen la co-ejecución. Maat también mejora la portabilidad de las aplicaciones, pues una gestión abstracta de los dispositivos permite que una aplicación programada para un sistema funcione en cualquier otro sin necesidad de modificaciones. Los resultados experimentales demuestran que Maat obtiene rendimientos cercanos a los ideales y ahorros energéticos importantes para las aplicaciones evaluadas, siendo Sigmoid el algoritmo de equilibrio de carga que mejores resultados obtiene, seguido de cerca por HGuided.

Para llevar la abstracción un paso más allá, esta tesis también propone la extensión de modelos de programación basados en tareas para soportar co-ejecución. Este tipo de modelos facilitan el

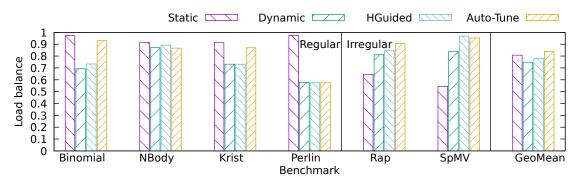

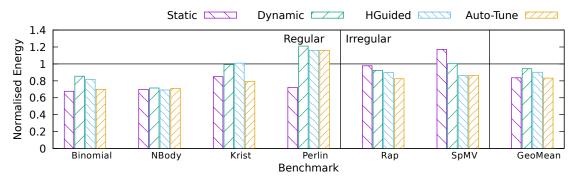

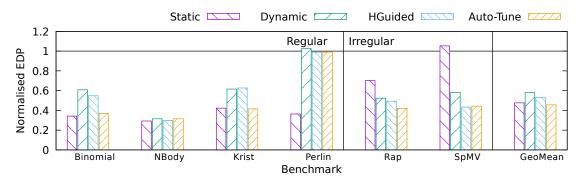

desarrollo de aplicaciones ofreciendo abstracciones de alto nivel que ocultan detalles complejos de la programación paralela. Sin embargo, tienen carencias importantes en lo que se refiere a co-ejecución. Como ejemplo para evaluar su utilidad, se ha añadido un nuevo módulo a OmpSs, pero las conclusiones extraídas pueden hacerse extensibles a otros lenguajes. Este nuevo módulo hace posible la co-ejecución de una sola tarea utilizando todos los recursos disponibles en el sistema sin requerir ningún esfuerzo del programador. Además, esta extensión apenas tiene impacto en la infraestructura original de OmpSs o en la forma de programar aplicaciones utilizándolo. De forma similar, los algoritmos implementados en el módulo respetan las ideas sobre equilibrio de carga propuestas por OpenMP, que es la base de OmpSs. Se proponen cuatro algoritmos. El algoritmo estático genera un único paquete por dispositivo, con un tamaño proporcional a la velocidad de cómputo de este en relación con la de todo el sistema. El algoritmo dinámico, por el contrario, divide la carga en gran cantidad de paquetes pequeños que se planifican en tiempo de ejecución. HGuided funciona de manera similar, pero utiliza tamaños de paquete decrecientes. Por último, Auto-Tune, es una evolución de HGuided capaz de monitorizar la co-ejecución, de modo que elimina la necesidad de parámetros, siendo un algoritmo no informado. Los resultados corroboran que la co-ejecución es beneficiosa para los modelos de programación basados en tareas, pues facilita el aprovechamiento de todos los recursos disponibles en el sistema. El algoritmo Auto-Tune consigue el mejor rendimiento medio, ya que es capaz de adaptarse a las aplicaciones irregulares y de conseguir un rendimiento casi igual al de Static en las regulares.

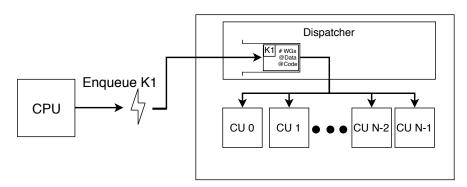

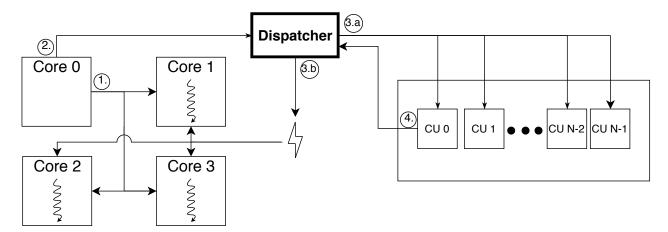

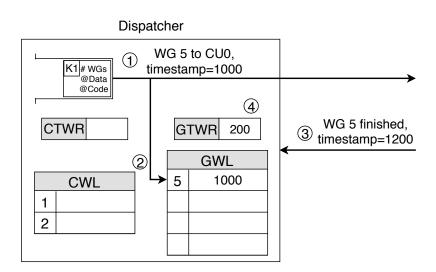

Esta tesis también presenta y evalúa un nuevo dispatcher para dar soporte hardware a la coejecución en sistemas heterogéneos integrados. Este tipo de arquitecturas aúnan en un solo SoC cores CPU y unidades de cómputo GPU, por lo que reducen las latencias y sobrecargas relativas a la interacción entre los dispositivos. Sin embargo, a pesar de la integración, la CPU y la GPU siguen tratándose como dispositivos individuales. Estos sistemas permitirían considerar diseños en los que el programador simplemente lanzara una tarea y fuera el hardware el que se encargara de distribuirla entre los dispositivos de forma eficiente. Así es como opera el nuevo dispatcher: reparte de forma autónoma work-groups OpenCL entre cores de la CPU y compute units de la GPU indistintamente. Además, el dispatcher monitoriza el tiempo que tardan en ejecutarse los work-groups en cada dispositivo. De esta manera, es capaz de desactivar temporalmente la co-ejecución si predice que la asignación de un work-group a un dispositivo supondrá un retraso. Esta propuesta ha sido evaluada utilizando el simulador gem5. Los resultados muestran que el nuevo dispatcher permite obtener mejoras de rendimiento importantes. Sin embargo, también genera nuevos retos que pueden limitar la ganancia de rendimiento en ciertos casos, como contención en el acceso a memoria.

Finalmente, una tesis no sólo representa una respuesta a una pregunta, sino también el comienzo de nuevas líneas de investigación que se construyen sobre el trabajo realizado a lo largo del doctorado. En primer lugar, los algoritmos de equilibrio de carga constituyen un área de investigación de gran interés. Los aquí propuestos se centran en el rendimiento. Sin embargo, aunque el rendimiento y el consumo energético estén muy relacionados, algunos resultados de esta tesis muestran que una distribución de carga que maximiza el rendimiento no necesariamente minimiza el consumo. Por este motivo, podría pensarse en algoritmos que tuvieran por objetivo minimizar la energía. Por otro lado, los algoritmos propuestos son agnósticos: operan de forma idéntica para todas las cargas de trabajo. Sería interesante investigar algoritmos que fueran capaces de analizar el código de la carga a co-ejecutar, de modo que pudieran tomar decisiones de equilibrio de carga más informadas. Podrían incluso decidir enviar toda la carga a un único dispositivo, liberando al programador de la decisión de cuándo co-ejecutar. Finalmente, desde el hardware, podría investigarse en técnicas para reducir la contención en el acceso a memoria producida por la co-ejecución, o en diseños de dispatchers más inteligentes, capaces de identificar patrones de cómputo irregulares.

# Contents

| Agradecimientos                        | Ι   |

|----------------------------------------|-----|

| Abstract                               | III |

| Resumen                                | v   |

| 1. Introduction                        | 1   |

| 1.1. Programming heterogeneous systems | 2   |

| 1.2. Co-execution                      | 2   |

| 1.2.1. Abstraction                     | 3   |

| 1.2.2. Load balancing                  | 4   |

| 1.3. Hypothesis                        | 5   |

| 1.4. Major Dissertation Contributions  | 5   |

| 1.5. Methodology                       | 6   |

| 1.5.1. Test platforms                  | 7   |

| 1.5.2. Evaluated metrics               | 7   |

| 1.5.3. Energy measurements             | 9   |

|    | 1.6. | Document Structure                                           | 10 |

|----|------|--------------------------------------------------------------|----|

| 2. | Bac  | kground and Related Work                                     | 13 |

|    | 2.1. | Programming models                                           | 13 |

|    |      | 2.1.1. Heterogeneous programming in OpenCL                   | 14 |

|    |      | 2.1.2. Task-based programming languages                      | 19 |

|    | 2.2. | Heterogeneous system simulation in gem5                      | 20 |

|    |      | 2.2.1. The GPU model                                         | 21 |

|    |      | 2.2.2. OpenCL support                                        | 22 |

|    | 2.3. | Related Work                                                 | 23 |

|    |      | 2.3.1. System abstraction                                    | 23 |

|    |      | 2.3.2. Load balancing                                        | 24 |

|    |      | 2.3.3. Integrated heterogeneous systems and hardware support | 25 |

| 3. | Loa  | d balancing algorithms for co-execution                      | 27 |

|    | 3.1. | Requirements for heterogeneous co-execution                  | 28 |

|    | 3.2. | Problem Definition                                           | 29 |

|    | 3.3. | The HGuided Algorithm                                        | 30 |

|    |      | 3.3.1. Overview                                              | 30 |

|    |      | 3.3.2. Limitations                                           | 33 |

|    | 3.4. | The Sigmoid Algorithm                                        | 34 |

|    |      | 3.4.1. Overview                                              | 35 |

|    |      | 3.4.2. | The logistic function and the load balancing problem $\ldots \ldots \ldots \ldots$ | 37 |

|----|------|--------|------------------------------------------------------------------------------------|----|

|    |      | 3.4.3. | Automatic parameter tuning                                                         | 39 |

| 4. | Co-I | Execut | tion & system abstraction                                                          | 45 |

|    | 4.1. | Motiva | ation                                                                              | 46 |

|    | 4.2. | Overv  | iew of Maat                                                                        | 47 |

|    | 4.3. | Desigr | n of Maat                                                                          | 48 |

|    |      | 4.3.1. | Device Abstraction                                                                 | 49 |

|    |      | 4.3.2. | Execution Abstraction                                                              | 50 |

|    |      | 4.3.3. | Memory Abstraction                                                                 | 52 |

|    |      | 4.3.4. | Summary                                                                            | 53 |

|    | 4.4. | Impler | mentation                                                                          | 54 |

|    |      | 4.4.1. | Data structure management                                                          | 55 |

|    |      | 4.4.2. | Runtime capabilities                                                               | 56 |

|    | 4.5. | Metho  | dology                                                                             | 61 |

|    |      | 4.5.1. | Reference algorithms                                                               | 61 |

|    |      | 4.5.2. | Applications                                                                       | 63 |

|    | 4.6. | Evalua | ation                                                                              | 64 |

|    |      | 4.6.1. | Load Balance                                                                       | 64 |

|    |      | 4.6.2. | Performance                                                                        | 65 |

|    |      | 4.6.3. | Energy consumption                                                                 | 67 |

|    |      | 4.6.4. | Scalability                                                                        | 69 |

|    | 4.7. | Conclusions                                           | 71  |

|----|------|-------------------------------------------------------|-----|

| 5. | Co-  | execution support in task-based programming models    | 73  |

|    | 5.1. | Motivation                                            | 74  |

|    | 5.2. | Kernel co-execution in OmpSs                          | 76  |

|    | 5.3. | Load Balancing Algorithms                             | 77  |

|    |      | 5.3.1. The Static algorithm                           | 77  |

|    |      | 5.3.2. The Dynamic algorithm                          | 79  |

|    |      | 5.3.3. The HGuided algorithm                          | 80  |

|    |      | 5.3.4. The Auto-Tune algorithm                        | 81  |

|    | 5.4. | Design                                                | 84  |

|    | 5.5. | Implementation                                        | 86  |

|    | 5.6. | Methodology                                           | 88  |

|    | 5.7. | Evaluation                                            | 90  |

|    |      | 5.7.1. Parameter sensitivity                          | 90  |

|    |      | 5.7.2. Experimental results                           | 92  |

|    | 5.8. | Conclusions                                           | 97  |

| 6. | Har  | dware supported co-execution in heterogeneous systems | 99  |

|    | 6.1. | Motivation                                            | 100 |

|    | 6.2. | Design                                                | 102 |

|    |      | 6.2.1. Programming support                            | 102 |

|     |       | 6.2.2. | Architecture and OS support                                                                    | . 103 |

|-----|-------|--------|------------------------------------------------------------------------------------------------|-------|

|     |       | 6.2.3. | Proposed dispatcher design                                                                     | . 104 |

|     |       | 6.2.4. | Automatic co-execution throttling                                                              | . 106 |

|     | 6.3.  | Impler | nentation                                                                                      | . 109 |

|     |       | 6.3.1. | OpenCL library                                                                                 | . 110 |

|     |       | 6.3.2. | OpenCL workloads on CPU cores                                                                  | . 111 |

|     |       | 6.3.3. | Architecture                                                                                   | . 112 |

|     | 6.4.  | Metho  | dology                                                                                         | . 115 |

|     |       | 6.4.1. | Modelled architecture                                                                          | . 115 |

|     |       | 6.4.2. | Selected applications                                                                          | . 116 |

|     |       | 6.4.3. | Evaluated metrics                                                                              | . 116 |

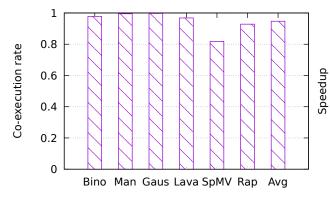

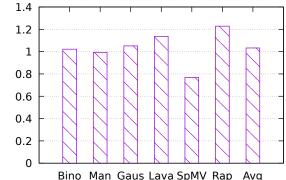

|     | 6.5.  | Evalua | tion $\ldots$ | . 117 |

|     | 6.6.  | Conclu | nsions                                                                                         | . 121 |

| 7.  | Con   | clusio | ns and Future Work                                                                             | 123   |

|     | 7.1.  | Conclu | isions                                                                                         | . 123 |

|     | 7.2.  | Future | Work                                                                                           | . 125 |

| Lis | st of | public | ations                                                                                         | 129   |

| Bil | bliog | raphy  |                                                                                                | 131   |

# List of Tables

| 4.1. | Maat and OpenCL functions                                                   | 54  |

|------|-----------------------------------------------------------------------------|-----|

| 4.2. | Parameters for each benchmark                                               | 63  |

| 4.3. | Maximum speedup for the different benchmarks                                | 65  |

| 4.4. | Number of Packages generated by each load balancing algorithm and benchmark | 67  |

| 5.1. | Parameters for each application                                             | 89  |

| 5.2. | Maximum achievable speedup per application.                                 | 90  |

| 6.1. | Parameters for each benchmark                                               | 116 |

# List of Figures

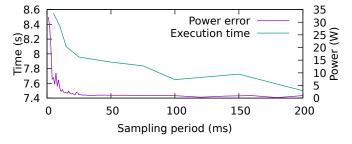

| 1.1. | Impact of sampling period on power measurement and kernel execution time                                                                 | 10 |

|------|------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1. | The Host-Device programming model.                                                                                                       | 15 |

| 2.2. | Platform and context possibilities for two sample systems                                                                                | 16 |

| 2.3. | OpenCL memory model                                                                                                                      | 18 |

| 2.4. | Headers for the tasks                                                                                                                    | 20 |

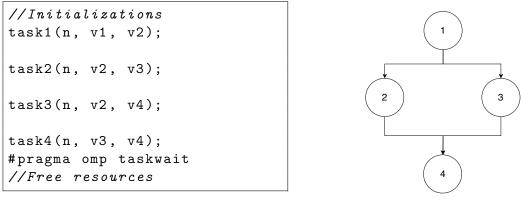

| 2.5. | Code for the launch of the tasks and generated OmpSs dependence graph                                                                    | 21 |

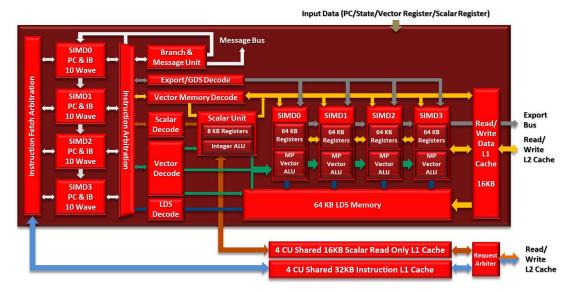

| 2.6. | Representation of the GCN compute unit. Taken from: White Paper. AMD<br>GRAPHICS CORES NEXT (GCN) ARCHITECTURE [AMD12]. Copyright<br>AMD | 22 |

| 3.1. | Computing speed comparison for Binomial                                                                                                  | 33 |

| 3.2. | Package size comparison for Binomial.                                                                                                    | 34 |

| 3.3. | Package size comparison for BM3D                                                                                                         | 34 |

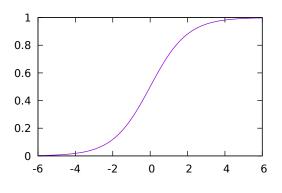

| 3.4. | Representation of the logistic function for $L = 1$ , $k = 1$ and $x_0 = 0$                                                              | 38 |

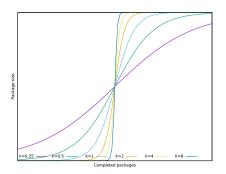

| 3.5. | Evolution of the package size for different $k$ values                                                                                   | 38 |

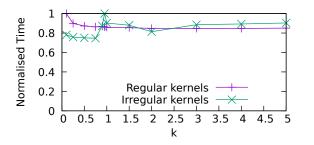

| 3.6. | Influence of $k$ on regular and irregular kernels                                                                                        | 42 |

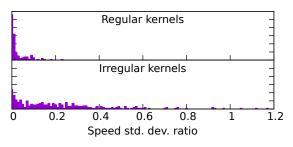

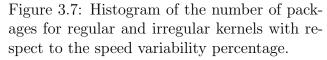

| 3.7.  | Histogram of the number of packages for regular and irregular kernels with re-                                             |    |

|-------|----------------------------------------------------------------------------------------------------------------------------|----|

|       | spect to the speed variability percentage                                                                                  | 42 |

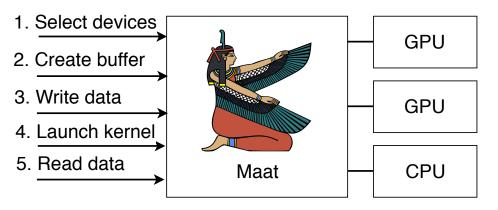

| 4.1.  | High level description of the operation of Maat.                                                                           | 48 |

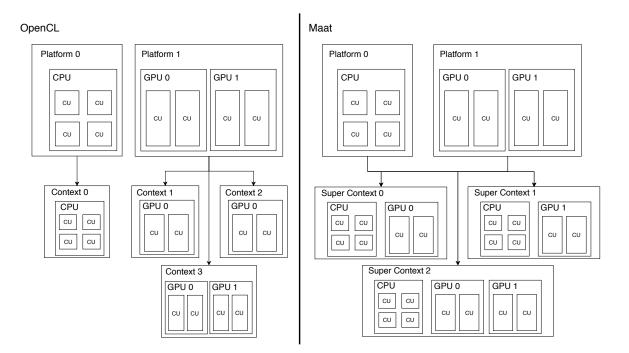

| 4.2.  | Possible contexts and SuperContexts in a sample system. Redundant SuperContexts omitted.                                   | 51 |

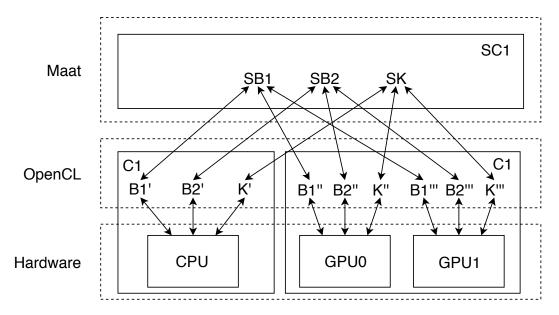

| 4.3.  | Underlying OpenCL data structures transparently managed by Maat in a sample system                                         | 55 |

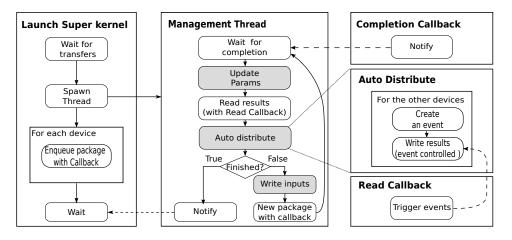

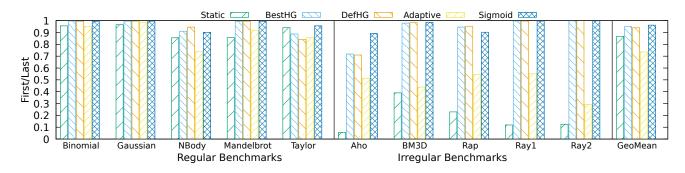

| 4.4.  | High level representation of the operation of Maat. Grey boxes represent optional operations.                              | 58 |

| 4.5.  | Representation of the dual queue operation of Maat.                                                                        | 59 |

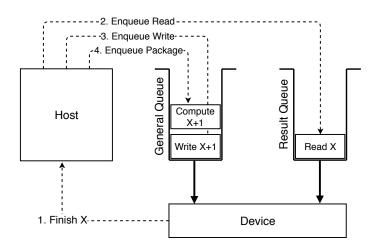

| 4.6.  | Representation of the partial results produced by two devices at the completion of a kernel                                | 60 |

| 4.7.  | Load balance of each device for all algorithms and benchmarks in the heterogeneous system.                                 | 65 |

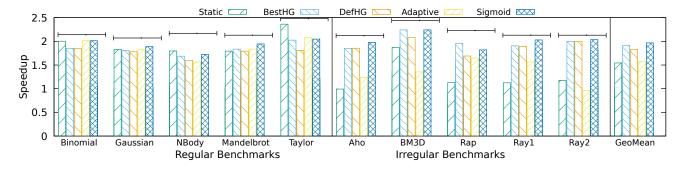

| 4.8.  | Speedups of the benchmarks with the different algorithms in the heterogeneous system.                                      | 66 |

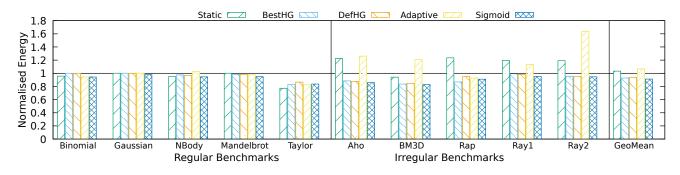

| 4.9.  | Energy consumption of the benchmarks with the different algorithms normalized to the baseline in the heterogeneous system. | 68 |

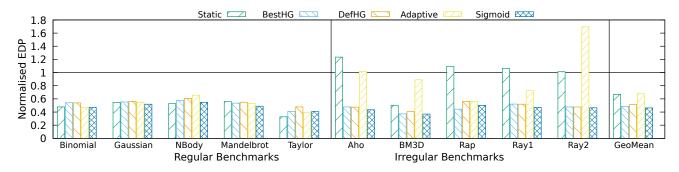

| 4.10. | EDP of the benchmarks with the different algorithms normalized to the baseline<br>in the heterogeneous system              | 68 |

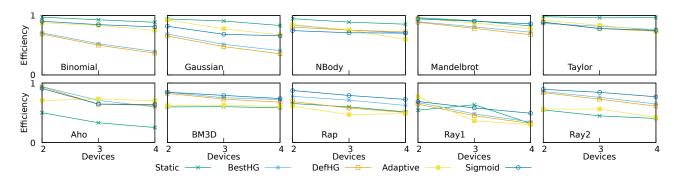

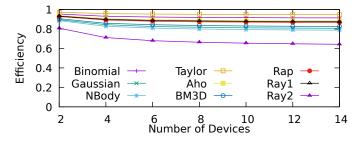

| 4.11. | Efficiency of the different algorithms executing the benchmarks on a homogeneous system.                                   | 69 |

| 4.12. | Estimation of the weak Scalability of Sigmoid algorithm using Gustafson Law                                                | 70 |

| 5.1.  | Header file for a sample task using the heterogeneous system extension                                                                                                                                                                                                                                 | 75  |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.2.  | Header and code for the manual co-execution of a sample task                                                                                                                                                                                                                                           | 76  |

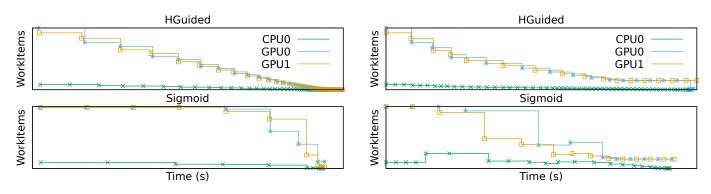

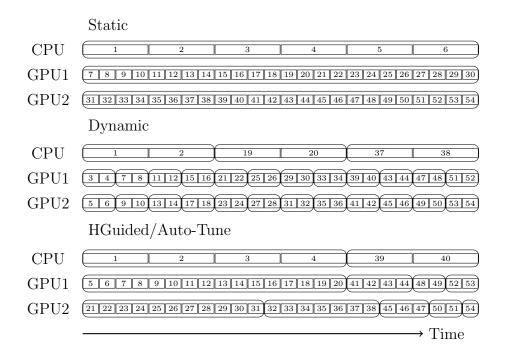

| 5.3.  | Depiction of how the four algorithms perform the data division among three devices. The work groups assigned to each device, identified by numbers, are joined in packages shown as larger rounded boxes. Note that the execution time of work groups in the CPU is four times larger than in the GPUs | 78  |

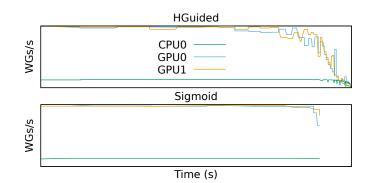

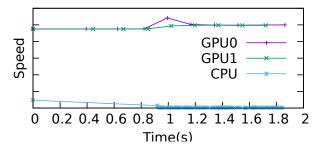

| 5.4.  | Evolution of the computing speed per device.                                                                                                                                                                                                                                                           | 81  |

| 5.5.  | Comparison of the environment variables to use for single device execution and co-execution.                                                                                                                                                                                                           | 86  |

| 5.6.  | OmpSs code and depiction of the children work descriptors generated by the co-execution extension                                                                                                                                                                                                      | 87  |

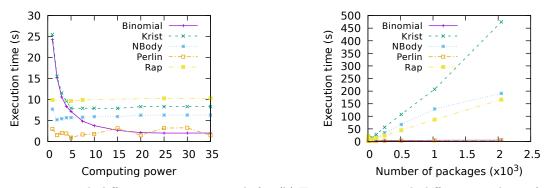

| 5.7.  | Parameter sensitivity analysis                                                                                                                                                                                                                                                                         | 91  |

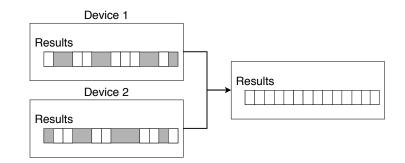

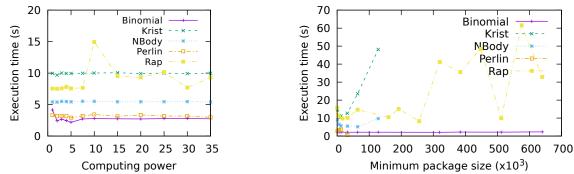

| 5.8.  | Speedup per application                                                                                                                                                                                                                                                                                | 93  |

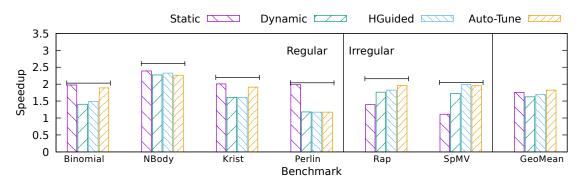

| 5.9.  | Load balance of the heterogeneous system                                                                                                                                                                                                                                                               | 95  |

| 5.10. | Normalized energy consumption per application                                                                                                                                                                                                                                                          | 95  |

| 5.11. | Normalized EDP per application.                                                                                                                                                                                                                                                                        | 96  |

| 6.1.  | Representation of the proposed design for the support of hardware co-execution.                                                                                                                                                                                                                        | 105 |

| 6.2.  | Representation of the proposed design for the support of hardware co-execution.                                                                                                                                                                                                                        | 105 |

| 6.3.  | Example of the operation of the dispatcher in detail.                                                                                                                                                                                                                                                  | 109 |

| 6.4.  | Code for a vector addition OpenCL kernel and equivalent C program                                                                                                                                                                                                                                      | 113 |

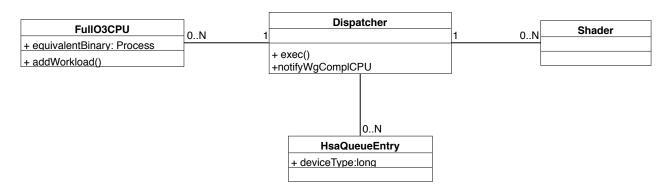

| 6.5.  | Simplified class diagram of the parts of gem5 directly involved in co-execution                                                                                                                                                                                                                        | 115 |

| 6.6.  | Load balance for the evaluated for the evaluated benchmarks using hardware supported co-execution.                                                                                                                                                                                                     | 118 |

| 6.7.  | Speedup for the evaluated for the evaluated benchmarks using hardware sup- |

|-------|----------------------------------------------------------------------------|

|       | ported co-execution                                                        |

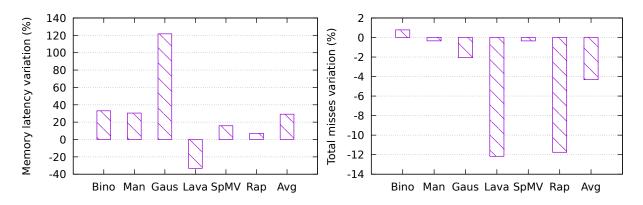

| 6.8.  | Memory access latency variation for the GPU when co-executing              |

| 6.9.  | Total L2 miss variation for the GPU when co-executing                      |

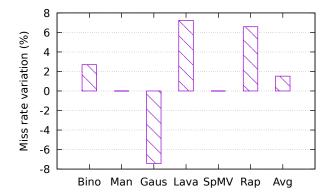

| 6.10. | L2 miss rate variation for the GPU when co-executing                       |

# Chapter 1

# Introduction

Computing systems are the main driving force of science and technology. The need for greater accuracy, more complex models and greater volumes of data, are the sources for ever growing computing requirements. In order to match these needs, computer architects have to overcome technology limitations that challenge the way in which systems are designed. First, it was Dennard scaling, which gave rise to multicore architectures. Now it is Moore's law, which has led to dispute the notion of architectures formed by identical cores. As a result, systems now accommodate devices specialized in accelerating certain workloads, such as GPUs, FPGAs or TPUs, that achieve outstanding performance and energy efficiency. This excellent capabilities have made heterogeneous systems prevalent in the computing world, ranging from supercomputing to mobile devices. However, managing the different devices of a heterogeneous system also poses certain new challenges that need to be addressed. One such is the programming itself, which is far from trivial, requiring significant expertise if all the potential computing capabilities of the system are to be leveraged. Furthermore, these systems combine devices with very different architectures and computing capabilities. This complicates the extraction of their performance and its portability.

## 1.1. Programming heterogeneous systems

The development of code for heterogeneous systems currently relies on *host-device* programming models. Applications following this approach will run on the CPU, and only certain compute intensive parts will be offloaded to the accelerators. Offloads have to be explicitly performed, so the programmer has to decide what to offload and when to do it. Moreover, the management of the data required by the accelerators has to be explicitly handled too, as devices often have their own memory spaces. The result is that the programmer is responsible for managing the whole heterogeneous system and extracting its potential performance, which is a complex task. For this reason, heterogeneous applications are often tailored to a particular system, requiring modifications to work on other systems and compromising portability.

Matters get even worse as systems grow. The more accelerators available, the more orchestration that is necessary, so fully using all the available computing capabilities is ever more challenging and hardly portable. Furthermore, failing to use all the devices represents a waste of energy, as idle devices still consume. So the question is: how can a programmer efficiently use a modern system, such as the DGX SaturnV, which holds 8 GPUs per node? One answer is offloading different workloads to each GPU. This is known as task parallelism, and it is limited by the number of independent tasks that can be extracted from an application. The other option is co-execution.

## 1.2. Co-execution

As opposed to task parallelism, co-execution is based on the cooperation of all the available devices, working on the same problem in a data-parallel fashion. This means that, when a task is launched, it is split, so each device computes for a portion of the total workload. Consequently, each device will produce a disjoint portion of the results. This approach lends itself specially well to heterogeneous environments, as accelerators often base their success on data-parallelism. Co-execution enables the extraction of all the potential performance of the system and also favours its efficient use, specially regarding energy consumption, as all the resources are contributing useful work instead of idling. Additionally, it does not force the programmer to generate parallelism through tasks, which sometimes are not easy to extract, but leverages the parallelism shown by data itself.

Nevertheless, there is an inconvenient. Current programming models favour task parallelism. This means that if co-execution is desired, the programmer will have to handle it himself. The management required includes manually splitting the task, handling the input and output data for each device and explicitly performing the offloads. In short, the programming model requires to express co-execution in terms of task-parallelism. This effectively turns heterogeneous coexecution into a second class citizen, requiring a significant amount of work to implement it.

For heterogeneous co-execution to be a useful option, it needs to be effortless. This is, the execution of a task using a single device should represent a similar effort to its efficient co-execution using all of them. This is, for example, the operation of the OpenMP parallel for clause, which enables the easy distribution of the iterations associated to a for loop to the available threads in a CPU. Effortless co-execution is based on two pillars: abstraction and load balancing.

#### 1.2.1. Abstraction

To minimize the effort required for co-execution, the programmer should operate the same way regardless of the system that will execute the application. In other words, he should not have to be aware of the underlying architecture of the heterogeneous system. This is, all the tasks that directly depend on the devices should be internally handled. As a result, the programmer will no longer have to deal with manual offloads or data distribution to each of the individual devices. This not only eases programming and makes co-execution more accessible, but also favours portability, as an application programmed for a system will work in a different one unmodified, regardless of the number and kind of devices it holds.

#### 1.2.2. Load balancing

The key to extracting all the performance a system has to offer through co-execution, is adequately distributing the workload among all the available devices. In general, the goal is to come up with a work partition that generates equal execution times in all the devices of the system, so they all finish simultaneously and idle times are minimized. In a heterogeneous environment, two aspects must be considered to obtain a balanced distribution: *irregularity* and *heterogeneity*. The former is related to the behavior of the workload, while the latter involves the devices.

Irregularity refers to the behavior of the co-executed workload throughout its runtime. Certain workloads, called *regular*, show equal execution times for equally sized portions of work. On the contrary, *irregular* workloads have varying execution times for chunks of work of the same size. For instance, a sparse matrix-vector product will be irregular, as each row may have a different number of non-zero elements, while a dense matrix-vector product will be regular. Consequently, irregular workloads are more challenging to balance, requiring a certain degree of adaptiveness to react to their changing behavior. However, adaptiveness comes at the price of overheads, which may harm the performance of regular workloads that do not require it.

Heterogeneity is related to the devices that take part in the co-execution. Heterogeneous systems include devices with very different architectures and computing capabilities. These should be taken into consideration to avoid scheduling too much work to a slow device, which might delay the completion of the whole workload. Furthermore, certain architectures require to be scheduled more work than others to fully use their resources, extracting all their potential performance.

Due to these two factors, load balancing decisions are complex, as they depend on the workload and the co-executing hardware. As a consequence, they should not be left to the programmer. A useful co-execution scheme should aid the programmer by offering load balancing algorithms capable of producing balanced work distributions. To make co-execution even easier, these algorithms should also require no input from the programmer. These are *uninformed* algorithms, as opposed to *informed* ones, which require to be provided with certain parameters to operate.

## 1.3. Hypothesis

In light of the above, the aim of the work presented in this dissertation will be evaluating the following hypothesis:

Co-execution can improve the performance and energy efficiency of heterogeneous systems. However, to achieve this, it is necessary to solve two main problems: abstraction and load balancing. To prove this, both hardware and software techniques, including different programming models, will be evaluated. The final goal is to ease the programming of heterogeneous systems, providing support for effortless co-execution that extracts all the performance available. This guarantees that the programming work required to efficiently execute a workload using all the available devices is equivalent to that of using just one.

## **1.4.** Major Dissertation Contributions

The most prominent contributions of the dissertation are listed next. Each of them will be explained in detail in a separate chapter of this document.

- Designing two novel load balancing algorithms: HGuided and Sigmoid are two new load balancing algorithms that specially target heterogeneous systems. HGuided is an informed algorithm that regards the computing speed of the devices and uses a diminishing package size for greater adaptiveness near the end of the co-execution. Sigmoid is an uninformed algorithm that monitors co-execution to adapt to the behavior of the workload. It uses the well-known sigmoid function to control the size of the packages it generates. Both algorithms obtain outstanding results regarding performance and energy efficiency.

- Proposing a heterogeneous co-execution library: Maat is an OpenCL library that achieves effortless co-execution by keeping all the management required by OpenCL under the hood

and implementing HGuided and Sigmoid. It offers high level abstractions that provide the illusion of dealing with a single OpenCL device that represents the aggregated computing capabilities of all the devices of the system. This eases the adaptation of pre-existing OpenCL applications to co-execution. Maat has been implemented with performance in mind. It has low overheads and leverages communication-computation overlapping when possible.

- Extending a task-based programming model with co-execution: OmpSs has been extended to support co-execution as a sample task-based programming model. This enables heterogeneous co-execution with an even higher level of abstraction, closer to sequential programming and not requiring to manage the heterogeneous environment at all. The new functionality has been implemented with minimum impact to OmpSs and preserving its programming philosophy, with load balancing algorithms inspired by OpenMP.

- Designing a dispatcher for hardware supported heterogeneous co-execution: A new hardware dispatcher for integrated heterogeneous systems has been proposed. It considers both CPU cores and GPU compute units in the scheduling of the OpenCL work-groups associated to a kernel launch. Consequently, it enables the programmer to enqueue a kernel to the heterogeneous system and let the hardware handle co-execution. The dispatcher is also capable of throttling co-execution to avoid delays if one of the devices is found to be too slow. The evaluation of the proposed design has been performed using the gem5 simulator.

## 1.5. Methodology

The results presented in this dissertation are based on experimental data obtained from real executions and simulation. This section introduces the platforms used throughout the evaluation, the selected metrics and the tools used to measure the energy consumption. Apart from the generic information provided in this section, later chapters may have their own methodology sections, devoted to the particular details of their experimentation.

#### 1.5.1. Test platforms

Two different platforms have been used for the experimentation. A system called *Batel*, belonging to Universidad de Cantabria, has been used to carry out most of the performance and energy evaluation. To analyze the scalability of the proposed load balancing algorithms, *Hydra* has been used due to its greater device count, which belongs to Universidad de Valladolid. Details on the specific configuration of each of the platforms are provided next.

**Batel** Batel has two CPUs, two GPUs and 16 GBs of DDR3 memory. The CPUs are Intel Xeon E5-2620, with six cores that can run two threads each at 2.0 GHz. The CPUs are connected via QPI, which allows OpenCL to detect them as a single device. Therefore, throughout the remainder of this document, any reference to the CPU includes both Xeon E5-2620 processors. The GPUs are NVIDIA Kepler K20m with 13 SIMD lanes (or SMs in NVIDIA terminology) and 5 GBytes of VRAM each [NVI12]. These are connected to the system using independent PCI 2.0 slots.

**Hydra** Hydra holds four NVIDIA GeForce GTX TITAN Black GPUs, each one having 15 SIMD lanes and 6GB of VRAM. Its greater number of devices will be leveraged to evaluate the scalability of the proposed co-execution techniques.

#### 1.5.2. Evaluated metrics

The contributions presented in this dissertation have been evaluated regarding their performance and energy consumption. The metrics considered in each case are explained next.

#### Performance

Performance has been evaluated using the response time of the selected benchmarks. This includes the time required by the communication between the host and the devices, comprising input and output data transfers, as well as the execution time of the co-executed workload itself.

The benchmarks are executed in two scenarios, the *heterogeneous system*, taking advantage of the GPUs and CPU, and the *baseline*, that only uses one GPU.

Based on these response times, two metrics are analyzed. The first is the speedup for each benchmark when comparing the baseline and the heterogeneous system response times. Note that, for the employed benchmarks, the CPU is much slower than the GPUs. Then, the maximum achievable speedup using n devices will not be n, but a fraction over the number of available GPUs that depends on the computing speed of the CPU for the application. The speedup for each application using a perfectly balanced distribution has also been used to give an idea of advantage of using the complete system. They were derived from the response time  $T_i$  of each device as shown in Equation 1.1.

$$S_{max} = \frac{1}{max_{i=1}^{n}\{T_i\}} \sum_{i=1}^{n} T_i$$

(1.1)

The second metric is the load balancing efficiency, obtained by dividing the obtained speedup by the speedup for the perfectly balanced distribution. The obtained value ranges between 0 and 1, giving an idea of the usage of the heterogeneous system. Efficiencies close to 1 indicate the best usage of the system is being made. The measured values do not reach this ideal because of the communication overheads and host-device interactions.

#### Energy

Regarding energy, the same two scenarios are considered as in the performance evaluation. However, in the baseline scenario the energy consumed by the idle devices is also taken into account. This is a fair comparison, as idle devices still consume static energy. Moreover, using an accelerator while the rest of the system is idle is a typical scenario favoured by hostdevice programming. Apart form the total consumed energy, the Energy Delay Product (EDP) [CCBB15] has also been used. It is a metric that combines performance and energy to evaluate the efficiency of the system. The tool used to measure the energy of the devices will be introduced next.

#### **1.5.3.** Energy measurements

To measure the energy consumption of the system it is necessary to take into account the power drawn by each device. Modern computing devices allow applications to monitor their functionality and performance. However, the power measured is associated to the device and not the kernel or process in execution. Together with the fact that it is impractical to add measurement code to all the test applications, this led to the development of a power monitoring tool named *Sauna*. It takes a program as its parameter, and is able to periodically query all the devices for power measurements throughout the execution of the program.

A significant amount of thought went into the conception of Sauna; the fact that it had to monitor several devices meant that it had to adapt to the particularities of each one while giving consistent and homogeneous output data. This started with the different APIs provided to perform these measurements. For the Intel CPUs, recent versions of the Linux kernel provide access to the *Running Average Power Limit (RAPL)* registers [RNR<sup>+</sup>11], which provide accumulative energy readings. On contrast, NVIDIA provides the *NVIDIA Management Library* (*NVML*) [NVI18] that gives instant power measurements. Naturally, Sauna had to be able to convert between the two magnitudes. A particularly interesting aspect of the development process of Sauna was studying the impact of the sampling frequency. In order to keep the program simple, it was necessary to use a single sampling period for all devices. Given that the power variations would be similar across devices, the idea seemed feasible.

To find the best frequency, a series of experiments were made for each device in *Batel* (Section 1.5.1). It was observed that each device reacted differently to the sampling frequency. The RAPL measurements grew with large frequencies. And more surprisingly, the NVIDIA devices slowed down noticeably when the sampling frequency was above a given threshold. This actually meant that the kernel running in the device took longer to complete. Figure 1.1 shows these effects as the magnitude of the variation of the measured CPU power depending on the sampling rate, together with the execution time of a Binomial kernel on a NVIDIA GPU. These graphs suggest adopting a low frequency, however, if the sampling period is too long, fast power spikes that may appear under irregular loads could be missed, leading to inexact results. As a

Figure 1.1: Impact of sampling period on power measurement and kernel execution time.

consequence it was decided to use 45ms as the sampling period for all the remaining experiments, as it balances overhead and accuracy.

### **1.6.** Document Structure

#### This dissertation is organized as follows:

Immediately following this introduction, Chapter 2 provides some background on the programming of heterogeneous systems, including OpenCL and OmpSs, and introduces the gem5 simulator. It also analyses the most notable related work on co-execution, heterogeneous system abstraction and load balancing.

Chapter 3 defines the load balancing problem formally and presents two novel load balancing algorithms designed for heterogeneous co-execution. HGuided stems from the need to reduce the overheads of dynamic load balancing techniques while preserving adaptiveness. The algorithm is first explained to then elaborate on its limitations. Sigmoid builds on the foundation of HGuided. It is an uninformed algorithm that monitors co-execution at runtime. The reasoning to obtain the workload division function of Sigmoid is first introduced to then detail how its internal parameters are tuned.

Chapter 4 presents Maat, an OpenCL library for effortless heterogeneous co-execution that provides the programmer with the illusion of handling a single device that represents the aggregate computing power of the whole system. An overview of Maat is provided first, to then dive into the design of the abstractions that it enables. These strive to preserve the OpenCL approach to parallel programming to ease the use of the library. The implementation of Maat is explained next, to then evaluate the performance, energy and scalability of the load balancing algorithms implemented in Maat, which are HGuided and Sigmoid.

Chapter 5 introduces an extension to OmpSs, as a sample task-based programming model, to support heterogeneous co-execution. First, the chapter elaborates on the best design approach to include co-execution in the OmpSs infrastructure. Then, the proposed load balancing techniques for co-execution in task-based programming models are introduced which, to accommodate to the philosophy of OmpSs, resemble the ones of OpenMP. How co-execution was implemented with minimum impact to OmpSs is explained next to finally evaluate the proposal in terms of performance and energy.

Chapter 6 proposes a new dispatcher design for co-execution in integrated heterogeneous systems. The chapter first discusses on the best way to support hardware aided co-execution in integrated CPU-GPU architectures, both from software and hardware. It then proposes a design with low impact on both OpenCL and the system architecture. How the dispatcher throttles co-execution to prevent delays from slow devices is explained next, to then dive into how the proposed design was implemented in the gem5 simulator. Finally, the proposed dispatcher is evaluated in terms of performance, as gem5 currently does not model the energy consumption of the GPU.

Lastly, the dissertation ends with Chapter 7, which presents some conclusions and future lines of work.

# Chapter 2

# **Background and Related Work**

Over the past few years, the development of heterogeneous platforms has been followed by an effort, both from academia an industry, to produce the necessary tools to efficiently use this kind of systems. This includes both the required software support to be able to program heterogeneous devices and the simulation environments to model their architecture and evaluate their capabilities. The purpose of this chapter is twofold: first, it introduces the key technologies and tools that the thesis has been built upon, and second, it presents some works that are related to the research field of co-execution.

## 2.1. Programming models

The main challenge of programming heterogeneous systems stems from their strength: the collaboration of several architectures to solve a problem may be highly advantageous, but the careful orchestration and management of very different devices is a problem to be solved in order to reap the benefits of heterogeneity. A very common approach is to deem the CPU as the host, while the rest of the devices are considered accelerators that will run certain offloaded parts of the applications. This concept, often referred to as "Host-Device Programming Model", lies at the core of the two most prominent heterogeneous programming frameworks: CUDA [KH10a] and OpenCL [GHK<sup>+</sup>11]. Both frameworks share many features and have a very similar

approach to heterogeneous systems. However, the former is a NVIDIA proprietary technology, so it is only supported by NVIDIA GPUs. Moreover, CUDA does not support the execution of a kernel in other kinds of devices, such as CPUs, which forces to develop and maintain several versions of the same program. For these reasons and considering that one of the goals of the thesis is being able to adapt to different configurations and types of heterogeneous devices, OpenCL has been used as a basis for the development and experimentation of this research.

Nevertheless, OpenCL has a caveat. It offers a low level of abstraction, leaving the programmer alone with the responsibility of manually managing data and devices individually. To explore a greater level of abstraction, the OmpSs extension to support OpenCL has also been used in this work, precisely in the areas related to Chapter 5. The following subsections are devoted to introducing the main features of OpenCL and OmpSs.

## 2.1.1. Heterogeneous programming in OpenCL

OpenCL [SGS10, KMSZ15], released by the Khronos Group in 2008, is a standard framework for the development of applications that will run on heterogeneous systems. One of the main advantages of OpenCL is its adaptiveness, as it is not limited to hardware of a certain type or from a particular vendor. Given an adequate OpenCL driver, which should be supplied by the hardware vendors, any application following the specification will run adequately on any device, ranging from GPUs [KH10b] or Xeon Phi [Rah13] to FPGAs [DGNGT<sup>+</sup>19]. This allows for the development of portable applications that can be accelerated regardless of the characteristics of the underlying system.

OpenCL implements a Host-Device approach to heterogeneous programming, depicted in Figure 2.1. One device, known as the host, is in charge of the management of the heterogeneous system, while the others act as accelerators, working on the more compute-intensive portions of the work offloaded to them by the host. To achieve this, OpenCL is formed by two parts: a C application programming interface (API) and a programming language. The API works as an abstraction layer. It implements hardware independent functions to manage the heterogeneous devices, offload work to them and perform data transfers. This works towards one of the main features

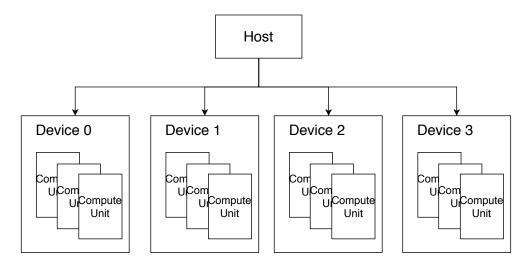

Figure 2.1: The Host-Device programming model.

of OpenCL, which is portability. The offloaded work is expressed in the form of functions implemented in OpenCL C, a subset of C99 with certain extensions for data-parallelism. The abstractions offered by OpenCL through its API and the data parallel programming model it follows will be explained next.

#### **Device** abstraction

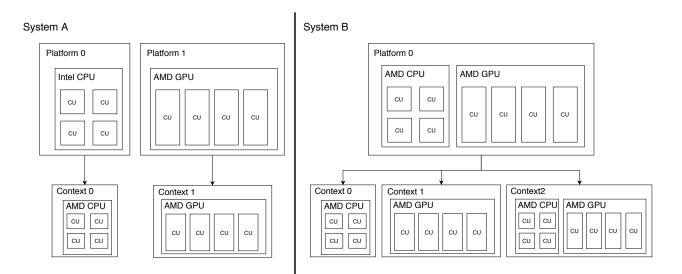

To guarantee that an OpenCL application can run on any hardware configuration, devices are treated abstractly. The abstraction is based on four main concepts: compute units, platforms, contexts and command queues. Devices are defined as a combination of *compute units*, as shown in Figure 2.1, which are functionally independent computation elements. For example, a 4 core CPU is regarded as a combination of 4 compute units or a GPU with 13 stream multiprocessor as comprised by 13 compute units. Devices are also grouped in *platforms*, which are representations of the OpenCL implementations available in the system. These are usually vendor specific. For instance, lets define system A and system B, depicted in Figure 2.2. System A comprises an Intel CPU and an AMD GPU whereas in system B both the CPU and the GPU are AMD. Considering the definition of a platform, System A has two platforms, one for the CPU and another one for the GPU. For System B, in turn, only one platform would be available, comprising all the devices. The OpenCL specification then defines the *context* as a representation of a combination of devices belonging to a platform, that will be

Figure 2.2: Platform and context possibilities for two sample systems.

used in the computation. In our example systems, one context per platform would be available in A, while 3 would be possible for B: one containing only the CPU, one containing only the GPU and a third one containing both the CPU and the GPU. Note that there is no context in system A comprising both the CPU and the GPU, as they belong to different platforms. Lastly, the *command queue* is the abstraction used to communicate with a specific device by performing data transfers, offloading work or waiting on certain events. The management of these structures is performed through the API. Considering the above, the initial steps of an OpenCL application would be:

- 1. Identifying the available platforms.

- 2. Selecting a context containing the devices that are to be used.

- 3. Creating the necessary command queues to communicate with the devices.

#### **Execution** abstraction

The OpenCL API offers functions to specify the work to be executed by the devices and perform the offload operation. *Kernels* are defined as functions that will be executed by a device. These represent the work to be performed by each launched thread or, as referred to in OpenCL terminology, *work-item*. OpenCL also defines the notion of a *work-group* as a set of work-items that are able to progress in the presence of barriers and that can synchronize. This implies that the work-items of a work-group need to be executed concurrently in a compute unit, to guarantee that a switch is possible and relatively inexpensive provided a work-item has to block. The OpenCL specification enforces this requirement, however the actual mapping of workgroups to hardware components is both architecture and OpenCL implementation dependent. Synchronization between work-items belonging to different work-groups is undefined. Kernels are expressed in OpenCL C which, among other extensions, offers functions that enable the work-items to identify themselves in their work-group and in the whole body of work-items that have been launched.

On the host code side, kernels are represented in an abstract manner using a data structure also known as kernel. These are context and device dependent structures, as the OpenCL C code needs to be compiled for each of the architectures that will execute it. The API offers the necessary function to create kernels (data structure), compile them, specify the arguments they use and launch them. Each kernel offload operation has to be accompanied by a specification of the number of work-items to be launched in the device and their distribution. This is defined using two parameters of the kernel offload function: the *global\_work\_size* and the *local\_work\_size*. The former specifies the total number of work-items to spawn and the latter the number of work-items for each work-group, implicitly specifying the total number of work-groups. A third parameter, the *global\_work\_offset* is also available, which acts as a displacement for the workitem id calculation. These three parameters may have up to 3 dimensions to adapt to different problems and algorithmic approaches.

#### Memory abstraction

Considering that the heterogeneous resources of a system are usually independent pieces of hardware, the memory spaces of a device and that of its host have been traditionally considered as separated. There are some examples of recent hardware that implements shared memory between host and devices. However, in this kind of systems, memory sharing is often offered at the cost of a highly degraded performance due to overheads. For this reason and considering

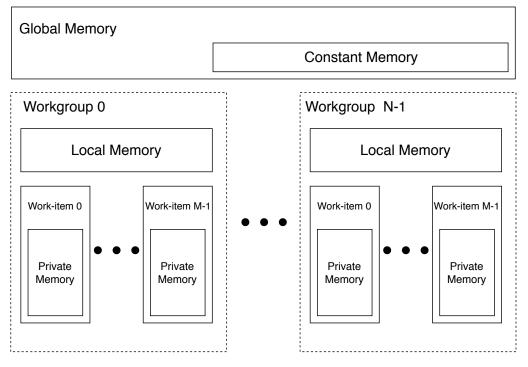

Figure 2.3: OpenCL memory model.

that separate memory spaces are still the norm, they have been the focus of this work. Moreover, the proposed techniques would also apply to shared memory systems if they become a viable option for performance in the future.

To account for separate memory spaces, data transfers are necessary to both provide the accelerators with input data for the offloaded work and to retrieve the results. Furthermore, these transfers need to be performed in an abstract fashion to preserve portability. The OpenCL standard defines the *buffer* as a memory address that is valid in the memory of an OpenCL device. The OpenCL API offers functions to create buffers on devices and to enqueue read and write operations on the command queues associated to them. These operations have the host as originator, so, for example, a read implies a data movement from a device memory to the host memory. Transfers can also be blocking or non-blocking, to control whether the host has to wait for the transfers to complete or can continue executing.

For flexibility, OpenCL also defines an abstract memory model. It defines four different memory spaces as shown in Figure 2.3. Both the *Global* and *Constant* memory spaces are shared by every work-item of a kernel launch, while every work-group has its own *Local* memory. This is a programmer managed memory space, commonly used as a scratchpad for fast collaboration

and data sharing at the work-group level. Each work-item has its own *Private* memory. The mapping of memory spaces to actual hardware is implementation dependent.

## 2.1.2. Task-based programming languages

Writing parallel code is a challenging task, as it requires to orchestrate the execution of several different devices. This includes managing the distribution of data to the devices as necessary, and also deciding what parts of the application can be run in parallel and when to launch them. The resulting applications are often complex and hard to maintain. Task-based programming languages strive to make the programming of this kind of systems simpler, by keeping it closer to traditional, sequential programming. Their take on parallelism is based on the *task* concept, which is often a function that may be executed in parallel. The programmer is then in charge of defining tasks and the data they use, leaving the management of their execution to a runtime, and thus making programming easier.

OmpSs is a programming model, created and maintained by the Barcelona Supercomputing Center, for the development of parallel applications. It was originally based on OpenMP [ope15] and StarSs [PBL08] but supports heterogeneous systems, both using CUDA and OpenCL, through an extension [DAB<sup>+</sup>11, F. 14].

OmpSs proposes a data-flow driven parallel programming model, in which tasks are asynchronously executed in parallel. Tasks are declared using compiler directives in the code of the application. The data dependencies between tasks are also declared through pragmas, so OmpSs can build a dependence graph and automatically execute tasks when their input data are ready. This is obtained thanks to the two main pieces that build OmpSs:

- *Mercurium*, which is a source-to-source compiler that processes certain directives (pragmas) and generates the actual code of the parallel application that will be executed [Mer].

- *Nanos++*, which is a runtime library that provides the necessary functionality for the application generated by Mercurium to be able to run. These include the creation of

```

#pragma omp task in([n]a) out([n]b)

void task1(int n, int * a, int * b)

#pragma omp task in([n]c) out([n]d)

void task2(int n, int * c,int * d)

#pragma omp task in([n]e) out([n]f)

void task3(int n, int * e, int * f)

#pragma omp task in([n]g, [n]h)

int task4(int n, int * g, int * h)

```

Figure 2.4: Headers for the tasks.

tasks, the generation and management of the dependence graph, the management of data and the launch of tasks when their data is available [Nan].

When a parallel program is executed, a thread pool is created with only one thread, the master, set as active. This thread uses the capabilities of Nanos++ to create tasks as specified in the pragmas and translated by Mercurium. Figure 2.4 shows the definition of four sample OmpSs tasks. Tasks are internally identified by *work descriptors* and added to the dependence graph, taking into account the information on data provided in the *in* and *out* clauses. In our example, function task1 is defined as a task using a as input and b as output (task2-4 are equivalently defined). Figure 2.5 shows an example launch of the tasks defined in Figure 2.4 and the dependence graph that it would generate. The master thread then schedules tasks to the available threads as soon as their input data is ready or, in OmpSs terminology, when their dependencies are satisfied. In the example, tasks 2 and 3 will be launched as soon as task 1 finishes, while task 4 will have to wait for the termination of tasks 2 and 3 to be executed.

## 2.2. Heterogeneous system simulation in gem5

Gem5 [BBB<sup>+</sup>11] is a modular simulation platform for computer-system architecture research, encompassing system-level architecture as well as processor microarchitecture. It provides several interchangeable CPU models, ranging from a simple processor to a detailed out-of-order CPU model, and four different architectures: Alpha, ARM, SPARC and x86. For the memory

(a) Launch of the tasks.

(b) Generated DAG.

Figure 2.5: Code for the launch of the tasks and generated OmpSs dependence graph.

subsystem, gem5 features Ruby, an event-driven simulator that models caches, crossbars, snoop filters and the DRAM. Gem5 supports two execution modes: *syscall emulation*, in which only the binary of an application is executed in the simulated system, and *full-system*, in which the complete OS is executed. All these capabilities make Gem5 the *de facto* standard architecture simulation tool in academic research. Regarding heterogeneous systems, the stable version of Gem5 includes a GPU model that represents an integrated SoC with support for shared virtual memory with the host CPU. This feature and its OpenCL backend, which are specially interesting for the study of integrated heterogeneous systems, will be explained next.

#### 2.2.1. The GPU model

To simulate integrated heterogeneous systems, gem5 offers the GPU model. Proposed in [BMB15, GBD<sup>+</sup>18], it is modelled after the architecture of GCN AMD GPUs [AMD12]. In GCN, the GPU is formed by a set of *compute units*, an example of which is depicted in Figure 2.6. Each compute unit holds 4 SIMD units that can process 16 work-items in parallel and a private L1 data cache. Each group of 4 compute units shares an L1 instruction cache, while the L2 is distributed and shared among all the compute units. L1 caches are write-through, so they are kept coherent with the L2 cache, which is write-back. Both are virtually addressed, so the memory hierarchy is integrated with x86 microprocessors and the memory space shared. Coherence with main memory is kept through a protocol called Viper. All the compute units also share a front-end, which is in charge of storing the information of kernels and dispatching

Figure 2.6: Representation of the GCN compute unit. Taken from: White Paper. AMD GRAPHICS CORES NEXT (GCN) ARCHITECTURE [AMD12]. Copyright AMD

work-groups to compute units. Regarding the complete GCN heterogeneous system, the CPU and GPU are two independent devices that can communicate and share the main memory.

## 2.2.2. OpenCL support

As explained in Section 2.1.1, OpenCL devices require a driver to communicate the runtime and the hardware through the OS. Adequating the GPU model to the working of a real driver would be very complex, as would be implementing a new, tailor-made driver. The implementation of the gem5 GPU model chooses to avoid the OS altogether, by implementing its own OpenCL backend and executing in syscall emulation mode. Consequently, OpenCL applications need to be compiled using a modified library that calls the necessary specific functions of the backend. Kernels also require a special treatment. They need to be compiled using CLOC, an offline compiler that generates an HSA object, which is then interpreted by the gem5 GPU model.

Two important limitations are worth noting. First, the GPU Model does not implement the complete GCN ISA. As a result, certain valid OpenCL kernels are rejected by the OpenCL backend and generate an error when the application is executed. This has proven an issue when running benchmarks on the simulator. Second, the backend and modified OpenCL library have no support for the execution of OpenCL on CPUs. This limitation will be addressed in the

implementation of hardware support for co-execution.

## 2.3. Related Work

Heterogeneous architectures have quickly permeated every computing system, ranging from large scale supercomputing servers to portable devices. This proliferation has given rise to an interest in how to adequately use the extra computing power and efficiency that these architectures offer [KC18]. This is a multi-faceted problem, as it involves hiding both the difficulties of handling several devices and the complexity of load balancing, which may be deeply influenced by the available devices and the workload to co-execute itself.

#### 2.3.1. System abstraction

To abstract the programmer from the management of the resources available in the heterogeneous system, a framework is usually offered. It acts as an intermediate layer, separating the programmer from the underlying heterogeneous programming framework, such as OpenCL, and providing access to a virtual device that represents the whole system. This is achieved by using a combination of runtimes [LSPM15, YWTC15, PG14, HCY<sup>+</sup>14, APnBF16, DMSD16, BBK17, GLMR13, LSM15, ZH13, KSL<sup>+</sup>12, LSPM13, CGS<sup>+</sup>15], compilers [KKLL11, KSL<sup>+</sup>12], kernel code modifications [HCB16, LSM15, LSPM13, LSPM15], libraries [dlLTBR12] and hardware support [CGS<sup>+</sup>15]. Out of these works, [LSPM15, PG14, KKLL11, HCB16, dlLTBR12, LSPM13] target co-execution, whereas the rest focus on task-parallel approaches. These orchestrate the execution of different tasks or kernels and manage data dependencies, in a similar manner to OmpSs. On the contrary, co-execution poses the special challenge of keeping the memory of the devices consistent, as they all collaborate on the computation of a single kernel. To do so, these frameworks either keep track of data differences to merge the results in the GPU at the end of the execution [PG14], or perform complex buffer access analysis to identify patterns and split data accordingly among each of the available devices [KKLL11, LSPM15, HCB16, LSPM13]. These are often costly operations that represent a significant overhead.

## 2.3.2. Load balancing