# Facultad de Ciencias

Optimización de aplicaciones y equilibrio de carga en sistemas heterogéneos con Xeon Phi

(Application performance optimization and load balancing in Xeon Phi based heterogeneous systems)

Trabajo de Fin de Grado para acceder al

### **GRADO EN INGENIERÍA INFORMÁTICA**

Autor: Adrián Herrera Arcila

**Director: José Luis Bosque Orero**

Septiembre - 2017

# Índice general

| Ín | dice  | de figuras                                                    | IV   |

|----|-------|---------------------------------------------------------------|------|

| Ín | dice  | de cuadros                                                    | v    |

| A  | grade | ecimientos                                                    | VI   |

| Re | esum  | nen en                                                        | VII  |

| A۱ | ostra | act                                                           | VIII |

| 1. | Intr  | roducción                                                     | 1    |

|    | 1.1.  | Sistemas heterogéneos                                         |      |

|    | 1.2.  | Objetivos y plan de trabajo                                   |      |

|    | 1.3.  | Estructura del documento                                      | 3    |

| 2. | Esta  | ado del arte                                                  | 4    |

|    | 2.1.  | Intel Xeon Phi                                                | 5    |

|    |       | 2.1.1. Aspectos clave y arquitectura                          | 5    |

|    | 2.2.  | Modelo de programación                                        | 7    |

|    |       | 2.2.1. OpenMP: memoria compartida                             | 7    |

|    |       | 2.2.2. Modo nativo                                            | 9    |

|    |       | 2.2.3. Modo descarga (offload)                                | 9    |

|    | 2.3.  | Algoritmos de equilibrio de carga                             | 10   |

|    |       | 2.3.1. Pre-análisis estático                                  | 10   |

|    |       | 2.3.2. Dinámico en tiempo de ejecución                        | 11   |

| 3. | Opt   | imización de aplicaciones para el Xeon Phi                    | 12   |

|    | 3.1.  | Identificando las cargas de cómputo paralelizables            | 12   |

|    | 3.2.  | Paralelizando el código                                       |      |

|    | 3.3.  |                                                               | 14   |

|    | 3.4.  | Otros aspectos relevantes                                     | 16   |

|    |       | 3.4.1. Alineamiento de estructuras de datos                   | 16   |

|    |       | 3.4.2. Índices de los subconjuntos de datos                   | 16   |

|    | 3.5.  | Ejemplo práctico                                              | 18   |

| 4. | Alg   | oritmos de equilibrio de carga                                | 21   |

| ⅎ. | _     | ¿En qué consiste el equilibrio de carga? Algunas aclaraciones | 21   |

|    | 4.2.  | Tipos de aplicaciones según su carga computacional            | 22   |

|    |       | 4.2.1. Aplicaciones con carga regular                         | 22   |

|    |       | 4.2.2. Aplicaciones con carga irregular                       | 22   |

|    | 4.3.  |                                                               | 24   |

|    |       | 4.2.1. Le transferencia de dates des un problema?             | 24   |

|              |                                                                               | 4.3.2. Un modelo de cómputo, primera aproximación                                                                                                                                | $\frac{26}{29}$ |  |  |  |  |  |  |

|--------------|-------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--|--|--|--|--|--|

|              | 4.4.                                                                          | Dinámico en tiempo de ejecución                                                                                                                                                  | 31              |  |  |  |  |  |  |

|              |                                                                               | 4.4.1. Funcionamiento del algoritmo                                                                                                                                              | 31              |  |  |  |  |  |  |

|              |                                                                               | 4.4.2. Efectos de la longitud de segmento elegida                                                                                                                                | 32              |  |  |  |  |  |  |

|              |                                                                               | 4.4.3. Reutilización de la memoria en el acelerador, reduciendo el sobrecoste $$                                                                                                 | 32              |  |  |  |  |  |  |

| <b>5.</b>    |                                                                               | luaciones y resultados                                                                                                                                                           | 33              |  |  |  |  |  |  |

|              | 5.1.                                                                          | rate Production and American                                                                                                                                                     | 33              |  |  |  |  |  |  |

|              | 5.2.                                                                          | *                                                                                                                                                                                | 34              |  |  |  |  |  |  |

|              |                                                                               | 5.2.1. Carga regular: simulación N-body                                                                                                                                          | 34              |  |  |  |  |  |  |

|              |                                                                               | 5.2.2. Carga irregular: filtrado específico de cualidades en una imagen                                                                                                          | 35              |  |  |  |  |  |  |

|              | 5.3.                                                                          | Desarrollo de las pruebas                                                                                                                                                        | 37              |  |  |  |  |  |  |

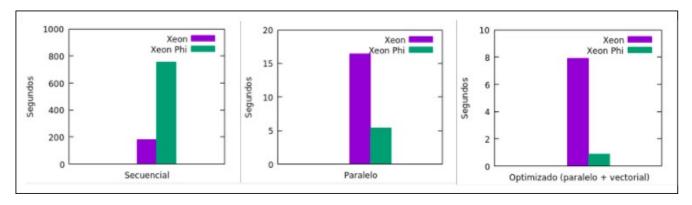

|              |                                                                               | 5.3.1. Optimización de la simulación N-body para el Xeon Phi                                                                                                                     | 37              |  |  |  |  |  |  |

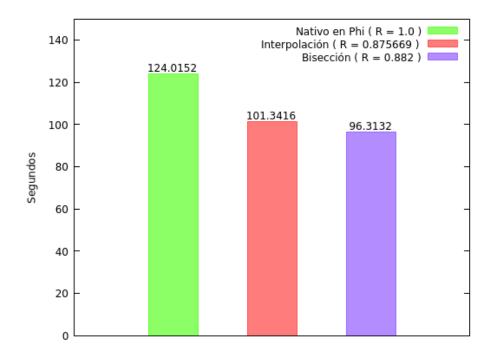

|              |                                                                               | <ul><li>5.3.2. Equilibrio de carga estático mediante interpolación para N-body</li><li>5.3.3. Equilibrio de carga estático mediante el método de bisección para N-body</li></ul> | 40<br>43        |  |  |  |  |  |  |

|              |                                                                               | 5.3.4. Equilibrio de carga dinámico para filtrado de imagen con representación matricial dispersa                                                                                | 45              |  |  |  |  |  |  |

|              | 5.4.                                                                          |                                                                                                                                                                                  | 48              |  |  |  |  |  |  |

|              | 0.1.                                                                          | 5.4.1. Simulación N-body optimizada                                                                                                                                              | 48              |  |  |  |  |  |  |

|              |                                                                               | 5.4.2. Pre-análisis estático en la simulación N-body: interpolación y bisección                                                                                                  | 49              |  |  |  |  |  |  |

|              |                                                                               | 5.4.3. Equilibrio de carga dinámico para el filtrado de imágenes con valores dis-                                                                                                |                 |  |  |  |  |  |  |

|              |                                                                               | persos                                                                                                                                                                           | 51              |  |  |  |  |  |  |

| 6.           | Con                                                                           | nclusiones y trabajos futuros                                                                                                                                                    | 53              |  |  |  |  |  |  |

|              | 6.1.                                                                          | Conclusiones                                                                                                                                                                     | 53              |  |  |  |  |  |  |

|              |                                                                               | 1                                                                                                                                                                                | 54              |  |  |  |  |  |  |

|              | 6.3.                                                                          | Trabajos futuros                                                                                                                                                                 | 54              |  |  |  |  |  |  |

| $\mathbf{G}$ | osar                                                                          | io                                                                                                                                                                               | <b>5</b> 6      |  |  |  |  |  |  |

| Bi           | bliog                                                                         | grafía                                                                                                                                                                           | <b>5</b> 8      |  |  |  |  |  |  |

| Aı           | iexos                                                                         | ${f s}$                                                                                                                                                                          | 60              |  |  |  |  |  |  |

| Aı           | iexo                                                                          | A. Código base de la simulación N-body (una iteración)                                                                                                                           | 61              |  |  |  |  |  |  |

| Aı           | iexo                                                                          | B. Código paralelo de la simulación N-body (una iteración)                                                                                                                       | 63              |  |  |  |  |  |  |

| Aı           |                                                                               | C. Código optimizado de la simulación N-body (una iteración) y programa<br>ncipal                                                                                                | 65              |  |  |  |  |  |  |

| Aı           | iexo                                                                          | D. Reporte de compilación                                                                                                                                                        | 68              |  |  |  |  |  |  |

| Aı           |                                                                               | E. Programa de descarga para la simulación N-body y división de las ciones de ésta.                                                                                              | 69              |  |  |  |  |  |  |

| Aı           | nexo F. Implementación nativa y de descarga para el filtrado de matrices dis- |                                                                                                                                                                                  |                 |  |  |  |  |  |  |

# Índice de figuras

| 2.1. | número                                                                                                                                                                                                                                                                            |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.2. | Intel destaca la reducción de costes asociados al desarrollo de software debido a la compatibilidad del Phi. Aquí "accelerators" hace referencia a las GPUs. Fuente:                                                                                                              |

| 2.3. | Intel                                                                                                                                                                                                                                                                             |

| 2.4. | Modelo de memoria en OpenMP                                                                                                                                                                                                                                                       |

| 2.5. | Modelo de ejecución en OpenMP                                                                                                                                                                                                                                                     |

| 2.6. | Nativo vs. Offload.                                                                                                                                                                                                                                                               |

| 2.7. | Diferencias entre carga regular e irregular                                                                                                                                                                                                                                       |

| 3.1. | Escalabilidad del Xeon Phi respecto al Xeon. Fuente: [10]                                                                                                                                                                                                                         |

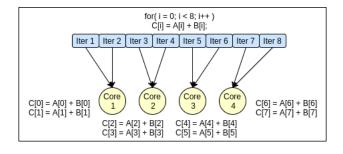

| 3.2. | Paralelización de un bucle                                                                                                                                                                                                                                                        |

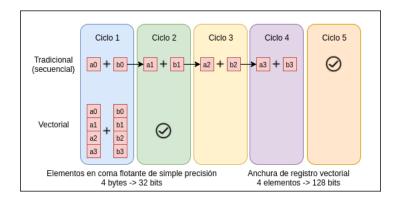

| 3.3. | Funcionamiento de la vectorización                                                                                                                                                                                                                                                |

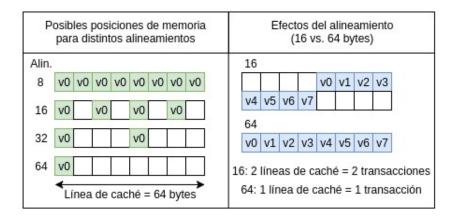

| 3.4. | Fundamentos del alineamiento                                                                                                                                                                                                                                                      |

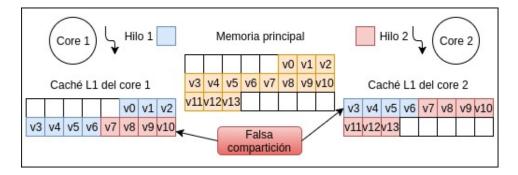

| 3.5. | Falsa compartición                                                                                                                                                                                                                                                                |

| 4.1. | Distintas formas de equilibrar la carga                                                                                                                                                                                                                                           |

| 4.2. | Diferencias en las cantidades de información                                                                                                                                                                                                                                      |

| 4.3. | Diferencias entre la carga regular y la irregular en un bucle de procesado                                                                                                                                                                                                        |

| 4.4. | Comparación del impacto de las fases de transferencia                                                                                                                                                                                                                             |

| 4.5. | Complejidad temporal. La variable n representa el tamaño del problema. Fuente: [22]                                                                                                                                                                                               |

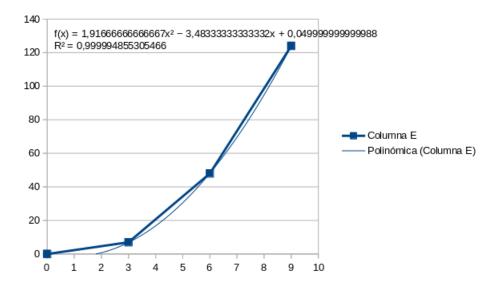

| 4.6. | Interpolación de una función de coste computacional $O(n^2)$ en LibreOffice Calc.<br>Los percentiles elegidos sobre el intervalo $[0,10]$ han sido $0/30/60/90\%$ . El polinomio $f(x)$ es el resultado aproximado de la función real, y $R^2$ es el coeficiente de determinación |

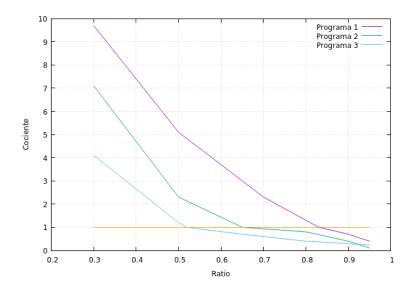

| 4.7. | Ratio óptimo para un cociente de 1.0 en tres programas distintos                                                                                                                                                                                                                  |

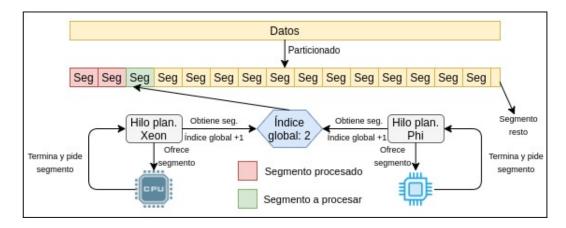

| 4.8. | Algoritmo dinámico de asignación de segmentos                                                                                                                                                                                                                                     |

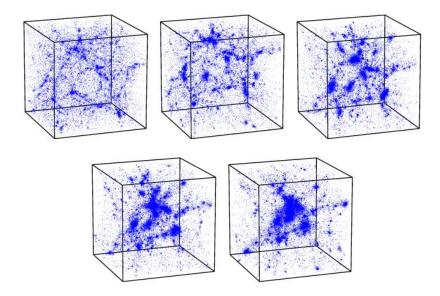

| 5.1. | Evolución de la simulación N-body en la que los cuerpos tienden a colapsar debido a las fuerzas gravitacionales. Fuente: [29]                                                                                                                                                     |

| 5.2. | Filtrado de una imagen de $8x6$ píxeles para $c$ rojo. Se observa cómo la saturación                                                                                                                                                                                              |

|      | central se mantiene y la exterior varía                                                                                                                                                                                                                                           |

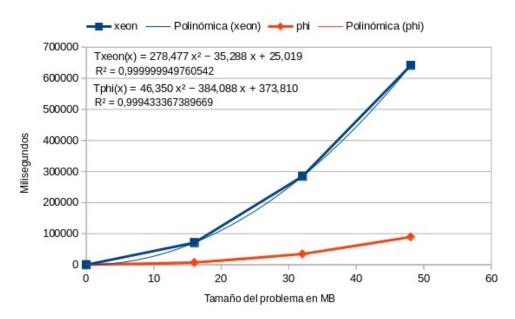

| 5.3. | Interpolación de las ecuaciones temporales de ambos componentes hardware para                                                                                                                                                                                                     |

|      | la simulación N-body.                                                                                                                                                                                                                                                             |

| 5.4. | Ejecución del script de bisección                                                                                                                                                                                                                                                 |

| 5.5. | Relación entre los dos componentes para las tres iteraciones del algoritmo                                                                                                                                                                                                        |

| 5.6. | Tiempo empleado en realizar la simulación para los distintos ratios                                                                                                                                                                                                               |

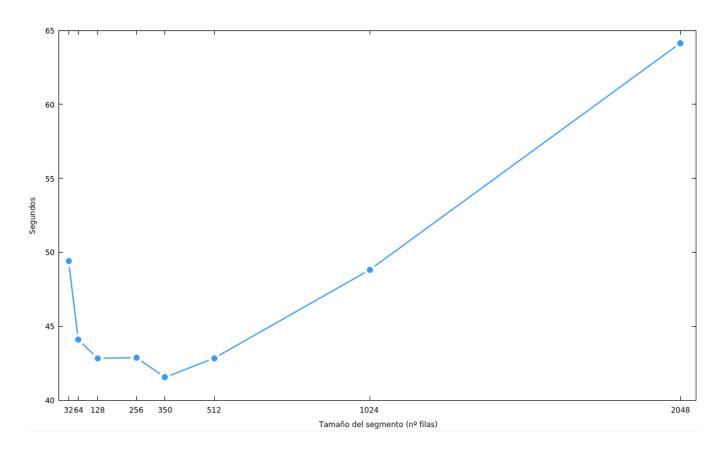

| 5.7. | Impacto del tamaño de segmento en el algoritmo dinámico                                                                                                                                                                                                                           |

# Índice de cuadros

| 4.1. | Análisis del modelo de transferencia de memoria. Resultados en milisegundos (ms). | 25 |

|------|-----------------------------------------------------------------------------------|----|

|      | Mediciones en milisegundos del tiempo de ejecución del núcleo N-body              |    |

| 5.2. | Resultados en segundos para la simulación N-body con 100000 partículas            | 48 |

| 5.3. | Resultados de rendimiento para el filtrado de imagen con distintas longitudes de  |    |

|      | segmento                                                                          | 51 |

# Agradecimientos

A mis padres por confiar en mí, dejarme tanto acertar como errar en mis decisiones y aprender del proceso; por apoyarme, animarme y aguantarme día tras día; por subirme a hombros cuando quiero tocar las nubes y por bajarme al suelo suavemente cuando me doy cuenta de que no puedo.

A mis amigos por estar siempre ahí para compartir y disfrutar momentos juntos, para ayudarme cuando lo he necesitado y para abstraerme de las dificultades.

A todos los profesores que me han enseñado a apreciar el aprendizaje durante estos años y que se han esforzado en transmitirme su pasión, especialmente a José Luis Bosque, director de esta investigación que ha confiado en mí para llevarla a cabo, me ha guiado en los momentos en los que no veía un camino a seguir y me ha inspirado para esforzarme en no dejar de creer en ella.

Finalmente a todas las personas que se levantan por la mañana con la intención de ayudar y aportar a la sociedad, ya sea a su familia, a su comunidad o a su país, gracias a ellos creo en el progreso de la humanidad y estoy feliz de sumarme a través de mi pasión mientras sea útil.

## Resumen

La curiosidad del ser humano es innata e infinita, para muchos forma parte del sentido de la vida, pero a medida que se exploran y resuelven misterios, surgen otros de mayor magnitud y complejidad; hoy en día muchos de los estudios e investigaciones que tratan de arrojar luz sobre estos problemas requieren herramientas software extremadamente complejas (simulaciones, análisis numérico, predicciones, ...), y por consiguiente tienen asociado un coste computacional alto.

Para enfrentarse a ello, los sistemas de alto rendimiento han pasado de un modelo de potencia bruta a uno colaborativo, en el que diversos componentes hardware trabajan de manera distribuida para ejecutar esas herramientas, asumiendo de forma paralela el coste total.

En este sentido han surgido nuevos dispositivos hardware específicamente diseñados para este modelo; en concreto, Intel ha desarrollado el Xeon Phi, un acelerador de decenas de núcleos de proceso que se encarga de tareas con un alto grado de paralelismo.

Esta investigación trata de informar del valor de esta pieza para las necesidades actuales y de cómo optimizar las aplicaciones para ejecutar sobre ella y sacar el máximo rendimiento; además se introducirán una serie de métricas, métodos y algoritmos para aprovechar el poder computacional combinado en un entorno heterogéneo compuesto por un procesador tradicional Xeon y este acelerador, un proceso conocido como equilibrio de carga.

En este entorno se realizarán un conjunto de pruebas sobre dos aplicaciones típicas en la computación de alto rendimiento, la simulación N-body y el filtrado de imágenes, en las que se pondrán en práctica los métodos desarrollados.

Por último, se analizarán los resultados de estas pruebas, donde serán explicadas las mejoras producidas por cada uno de ellos sobre los programas elegidos, así como las principales razones que han conducido a esos incrementos de rendimiento.

Palabras clave: paralelismo, acelerador, coste o carga computacional, sistema heterogéneo, equilibrio de carga, Intel Xeon Phi.

# **Abstract**

Human beings' curiosity is inborn and infinite, for many it takes part in their meaning of life conception, but while we get further through solving unanswered questions and mysteries, more and more versions of these pop up with higher degree of both scale and complexity; nowadays a considerable fraction of the studies and investigations going on require extremely complex software tools (simulations, numerical analysis, forecasting, ...), which in turn have a huge computational cost associated to them.

In order to face this issue, high performance systems have transitioned from a pure power model to a rather colaborative one, in which big numbers of diverse hardware subsystems work in a distributed way to execute these mentioned tools, assuming the total cost in a parallel manner.

Having this into account, new specific hardware for this model is being created; in particular, Intel has developed the Xeon Phi, an accelerator possesing dozens of processing cores which takes care of applications with high degrees of parallelism.

This investigation tries to transmit the value of the Xeon Phi for today's needs, and gives advise on how to optimize software for it, squeezing its performance to higher levels; moreover a set of metrics, methods and algorithms will be introduced to exploit the combined computational power in a heterogeneous environment formed by a traditional Xeon processor and this accelerator, a process being known as load balancing.

Within this environment, a test set will be applied to two main applications in high performance computing, N-body simulation and image filtering, this set reflecting the implementation of previously introduced methods.

At last, the results of the tests will be analysed, and both the improvements in performance due to these methods as well as the reasons driving to them will be explained.

**Keywords**: parallelism, accelerator, computational cost or complexity, heterogeneous system, load balancing, Intel Xeon Phi.

# Capítulo 1

## Introducción

#### 1.1. Sistemas heterogéneos

La ley de Moore expresa que el número de transistores en un microchip dobla su magnitud cada dos años, aproximadamente; las consecuencias de esto son, entre otras, las mejoras a nivel de microarquitectura, como el aumento de componentes (puertas lógicas, registros, contadores, ...) o la optimización de su distribución; esto, a su vez, tiene un impacto en el rendimiento del hardware, que es capaz de producir mejores resultados para mismas cargas.

Normalmente este efecto se produce por la reducción del tamaño del transistor y por consiguiente el aumento de su densidad en el circuito, no obstante los límites físicos están frenando la tendencia; con tamaños de 10 nanómetros planificados para 2017, cada vez son más notables los problemas asociados con esta métrica, como el filtrado de energía o la complejidad de manufacturación; por otro lado el consumo energético está conteniendo el incremento de las frecuencias de reloj en los procesadores, uno de los parámetros fundamentales de mejora de rendimiento.

A raíz de esto se han generado una serie de conceptos y técnicas para sobrepasar estas limitaciones, que radican en dos principios fundamentales: la división y la simultaneidad en el procesado de la carga computacional.

Desde el procesador multinúcleo hasta los sistemas heterogéneos, la transición hacia ejecuciones distribuidas y colaborativas de los programas ha supuesto una serie de retos a los programadores; entre ellos está la necesidad de adaptar sus aplicaciones y, aún más importante, su concepción de la programación.

Particularmente en los sistemas heterogéneos, los componentes hardware participantes presentan diferencias a nivel arquitectural, cuyas consecuencias impactan negativamente tanto a la compatibilidad de los modelos de programación como al propio proceso de compilación (diferentes arquitecturas, distintas instrucciones).

Una combinación especialmente típica en estos sistemas es la utilización de un acelerador para complementar a la unidad de proceso principal; el acelerador normalmente se encarga de tareas con alto grado de paralelismo en su ejecución, ya que su característica fundamental es el elevado número de núcleos de proceso; estos núcleos son distintos de los de un procesador tradicional, individualmente son menos potentes, pero al ser más tienden a generar mayor rendimiento cuando el procesado es divisible.

Para paliar el sobrecoste temporal y económico de introducir nuevas metodologías de programación en pos de obtener beneficios de estos componentes, Intel ha lanzado un tipo de acelerador

denominado Xeon Phi, que permite a los programadores utilizar sus paradigmas tradicionales para conseguir esa mejora de rendimiento.

#### 1.2. Objetivos y plan de trabajo

Esta investigación se ha centrado en la programación de un entorno heterogéneo compuesto por un procesador Intel Xeon y un acelerador Intel Xeon Phi; la idea principal es caracterizar las capacidades del acelerador, en qué aspectos destaca y la importancia de su correcta programación; además se introducen mecanismos para la repartición o equilibrio de carga entre ambos componentes, comparando el rendimiento con el de la ejecución individual y señalando los sobrecostes de comunicación y sincronización.

El enfoque es fundamentalmente didáctico, de tal forma que el lector pueda observar no sólo las consecuencias de la utilización de un sistema heterogéneo, sino el motivo de los métodos de programación, optimización y equilibrio utilizados, así como el tipo de aplicaciones a las que está destinado cada uno de ellos.

Los objetivos concretos del proyecto han sido los siguientes:

- Optimización de aplicaciones para el acelerador Intel Xeon Phi, mejora de rendimiento de programas existentes a través de las características arquitecturales de este componente; a partir de la implementación secuencial de un algoritmo, adaptar el código mediante modelos de programación tradicionales para conseguir un rendimiento óptimo en el acelerador.

- Implementación de mecanismos para equilibrar la carga computacional en un sistema heterogéneo compuesto por un procesador Xeon y un acelerador Xeon Phi; a través de la descarga de datos, conseguir la co-ejecución de un programa en ambos componentes, mejorando aún más los resultados de la implementación optimizada; cada uno de estos mecanismos estará enfocado a un tipo de aplicación concreto para el cual ofrecerá la máxima efectividad.

Para conseguirlos, se ha llevado a cabo el siguiente plan de trabajo:

- Recopilación de información sobre el Intel Xeon Phi, su arquitectura, modelos de programación y diferencias claves con los procesadores multinúcleo tradicionales.

- Exposición de los principales aspectos a tener en cuenta a la hora de optimizar los programas para su utilización en el acelerador Xeon Phi, en concreto la paralelización y la vectorización de las fases computacionales.

- Introducción al equilibrio de carga, clasificación en dos grandes grupos, carga regular e irregular, con ejemplos de aplicaciones concretas; identificación de métodos específicos para cada uno de ellos, diferencias, ventajas y desventajas.

- Desarrollo de aplicaciones bajo un modelo de programación de memoria compartida compatible entre el procesador y el acelerador, OpenMP; implementación de los métodos previamente introducidos, utilizando el modelo de descarga u offload para la repartición de la carga computacional.

- Pruebas sobre el sistema real, generación de resultados y análisis de estos para la verificación y validación de la viabilidad en los métodos aplicados; rendimiento y *speedups* conseguidos.

#### 1.3. Estructura del documento

Además del actual capítulo de introducción, el documento consta de 5 capítulos adicionales configurados según la siguiente estructura:

- Capítulo 2: Estado del arte. Se realiza una primera exposición de los conceptos reflejados durante el resto del proyecto: tendencias y necesidades en la computación de alto rendimiento, aceleradores y el Xeon Phi, aspectos arquitecturales, modelos de programación y algoritmos de equilibrio de carga.

- Capítulo 3: Optimización de aplicaciones para el Xeon Phi. Se profundiza en los principales factores a tener en cuenta a la hora de optimizar las aplicaciones para el Xeon Phi, en concreto se explican los fundamentos de la paralelización y la vectorización, así como los recursos prácticos (opciones de compilación, directivas, variables de entorno) necesarios para activarlos y utilizarlos eficazmente; además, se destacan algunos puntos importantes adicionales que mejorarán el rendimiento de las aplicaciones; finalmente se expone un ejemplo práctico que resume el capítulo e integra los métodos introducidos.

- Capítulo 4: Algoritmos de equilibrio de carga. Explicación del concepto de equilibrio de carga, qué consecuencias tiene (sobrecostes de comunicación, diferencia temporal, ...) y división de la carga en dos grandes grupos, regular e irregular; se presentan tres métodos para intentar obtener el ratio óptimo de división de trabajo: un análisis estático mediante interpolación de las curvas de coste computacional, el método de bisección aplicado al ratio, y un algoritmo dinámico de partición y distribución de segmentos a procesar en tiempo de ejecución; se discutirá el tipo de carga al que estará dirigido cada uno y los posibles resultados de su implementación.

- Capítulo 5: Evaluaciones y resultados. Una breve introducción al entorno real de pruebas con sus características más importantes; se detalla el desarrollo e implementación de todos los métodos y algoritmos mencionados en los capítulos 3 y 4 para un conjunto de aplicaciones concretas, señalándose los puntos clave del código y las herramientas utilizadas (Intel Language Extensions for Offload, OpenMP, compilador ICC, ...); finalmente se realiza un grupo de pruebas basadas en estas implementaciones, y se analizan los resultados obtenidos, contrastando su viabilidad y efectividad.

- Capítulo 6: Conclusiones y trabajos futuros. En este último capítulo se exponen una serie de conclusiones sobre el proceso de realización de este proyecto: dificultades, objetivos logrados, aprendizaje, ...; además, se indicarán brevemente algunos conceptos relevantes sobre los que trabajar para, en un futuro, mejorar los desarrollos y el valor de los resultados.

# Capítulo 2

# Estado del arte

La computación de alto rendimiento se suele asociar a grandes sistemas capaces de alcanzar miles de millones de operaciones por segundo, de tal forma que pueden ejecutar aplicaciones realmente complejas en un tiempo razonable; éstas normalmente están relacionadas con ámbitos científicos y tecnológicos: simulación de entornos dinámicos de partículas, estudios del origen del universo, predicción del clima y catástrofes naturales, pruebas nucleares, ...[1] Actualmente, la supercomputadora más potente a nivel mundial ha logrado un rendimiento de unos 100 petaflops¹ en los benchmarks estándar, y se está trabajando para alcanzar la escala del exaflop en los próximos años.

No obstante, alrededor de esta idea de alcanzar la máxima capacidad de cómputo posible, han surgido nuevas preocupaciones que han afectado a la dirección del desarrollo de hardware y software para HPC considerablemente.

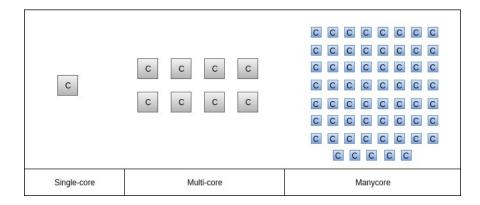

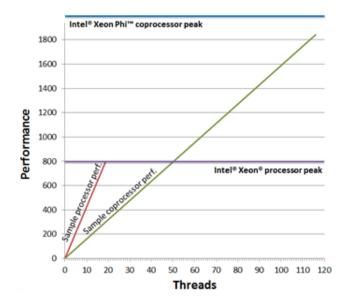

Con las limitaciones de la ley de Moore ya se había observado que la tendencia hacia arquitecturas paralelas era una forma no sólo de romper el muro del mononúcleo, sino de incrementar la eficiencia energética del sistema; los últimos avances en este campo han traído de la mano las denominadas arquitecturas manycore, que pasan a utilizar decenas, incluso centenas de núcleos de proceso; éstos son de naturaleza simple, y su rendimiento en aplicaciones secuenciales no es bueno, ya que excluyen muchas de las características técnicas de los cores modernos (ejecución OoO, pipelines profundas, ...), pero esto a su vez tiene la ventaja de hacerlos extremadamente eficientes en su consumo, mientras que logran alcanzar rendimientos elevados en aplicaciones paralelas debido a su número (ver figura 2.1).

Por otro lado, se ha insistido en la importancia de la accesibilidad a los sistemas actuales, en su mayoría distribuidos y heterogéneos; paradigmas de programación como MPI u OpenCL permiten el desarrollo de aplicaciones que pueden utilizar los distintos recursos del sistema de forma conjunta, pero son complicados y requieren conocimiento técnico de las arquitecturas subyacentes, así como de modelos de programación adecuados.

Teniendo en cuenta que las personas que hacen uso de estos sistemas no son especialistas ni siquiera en el campo de la informática (físicos, matemáticos, médicos, ...), es necesario ofrecerles una alternativa para adaptar sus aplicaciones sin que se tengan que formar extensivamente para ello; en este sentido, Intel ha hecho un movimiento significativo, ya que ha conseguido crear una arquitectura manycore compatible con modelos de programación tradicionales como los utilizados en los multinúcleo x86, la llamada Intel MIC.

<sup>&</sup>lt;sup>1</sup>Un petaflop equivale a mil billones europeos (10<sup>15</sup>) de operaciones en punto flotante.

Figura 2.1: Los núcleos del manycore son mucho más sencillos, el rendimiento viene de su número.

#### 2.1. Intel Xeon Phi

Intel Xeon Phi es el nombre comercial dado a una serie de procesadores basados en Intel MIC que vio la luz por primera vez en junio de 2013, cuando el Tianhe-2 entró en la lista Top500 como la supercomputadora más rápida del mundo utilizando este hardware[2].

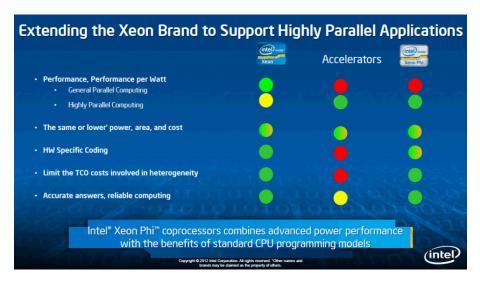

La primera versión recibió el nombre en clave *Knights Corner*, y es sobre la que se ha llevado a cabo esta investigación; el Knights Corner se considera un coprocesador o acelerador, un tipo de hardware pensado para complementar a las CPUs tradicionales y asistir con las tareas de alto grado de paralelismo; otros ejemplos de aceleradores actualmente presentes en el mercado son las GPUs (ver figura 2.2).

Figura 2.2: Intel destaca la reducción de costes asociados al desarrollo de software debido a la compatibilidad del Phi. Aquí "accelerators" hace referencia a las GPUs. Fuente: Intel.

#### 2.1.1. Aspectos clave y arquitectura

El Intel Xeon Phi Knights Corner (KNC), debido a su naturaleza de acelerador, necesita un procesador tradicional para poder funcionar; la conexión y comunicación entre ambos se lleva a cabo mediante un bus PCI Express v2.

Para poder utilizarlo es necesario instalar una capa de software adicional denominada Intel MPSS (Manycore Platform Software Stack), que consiste fundamentalmente en un sistema Li-

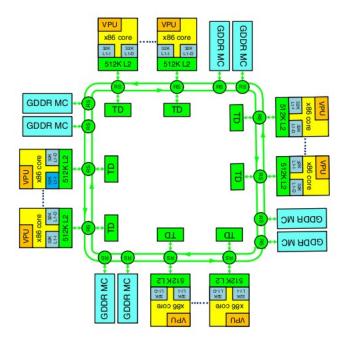

Figura 2.3: Arquitectura del Knights Corner. Fuente: [5]

nux y utilidades para la correcta comunicación y ejecución de aplicaciones; una vez instalada es posible acceder al acelerador mediante un túnel SSH desde la CPU.

Su arquitectura está basada en la ya mencionada Intel MIC; los fundamentos de ésta son la integración de muchos núcleos de proceso en un único chip, en concreto KNC posee 61, y cada uno de ellos es capaz de ejecutar 4 hilos hardware mediante SMT, lo que constituye un total de 244 posibles hilos concurrentemente en el sistema; estos núcleos están conectados entre sí a través de un anillo bidireccional de alto rendimiento, y tienen acceso a 8 controladores de memoria, con un máximo de 16 GB de GDDR5 en el sistema y ancho de banda de 352 GB/s; esta memoria es compartida entre los núcleos a través del anillo y presenta coherencia de caché[3] en todo el chip.

Cada uno de los núcleos ejecuta instrucciones en orden por dos cauces, lo que significa que puede albergar dos líneas de ejecución simultáneas y hasta 4 hilos concurrentemente gracias al SMT; funcionan a 1.2 GHz y poseen 32 KB de caché de instrucciones y otros 32 KB de datos de L1[4]; la L2 es de 512 KB en cada uno, pero es compartida entre todos, haciendo un total de 30 MB de capacidad; su microarquitectura está fundamentada en los cores x86 de Intel Pentium y poseen soporte para 64 bits (ver figura 2.3).

Un aspecto fundamental de la arquitectura del KNC además de su número de cores, es el soporte para operaciones vectoriales; cada núcleo posee una estructura vectorial con anchura de registro de 512 bits, capaz de ejecutar instrucciones SIMD de hasta 8 operaciones en coma flotante de precisión doble o 16 de simple simultáneamente; es importante destacar que la ISA vectorial del KNC, denominada Intel IMCI (Initial Many Core Instructions), no es compatible ni equivalente a las extensiones vectoriales SSE y AVX de las CPUs tradicionales, por tanto la programación vectorial explícita no es recomendable.

#### 2.2. Modelo de programación

La paralelización del código y distribución de las distintas partes entre las unidades de proceso, así como la correcta utilización del subsistema vectorial son los dos pilares que sustentan la mejora de rendimiento ofrecida por el KNC; los modelos de programación y APIs tradicionales suelen ser incompatibles con los utilizados en los aceleradores, por ejemplo NVIDIA tiene su propia interfaz de programación para las GPUs, CUDA, y las soluciones como OpenCL, que tratan de homogeneizar el sistema desde el punto de vista software, son relativamente complejas[6].

En este sentido, KNC, al presentar la misma microarquitectura que los procesadores x86, supone la posibilidad de realizar código compatible en ambos sistemas hardware con un mismo modelo o API; sumado a esto, el hecho de que su jerarquía de memoria sea compartida y coherente, hace prácticamente inmediata la paralelización ligera haciendo uso de hilos.

Todo esto nos lleva a la elección de paradigmas que utilicen estas ventajas de forma sencilla para facilitar la accesibilidad antes mencionada, como es el caso de OpenMP[7].

#### 2.2.1. OpenMP: memoria compartida

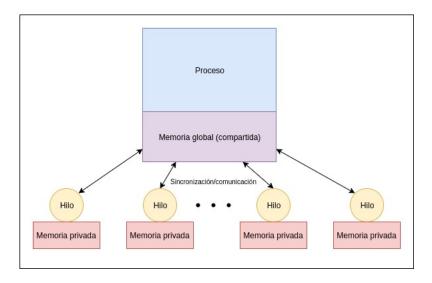

OpenMP es una API para la implementación de programas paralelos mediante hilos software; los hilos de ejecución son pequeñas secuencias de instrucciones independientes pertenecientes a un mismo proceso; éstos pueden ser ejecutados simultáneamente en un mismo sistema de memoria compartida, donde comparten los recursos y se comunican a través del espacio de memoria asignado a su proceso padre.

Su programación es relativamente sencilla, ya que utiliza una colección de directivas, funciones y variables de entorno que abstraen al usuario de la gestión de los hilos en el sistema; la API está disponible para los lenguajes de programación C, C++ y Fortran, siendo el primero de ellos el utilizado en este trabajo.

Cada hilo de ejecución posee un espacio de memoria privado para realizar sus operaciones y guardar las variables no compartidas, mientras que el resto de datos se encuentra en la memoria global del proceso padre, donde se realiza la comunicación y la sincronización; esta última es fundamental para la correcta ejecución del programa, y, a pesar de que OpenMP la abstrae en su mayoría, a veces es necesario expresarla explícitamente mediante puntos de sincronización (ver figura 2.4).

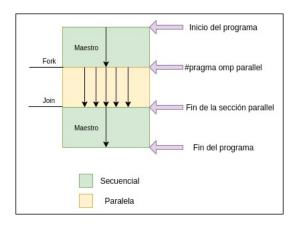

Un programa en OpenMP empieza como un proceso con un hilo de ejecución maestro; si no existe ninguna directiva, la aplicación se ejecutará de forma secuencial en un núcleo, en el que se planificará el hilo maestro; el trabajo del programador es detectar las partes del código altamente paralelizables y añadir las directivas correspondientes para la creación y manejo de los hilos; esto es lo que se conoce como un modelo "fork-join": en la parte secuencial ejecuta un único hilo maestro; cuando se llega a la parte paralela se generan tantos hilos como el programador haya especificado (fork) y éstos la ejecutan, cuando termina la parte paralela se reúnen los resultados (join) y vuelve a ejecutar el maestro (ver figura 2.5).

En la pieza de código 2.1 podemos ver un ejemplo de C y OpenMP con las directivas fundamentales.

Figura 2.4: Modelo de memoria en OpenMP.

```

// Parte secuencial.

int a = 1, b = 2;

// Parte paralela.

#pragma omp parallel num_threads( 8 ) private( a ) shared( b )

{

#pragma omp master

{

int numthreads = omp_get_num_threads();

printf( "%d\n", numthreads );

}

#pragma omp barrier

#pragma omp for simd

for( int i = 0; i < 10; i++ )

{

a += 1;

b *= 2;

}

}

//Parte secuencial.

printf( "Privada: %d, compartida: %d\n", a, b );</pre>

```

Listing 2.1: Ejemplo de código C con directivas OpenMP.

Todas las directivas comienzan con  $\#pragma\ omp\ y$  continúan con su acción concreta, seguida de sus opciones.

En este caso, el hilo maestro comienza el programa y crea dos variables enteras, a con valor de 1 y b con valor de 2; posteriormente llega a la directiva parallel, la cual se encarga de hacer el fork y crear tantos hilos como los especificados en la opción  $num\_threads$ , es decir, 8; la variable a va a la memoria privada de cada hilo mediante la opción private, mientras que la variable b va a la memoria global del proceso padre a través de la opción shared, y por lo tanto es compartida entre los hilos.

A partir de la directiva parallel, el mismo código es ejecutado por todos los hilos activos; la sección master hace que sólo el hilo maestro ejecute esa parte del código, así que el resto de hilos se la saltarán hasta llegar a barrier, que constituye un punto de sincronización explíci-

Figura 2.5: Modelo de ejecución en OpenMP.

to: mientras que todos los hilos no hayan ejecutado hasta esa barrera, no se reanuda el programa.

La directiva compuesta for simd es una combinación de dos directivas básicas: for señala que las iteraciones del bucle a continuación se dividirán entre el número de hilos disponibles y se ejecutarán en paralelo, mientras que simd indica al compilador que, si es posible, se utilicen las instrucciones vectoriales para el contenido del bucle.

OpenMP ofrece muchas más directivas, así como funciones en tiempo de ejecución que permiten modificar el entorno, más adelante se verán las más relevantes a la hora de programar para la arquitectura MIC.

#### 2.2.2. Modo nativo

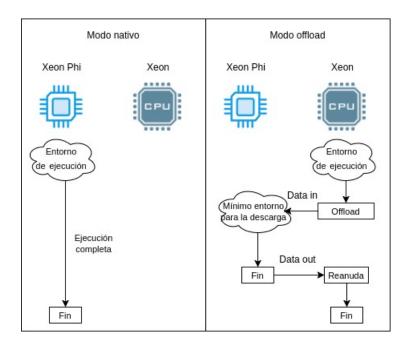

Hemos destacado que, a diferencia de las GPUs, KNC es un sistema en sí mismo, ejecuta una capa Linux y es posible acceder a él desde el host Xeon; esta característica es de alta importancia, ya que nos permite la ejecución nativa de aplicaciones en el coprocesador.

Existen varias ventajas que nos ofrece el ejecutar de forma nativa; entre ellas, hay dos que son fundamentales:

- No existe transferencia de datos entre el host y el acelerador; al tener control total del entorno de ejecución, el acceso a los recursos es inmediato y no se requiere de comunicación ni sincronización entre los dos sistemas; KNC puede trabajar sólo.

- El compilador, al producir código nativo para el KNC, es capaz de fijarse en la arquitectura MIC para generar código que se aproveche de las características beneficiosas de ésta, como es el conjunto de instrucciones IMCI.

#### 2.2.3. Modo descarga (offload)

Si bien es cierto que el modo nativo nos permite aprovechar al máximo el potencial del KNC, es importante destacar que mientras éste está trabajando, el Xeon no participa en la ejecución del programa; es posible ejecutar distintas aplicaciones en los dos sistemas para mantenerlos ocupados, pero ¿existe alguna manera de que ambos puedan participar en una misma tarea?

Tanto el compilador de Intel como OpenMP en su revisión 4.0 y posteriores, introducen un modo de programación para aceleradores, el denominado *offload*, y que precisamente se encarga de responder a ésta pregunta.

Figura 2.6: Nativo vs. Offload.

El modo offload, en castellano descarga, permite al host asignar partes de la tarea al KNC, de tal forma que las secciones de código secuencial se ejecutan en la parte del host, mientras que las más paralelizables son delegadas al acelerador (ver figura 2.6); este modo es, en esencia, el utilizado en la programación de GPUs.

En ocasiones, la magnitud de cómputo de una aplicación puede ser considerable incluso para un coprocesador como KNC; en estos casos, es bastante común que mientras el acelerador se encarga de ello, el host no esté haciendo nada, ya que está esperando los resultados y por tanto se desperdician recursos.

En este sentido, es realmente interesante explorar la posibilidad de repartir la carga computacional entre ambos sistemas; para poder obtener un rendimiento óptimo, el tiempo empleado para procesar la carga por cada sistema ha de ser el mismo, y para ello es el programador el que ha de equilibrar esta repartición, enviando más datos al componente más rápido y menos al más lento.

#### 2.3. Algoritmos de equilibrio de carga

Existen cientos de aplicaciones para HPC, y cada una de ellas puede estar implementada de muchas maneras distintas, por lo tanto es muy complicado aportar un mecanismo genérico de equilibrio de carga cuando no conoces el comportamiento de la aplicación sobre el sistema heterogéneo.

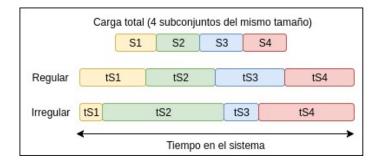

En este proyecto se han desarrollado dos formas distintas de afrontar este problema, cada una de ellas enfocada a un tipo de carga computacional: regular e irregular (ver figura 2.7).

#### 2.3.1. Pre-análisis estático

La carga computacional regular se caracteriza por ser constante a lo largo del conjunto de datos; esto quiere decir que una unidad de carga cualquiera da lugar al mismo número de ope-

Figura 2.7: Diferencias entre carga regular e irregular.

raciones en el sistema que el resto de ellas.

Normalmente balancear la carga implica asignar un subconjunto de datos a cada sistema, y debido a la regularidad es deducible que cualquier subconjunto de datos del mismo tamaño será procesado en el mismo tiempo; esto nos permite despreocuparnos de qué intervalos de datos procesará cada parte del sistema, centrándonos en la cantidad o magnitud.

En este sentido, el pre-análisis estático se encarga de ofrecer al programador una serie de pautas para poder obtener el ratio óptimo de magnitud de carga para cada sistema.

#### 2.3.2. Dinámico en tiempo de ejecución

A veces, las operaciones llevadas a cabo dentro del núcleo de cómputo son condicionadas por factores intrínsecos a la etapa de ejecución; un ejemplo típico para verlo más claro es el procesado por filas de una matriz dispersa: cuando los valores de los elementos son 0, no se realiza operación alguna, por tanto la carga de los subconjuntos de filas es variable respecto del número de elementos que tenga cada una de ellas.

Este tipo de carga se suele denominar irregular, y siguiendo con la definición utilizada anteriormente, distintos subconjuntos de datos del mismo tamaño no tienen por qué ejecutarse en el mismo tiempo.

Debido a esto, el análisis en pos de encontrar un ratio óptimo en función de las cantidades se torna complicado, ya que no existe una tendencia definitiva; a raíz de ello, es interesante pensar en una alternativa adaptable, un algoritmo en tiempo de ejecución que ofrezca carga a medida que los sistemas vayan acabando su trabajo.

# Capítulo 3

# Optimización de aplicaciones para el Xeon Phi

La fase de procesado de las aplicaciones con un alto coste computacional derivado de grandes cantidades de datos, normalmente implica la ejecución de unas pocas operaciones sobre millones de elementos; en este sentido, uno de los conceptos más importantes hoy en día en el mundo de la HPC es la **escalabilidad**, que se refiere a la capacidad de una aplicación de adaptar su ejecución sobre varios procesadores, de tal forma que estas operaciones se lleven a cabo de forma paralela sobre los distintos datos, y sin sufrir una pérdida significativa de rendimiento a causa de la repartición.

Dos de los principales caminos para conseguir esta característica son la paralelización de los programas y la utilización de paradigmas de programación vectoriales para aprovechar la arquitectura del mismo nombre; el Xeon Phi es un componente hardware especializado en ambos métodos, y por tanto es mucho más escalable que un procesador multinúcleo tradicional (ver figura 3.1), por tanto si queremos exprimir su rendimiento tendremos que modificar nuestras aplicaciones, que gracias a la programabilidad compatible, beneficiará tanto al host Xeon como al acelerador; en este capítulo veremos unas pautas generales para aprovechar al máximo ambos aspectos.

Las opciones, variables y comandos utilizados en las explicaciones son condicionadas al uso del lenguaje C, al compilador de Intel ICC y a las librerías de OpenMP[8] provistas por Intel; la utilización de GCC no es recomendable para generar ejecutables del Xeon Phi debido a ciertas limitaciones[9].

### 3.1. Identificando las cargas de cómputo paralelizables

Este proyecto se centra en aplicaciones masivamente paralelas en datos, en las que normalmente el coste computacional gira en torno a los bucles de procesado; estos recorren estructuras de datos y realizan operaciones sobre sus elementos, frecuentemente modificando su contenido o utilizándolo para generar uno nuevo; las operaciones realizadas cumplen un papel muy importante en la posibilidad de paralelizar estos bucles (ver figura 3.2), ya que pueden presentar **dependencias**; este problema se da cuando las operaciones de una iteración necesitan el resultado de otra, lo que impide la ejecución simultánea y la ganancia de rendimiento.

Existen diferentes maneras de reducir las dependencias, y por suerte los compiladores modernos se encargan en gran parte de esto[11], no obstante a la hora de programar es importante mantener los bucles limpios para facilitar el trabajo al compilador; la recomendación es utilizar

Figura 3.1: Escalabilidad del Xeon Phi respecto al Xeon. Fuente: [10].

las optimizaciones de éste siempre que sea posible, en los casos de GCC e ICC esto se puede conseguir con  $-\mathbf{O3}$  como opción de línea de comandos.

#### 3.2. Paralelizando el código

Una vez sabido que la carga es en efecto paralelizable, es necesario indicar al compilador cómo hacerlo de la forma deseada; en este caso la manera tradicional de llevarlo a cabo con OpenMP nos sirve para ambos sistemas debido a la compatibilidad existente; en el caso del Xeon Phi es necesario compilar con la opción **-mmic**, para que el ejecutable generado sea compatible con la arquitectura MIC; es importante no especificar el número de hilos en el código del programa, ya que el acelerador puede soportar muchos más que el Xeon y por tanto son valores distintos; para controlar esto, es fundamental configurar el entorno de ejecución del Xeon Phi.

Para poder ejecutar una aplicación nativa sobre el Phi hay que conectarse a él a través de un túnel SSH, y una vez dentro se presentará una interfaz de consola Linux tradicional; la fase de compilación se realiza en el host Xeon, y el ejecutable resultante se copia al Xeon Phi con herramientas como SCP[12]; en Linux, el entorno de ejecución se configura a través de variables de entorno, y para el caso del paralelismo existen dos en concreto fundamentales: OMP\_NUM\_THREADS y KMP\_AFFINITY.

Figura 3.2: Paralelización de un bucle.

Con OMP\_NUM\_THREADS es posible especificar el número de hilos software que OpenMP generará al llegar a la directiva #pragma omp parallel; en general, el máximo rendimiento es conseguido con un número de hilos igual al máximo soportado por el sistema; existen varias versiones del Xeon Phi, con diferente número de núcleos de proceso, por eso siempre es recomendable cerciorarse de este dato in situ; para ello, es posible obtenerlo con el comando nproc, o si no se dispone de éste con cat /proc/cpuinfo | grep siblings | head -n 1; en este caso el número de hilos soportados es de 61 núcleos x 4 hilos hardware que hacen un total de 244, por tanto se especificará esta variable con un valor de 244.

KMP\_AFFINITY permite especificar la afinidad de los hilos software al hardware subyacente; este es un concepto de bajo nivel de abstracción pero de alta importancia, y viene a definir la manera en la que se van a planificar los hilos software en las unidades y núcleos de proceso.

En general existen tres opciones principales, aunque se pueden hacer configuraciones personalizadas:

- Compacta (compact): los hilos software se van asignando a los hilos hardware de cada núcleo de forma que se utilicen todos los recursos de un núcleo antes de planificar sobre el siguiente; de esta manera, los hilos software estarán alojados en el menor número de núcleos posible; esto hace que se desperdicien recursos de otros núcleos.

- Dispersa (scatter): los hilos software se asignan a los hilos hardware de tal forma que ocupen el máximo número de núcleos posible; si tenemos 65 hilos, del 0 al 60 irán a los núcleos 0 al 60, mientras que el 61 se planificará de nuevo sobre el núcleo 0 (ciclo); esto aumenta la utilización del sistema, pero se pierde el beneficio de compartir caché entre los hilos, ya que cada uno estará en un núcleo distinto.

- Equilibrada[13] (balanced): fundamentalmente como la dispersa, se prioriza la utilización de los núcleos, pero en este caso los hilos software que se encargan de conjuntos de datos consecutivos se planifican sobre el mismo núcleo, de tal forma que exista la compartición de caché de la opción compacta.

Al utilizar el máximo número de hilos, realmente la afinidad disminuye su relevancia, ya que la utilización será siempre máxima, la ganancia surgirá de las dependencias entre hilos y su cercanía; la opción más recomendable para el caso general es que esta variable posea el valor balanced.

#### 3.3. Vectorización y SIMD con Intel IMCI

Además de repartir el trabajo entre las distintas unidades de proceso o hilos hardware, existe una forma complementaria de producir paralelismo de datos y mejorar el rendimiento: las extensiones vectoriales; también llamadas SIMD (una instrucción, múltiples datos), permiten ejecutar una misma operación sobre un conjunto de elementos denominado *vector* (no confundir con la estructura de datos del mismo nombre) simultáneamente (ver figura 3.3).

El número de estos elementos depende de la anchura de registro vectorial; en el caso del Xeon Phi, el conjunto de instrucciones IMCI tiene una anchura de 512 bits, y soporta tanto números enteros como en coma flotante; por ejemplo un número en coma flotante de doble precisión ocupa en el lenguaje C 8 bytes, 64 bits, por tanto se podrá ejecutar una operación simultánea sobre 8 de estos (512/64 = 8); en el caso de los multi-core tradicionales, a pesar de que hoy en día se están adoptando nuevas tecnologías como AVX-512, se utilizan extensiones vectoriales con menor anchura de registro, como son SSE (128 bits) o AVX (256 bits), por tanto

para aplicaciones vectorizables el Xeon Phi dará mejores resultados.

Y, ¿qué se considera una aplicación vectorizable? De nuevo surge el problema de las dependencias; para poder ejecutar simultáneamente una operación sobre varios datos, no pueden existir dependencias entre los elementos participantes y/o el resultado de sus operaciones, ya que no respetaría el modelo de consistencia secuencial; en el caso del paralelismo, cuando existe alguna dependencia ha de ser tratada con una etapa de sincronización, en la que, a través del establecimiento de un orden de ejecución de los hilos, se garantice esta consistencia, sin embargo en el caso de la vectorización es un requerimiento que no existan.

Otra restricción importante es el *stride* o desplazamiento de acceso a las estructuras de datos; la vectorización sólo se puede realizar sobre datos consecutivos, si existe un desplazamiento de acceso, de tal forma que en la iteración i se acceda al elemento m y en la i+1 se acceda al elemento n>m+1 la vectorización no será posible; esto suele pasar cuando los desplazamientos de acceso son un derivado del índice de iteración, por ejemplo se accede a la estructura con desplazamiento estructura[2\*i].

El compilador ICC tiene la capacidad de auto-vectorizar el código de un programa a partir de las optimizaciones -O2 en adelante, no obstante es bastante conservador en este aspecto, en el caso de que no esté seguro de las dependencias existentes o no en un fragmento de código, no realizará el proceso; en este sentido, es importante echar una mano al compilador cuando el programador esté seguro de que no existen dependencias, y para ello son proporcionados mecanismos como #pragma ivdep, que indica al compilador que ignore las dependencias asumidas, o en el caso de OpenMP 4.0+ las directivas #pragma omp simd; existen múltiples tutoriales en la red, además es posible profundizar en el tema con artículos como [14].

Es importante destacar la existencia de instrucciones intrinsic, que son llamadas a funciones que realizan específicamente una operación vectorial perteneciente a un conjunto de instrucciones vectoriales concreto; en el caso de IMCI, por ejemplo  $\_m512d$   $\_cdecl$   $\_mm512\_add\_pd(\_m512d$  v2,  $\_m512d$  v3) suma dos vectores de elementos en coma flotante de doble precisión; estas instrucciones permiten acceder al proceso de vectorización desde un nivel más bajo, y por tanto especificar de forma más concreta lo que se quiere realizar sobre el sistema, no obstante el inconveniente que tienen y por lo que no son recomendables es porque son inherentes a la arquitectura del Xeon Phi, lo cual implica que no podrán compilarse para el host Xeon, y romperán la principal ventaja del acelerador, la programabilidad compatible.

La vectorización es complementaria al paralelismo; cada unidad de proceso posee 32 registros vectoriales, en total 128 en cada núcleo, que también posee 1 unidad de procesamiento vectorial;

Figura 3.3: Funcionamiento de la vectorización.

en este sentido, para obtener el máximo rendimiento es importante integrar ambas técnicas.

#### 3.4. Otros aspectos relevantes

Gracias a la abstracción de los paradigmas de programación como OpenMP, las directivas de los compiladores y las optimizaciones llevadas a cabo por estos, paralelizar y vectorizar un programa para el Xeon Phi no resulta extremadamente complejo, no obstante se pueden tener en cuenta pequeños aspectos para optimizar aún más las aplicaciones.

#### 3.4.1. Alineamiento de estructuras de datos

En sistemas GNU/Linux y programación en C, cuando se dispone de estructuras de datos de gran magnitud, se suele utilizar memoria dinámica o *heap*; las llamadas más comunes para solicitar un bloque de memoria a utilizar son *malloc* y *calloc*.

Para computadoras de 64 bits, el bloque devuelto por estas llamadas consiste en una dirección de memoria múltiplo de 16; esto quiere decir que el primer elemento de la estructura que va a ser contenida en ese bloque estará localizado en una posición de memoria divisible por 16.

Las memorias caché poseen un tamaño de línea que representa la unidad mínima de transacción entre la memoria principal y éstas; tanto en el caso del host Xeon como el del acelerador este tamaño es de 64 bytes.

Las transacciones de memoria principal a caché son mucho más costosas que las de caché a registros, por tanto es muy importante reducirlas; para ello, es fundamental el correcto alineamiento de los bloques de memoria solicitados, en concreto se deberá alinear cualquier estructura al tamaño de línea de caché, 64; de esta forma, se consigue que el primer elemento de la estructura siempre empiece en una nueva línea de caché, de tal forma que el grueso de la estructura ocupe el mínimo número de líneas posible, y por tanto suponga el mínimo número de transacciones (ver figura 3.4).

Además de ser importante para minimizar las transacciones de memoria principal a caché, el alineamiento tiene un impacto en el proceso de vectorización, ya que se reproduce el mismo problema en las transacciones de caché a registros: el registro vectorial de 64 bytes (IMCI) accederá a la estructura de datos, si se contiene en una única línea de caché traerá todos sus elementos, si se contiene en dos necesitará dos registros y por tanto dos operaciones vectoriales.

El registro vectorial del Xeon en el caso de este trabajo es de una anchura de 32 bytes (AVX), mientras que el del acelerador sabemos que es de 64 bytes, no obstante al estar alineado a 64 está consecuentemente también a 32 (2 accesos a la misma línea de caché con desplazamiento 0 y 32).

Para poder asignar posiciones de memoria alineadas a estructuras de datos, existen llamadas especiales, en el caso de Intel nos ofrecen \_mm\_malloc y en el estándar C11 se define aligned\_alloc, ambas análogas a la hora de compilar; además de alinear la memoria, es necesario indicar al compilador que está alineada para que la utilice en el proceso de vectorización, en el caso de Intel nos proporcionan la directiva #pragma vector aligned y en OpenMP 4.0+ la opción aligned(nombre\_estructura: alineamiento) para la directiva #pragma omp simd.

#### 3.4.2. Índices de los subconjuntos de datos

Al paralelizar un bucle se asigna un subconjunto de iteraciones a cada hilo software; estos hilos, como se ha visto, estarán distribuidos por los distintos núcleos de proceso del acelerador,

Figura 3.4: Fundamentos del alineamiento.

y por tanto accederán a distintas memorias caché L1.

Los accesos a las estructuras de datos dentro de los bucles son dependientes en la mayoría de los programas del índice de la iteración que se está ejecutando en ese momento, o en su defecto de un desplazamiento sobre ese índice; en este sentido, cada hilo accederá a un subconjunto de la estructura de datos definido por los índices de acceso y del tamaño del chunk¹ especificado para el planificador.

Estos accesos traerán partes de la estructura de datos de memoria principal a la caché del núcleo de proceso en el que se aloja el hilo; como antes, es deseable reducir el número de estos accesos, así que se habrá de recurrir de nuevo al recurso del alineamiento: se trata de que cada hilo reciba un índice inicial alineado a 64 bytes, de tal forma que pueda traer el subconjunto de datos en el menor número de transacciones.

El tamaño de chunk es medido en iteraciones por tanto hay que tener en cuenta el tamaño de los elementos de la estructura de datos, si son enteros de 4 bytes, el tamaño de chunk tendrá que ser múltiplo de 16 iteraciones (64 div. 4), si son flotantes de doble precisión el elemento es de 8 bytes, por tanto chunk múltiplo de 8 iteraciones (64 div. 8).

Es relativamente común el fenómeno denominado false sharing o falsa compartición, en el que dos o más hilos en dos o más núcleos diferentes acceden a subconjuntos de la estructura de datos contenidos en líneas de caché comunes; cuando un hilo de un núcleo accede a su subconjunto trae una línea de caché y la modifica; cuando el otro hilo accede al suyo, y precisamente ha de acceder a esa línea de caché común con otro desplazamiento, no está en su memoria caché, ya que está alojado en un núcleo diferente, y por tanto se origina un conflicto de coherencia.

En la figura 3.5 se puede observar un ejemplo de este fenómeno; un vector de 14 elementos va a ser procesado por 2 hilos, cada uno de ellos se encargará de 7 elementos; estos dos hilos están alojados en dos núcleos distintos, con cachés L1 privadas.

El vector no está alineado a 64 bytes, y por tanto ocupa 3 líneas de caché en vez de 2; en la segunda de estas líneas, los elementos de v3 a v6 están asociados al hilo 1, mientras que de v7 a v10 lo están al hilo 2; esta línea es, por lo tanto, común a ambos hilos y supondrá una falsa compartición en las cachés privadas, con un coste adicional de coherencia.

Establecer una distribución de hilos favorable a los accesos de memoria y un alineamiento de

$<sup>^{1}</sup>$ El tama $\tilde{n}$ o de chunk es el número de iteraciones de los subconjuntos a asignar a los hilos software.

Figura 3.5: Falsa compartición.

```

int main()

{

const int N = 5000;

const double K = 2.0;

int i;

double *A, *B;

A = ( double * ) aligned_alloc( 64, N * sizeof( double ) );

B = ( double * ) aligned_alloc( 64, N * sizeof( double ) );

lee_datos( A, B );

for( i = 0; i < N; i++ )

{

A[i] = A[i] + K * B[i];

}

muestra_resultados( A );

return 0;

}</pre>

```

Listing 3.1: DAXPY base.

los índices reducen su impacto; para informarse más detalladamente sobre la falsa compartición se recomienda leer [15].

### 3.5. Ejemplo práctico

Una vez explicados los conceptos más importantes para la optimización de aplicaciones en el Xeon Phi, se procede a exponer un pequeño ejemplo que sirva de base para la adaptación de otras aplicaciones; éste se va a basar en la rutina DAXPY, la cual realiza la siguiente operación en un bucle: A[i] = A[i] + K \* B[i], donde los vectores A y B, así como la constante K son números en coma flotante de doble precisión.

El código base se puede observar en el fragmento de código 3.1; se ha utilizado *aligned\_alloc* para alinear los dos vectores al tamaño de línea de caché y reducir así los accesos a memoria principal.

Primero es necesario identificar si el bucle, que es el principal factor de coste computacional, es paralelizable; la iteración con operación A[i] = A[i] + K \* B[i] es independiente del resto de iteraciones, ya que no hace referencia a los resultados de éstas, por tanto el bucle es paralelizable; un contraejemplo podría ser una operación de tipo A[i] = A[(i-1)%N] + K \* B[i], en la que el

resultado actual (A[i]) depende del resultado de la iteración anterior (A[i-1]).

En el fragmento de código 3.2 se puede observar el bucle paralelizado con OpenMP; el tipo de datos double es de 8 bytes en el lenguaje C, por tanto en una línea de caché de 64 bytes entrarán 8 elementos, así que el tamaño de chunk ha de ser múltiplo de 8 para tener subíndices alineados y reducir la falsa compartición.

La planificación especificada es estática, ya que la carga computacional de cada iteración es la misma, una operación DAXPY; los chunks para este tipo de planificación son asignados a los hilos por orden de identificación, y cuando se ha asignado un chunk a cada hilo, el siguiente chunk se ofrece de nuevo al primer hilo (round-robin<sup>2</sup>); en este sentido, surge la reflexión de si es mejor un chunk pequeño (de una línea de caché), o uno grande (de varias líneas).

```

#pragma omp parallel for private( i ) schedule( static, 16 )

for( i = 0; i < N; i++ )

{

A[i] = A[i] + K * B[i];

}</pre>

```

Listing 3.2: DAXPY paralelo.

Dejando de lado el aspecto práctico para las pruebas realizadas, existe algún factor teórico que favorece el chunk grande; el Xeon Phi soporta *prefetching*, una técnica para reducir las latencias de la jerarquía de memoria, mediante la cual se traen a la caché bloques de memoria antes de ser utilizados por el programa.

El prefetching se basa en el patrón de acceso a memoria, es decir, predice los bloques que se van a utilizar, así, si el programa pide una línea de memoria L, se hace prefetch de la L+1, ya que es probable que sea utilizada; si el chunk es de una línea de caché, el prefetching no servirá, ya que la siguiente línea es otro chunk para otro hilo, sin embargo si es de varias líneas, esta técnica incrementaría el rendimiento; para conocer más sobre el prefetching se puede recurrir a [16].

En este caso el tamaño de las estructuras de datos es N=5000; como el Xeon Phi posee 244 hilos hardware, se habrán de generar 244 hilos software; si se divide 5000 entre 244, el chunk es de 20 iteraciones para cada hilo; como 20 no es múltiplo de 8 se busca el anterior número que sí lo sea, en este caso 16.

Si se utilizase 24 como tamaño de chunk, algunos hilos se quedarían sin carga de trabajo, ya que 5000/24 = 208, es decir, con 208 - 209 hilos se cubrirían todos los datos, sin embargo con un tamaño de 16 se completa el primer ciclo de asignación en el elemento 244 \* 16 = 3904, y de nuevo se asigna el chunk [3905 - 3920] al primer hilo.

Es apreciable que 16 no divide a 5000, el resto de esta división es 8, lo cual quiere decir que existirá un pequeño chunk de 8 iteraciones [4993 - 5000] restante, lo que se denomina el remainder y que se suele aislar del resto de iteraciones por el compilador para poder vectorizar íntegramente el bucle principal.

Es importante destacar que el tamaño de chunk se puede especificar en una variable, por

<sup>&</sup>lt;sup>2</sup>Algoritmo de planificación equitativo, que asigna de uno en uno los elementos a los recipientes desde el primero hasta el último, y empieza de nuevo desde el primero cuando se ha completado un ciclo de asignación.

tanto se puede adaptar tanto al tamaño de las estructuras de datos como a los hilos a generar (si se ejecuta en el host Xeon serán 24, en el Phi 244).

El código ya está paralelizado, por último es necesario vectorizarlo; en el fragmento de código 3.3 es posible observar el resultado final; la directiva simd indica al compilador que el bucle es vectorizable, mientras que la opción aligned informa de que todos los subconjuntos de datos de A y B están alineados al tamaño de línea de caché, 64 bytes.

```

#pragma omp parallel for simd private( i ) schedule( static, 16 )

aligned( A, B : 64 )

for( i = 0; i < N; i++ )

{

A[i] = A[i] + K * B[i];

}</pre>

```

Listing 3.3: DAXPY paralelo y vectorizado.

Este es un ejemplo muy básico y que favorece tanto la paralelización como la vectorización, no obstante puede funcionar de referencia a la hora de adaptar las aplicaciones; si se consiguen simplificar los bucles, eliminar dependencias y alinear accesos, se pueden optimizar de una forma similar a ésta; para ello, puede resultar interesante informarse sobre las transformaciones de bucles en artículos como [17].

Los efectos en el rendimiento de una aplicación derivados de estas optimizaciones suelen ser significativos, siempre y cuando el programa sea tanto paralelizable como vectorizable; en el apartado 5.4.1 se puede observar la magnitud de las mejoras para una aplicación que cumple estas dos premisas.

# Capítulo 4

# Algoritmos de equilibrio de carga

En las aplicaciones de alto grado de paralelismo de datos, la principal manera de utilizar un sistema heterogéneo es repartir esta carga de datos entre los distintos componentes; por ello, un buen parámetro para establecer cuán adaptada está una aplicación al sistema sobre el que ejecuta, es el grado de utilización de sus recursos.

En el anterior capítulo se presentaban una serie de factores a tener en cuenta para exprimir al máximo el rendimiento individual tanto del host Xeon como, y más importante, del acelerador Xeon Phi; este capítulo se centrará en explicar y ofrecer métodos para la explotación de ambos sistemas simultáneamente, consiguiendo rendimientos aún superiores a los programas optimizados.

# 4.1. ¿En qué consiste el equilibrio de carga? Algunas aclaraciones

Se puede definir la carga computacional de una aplicación como la cantidad de datos a procesar, y su coste como el tiempo que emplea un sistema hardware concreto en llevar a cabo tal tarea; este coste es condicionado por diversos factores: diseño del software, utilización de la arquitectura hardware, fase de compilación, entorno de ejecución y recursos disponibles, ...

El equilibrio de carga se enfoca en maximizar uno de estos factores, la utilización del sistema hardware subyacente; actualmente y como se ha mencionado en los capítulos introductorios, existe una proliferación de sistemas distribuidos heterogéneos con distintos componentes hardware que colaboran en las tareas; además de utilizar de forma óptima las facilidades de las arquitecturas de estos (cubierto en el capítulo 3), es importante que todos colaboren de una manera activa durante la ejecución de los programas.

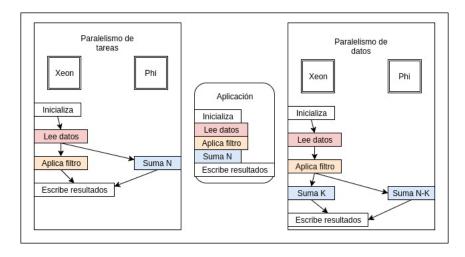

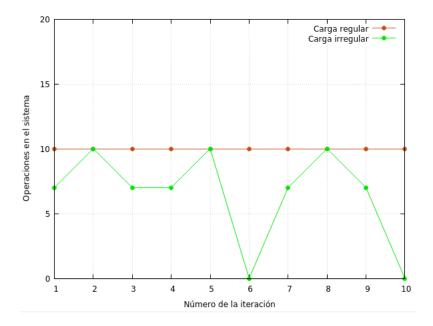

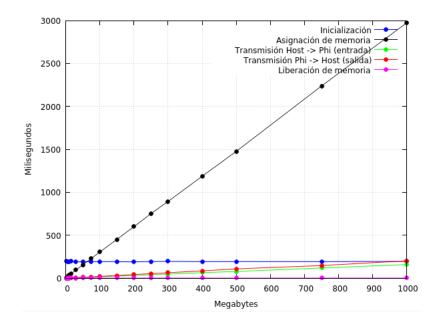

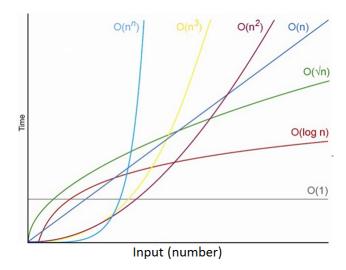

En este sentido existen dos maneras de maximizar esa actividad: división de una tarea en subtareas y repartición de éstas (paralelismo de tareas), y división de los datos a procesar en subconjuntos de datos que se asignan a las partes del sistema (paralelismo de datos) (ver figura 4.1); esta investigación se ha centrado en el equilibrio de carga a través del paralelismo de datos, no obstante estas dos vías son complementarias, por tanto no se descartan trabajos futuros que involucren el paralelismo de tareas.