# (12) SOLICITUD INTERNACIONAL PUBLICADA EN VIRTUD DEL TRATADO DE COOPERACIÓN EN MATERIA DE PATENTES (PCT)

### (19) Organización Mundial de la Propiedad Intelectual

Oficina internacional

(10) Número de Publicación Internacional WO 2012/080530 A4

(51) Clasificación Internacional de Patentes: *H04L 12/56* (2006.01)

(21) Número de la solicitud internacional:

PCT/ES2011/000343

(22) Fecha de presentación internacional:

28 de noviembre de 2011 (28.11.2011)

(25) Idioma de presentación:

Сорино

(26) Idioma de publicación:

español

(30) Datos relativos a la prioridad:

P201001589

15 de diciembre de 2010 (15.12.2010) ES

(71) Solicitante (para todos los Estados designados salvo US): UNIVERSIDAD DE CANTABRIA [ES/ES]; Pabellón De Gobierno, Avda. De Los Castros s/n, 39005 Santander (ES).

(72) Inventores; e

(75) Inventores/Solicitantes (para US solamente): ABAD FIDALGO, Pablo [ES/ES]; Dpto. Electrónica y

Computadores, Facitad de Ciencias, Avda. de los Castros 48, 39005, Santander, cantabria (ES). PUENTE VARONA, Valentin [ES/ES]; Dpto. Electrónica y Computadores, E.T.S.I. Industriales y Telecomunicaciones, Avda. de los Castros 46, 39005, Santander, Cantabria (ES). GREGORIO MONASTERIO, José Angel [ES/ES]; Dpto. Electrónica y Computadores, E.T.S.I. Industriales y Telecomunicaciones, Avda. de los Castros 46, 39005, Santander, Cantabria (ES).

(81) Estados designados (a menos que se indique otra cosa, para toda clase de protección nacional admisible): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

[Continúa en la página siguiente]

(54) Title: PACKET ROUTER FOR MULTIPROCESSOR SYSTEMS

(54) Título: ENCAMINADOR DE PAQUETES PARA SISTEMAS MULTIPROCESADOR

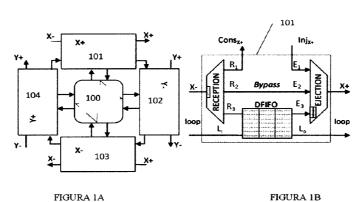

#### FIGURA 1

(57) Abstract: The invention relates to a packet router for the interconnecting networks of a multiprocessor system. The router comprises 2·B basic building blocks (101, 102, 103, 104) arranged in a ring around a local node (100), wherein B is a natural number greater than 1. The router is configured such that each packet that enters the router flows through a loop that passes through the basic building blocks (101, 102, 103, 104) until it reaches an output port that directs same to its destination. Each basic building block (101) comprises a packet reception stage (RECEPTION), a packet ejection stage (EJECTION) and a FIFO buffer (DFIFO), in which the FIFO buffer (DFIFO) has two input ports ( $R_3$ ,  $L_i$ ) and two output ports ( $E_3$ ,  $L_o$ ). One of the input ports ( $R_3$ ) is connected to an output of the packet reception stage (RECEPTION), while the other input port ( $L_i$ ) is connected to an output port of a FIFO buffer of a front-end basic building block (104). Moreover, one of the output ports ( $E_3$ ) is connected to an input of the packet ejection stage (EJECTION), while the other output port ( $L_o$ ) is connected to an input port of a FIFO buffer of a back-end basic building block (102). The FIFO buffer (DFIFO) is configured such that: either a packet leaves the router via the port ( $E_3$ ) connected to the aforementioned back-end basic building block (102) so that it can continue through the loop.

(57) Resumen:

(84) Estados designados (a menos que se indique otra cosa, para toda clase de protección regional admisible):

ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, SZ, TZ, UG, ZM, ZW), euroasiática (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), europea (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD,

#### Publicada:

- con informe de búsqueda internacional (Art. 21(3))

- con reivindicaciones modificadas y declaración (Art. 19(1))

Fecha de publicación de las reivindicaciones modificadas y de la declaración:

9 de agosto de 2012

Un encaminador de paquetes para redes de interconexión de un sistema multiprocesador que comprende 2 B bloques constructivos básicos (101, 102, 103, 104) dispuestos en anillo en torno a un nodo local (100), donde B es un número natural mayor que 1. El encaminador está configurado para que cada paquete que entra al encaminador circule a través de un lazo que atraviesa dichos bloques constructivos básicos (101, 102, 103, 104) hasta que encuentre un puerto de salida que lo acerque a su destino. Cada bloque constructivo básico (101) comprende una etapa de recepción de paquetes (RECEPTION), una etapa de expulsión de paquetes (EJECTION) y un búfer FIFO (DFIFO), donde dicho búfer FIFO (DFIFO) tiene dos puertos de entrada (R<sub>3</sub>, L<sub>i</sub>) y dos puertos de salida (E<sub>3</sub>, L<sub>0</sub>), donde uno de los puertos de entrada (R<sub>3</sub>) está conectado a una salida de dicha etapa de recepción de paquetes (RECEPTION), y el otro puerto de entrada (L<sub>i</sub>) está conectado a un puerto de salida de un búfer FIFO de un bloque constructivo básico anterior (104), y donde uno de los puertos de salida (E<sub>3</sub>) está conectado a una entrada de dicha etapa de expulsión de paquetes (EJECTION), y el otro puerto de salida (Lo) está conectado a un puerto de entrada de un búfer FIFO de un bloque constructivo básico posterior (102), estando dicho búfer FIFO (DFIFO) configurado para que o bien un paquete abandone el encaminador a través del puerto (E<sub>3</sub>) conectado a dicha etapa de expulsión de paquetes (EJECTION), o bien un paquete abandone el búfer FIFO (DFIFO) a través del puerto (L<sub>0</sub>) conectado a dicha bloque constructivo básico posterior (102) para que siga circulando a través de dicho lazo.

## REIVINDICACIONES MODIFICADAS

recibidas por la oficina Internacional el 6 de Junio de 2012 (06.06.2012)

#### REIVINDICACIONES

1. Un encaminador de paquetes para redes de interconexión de un sistema multiprocesador, donde dicho encaminador de paquetes comprende 2·B bloques constructivos básicos (101, 102, 103, 104) dispuestos en anillo en torno a un nodo local (100), donde B es un número natural mayor que 1 y que corresponde al número de dimensiones de la topología a emplear, estando el encaminador configurado para que cada paquete que entra al encaminador circule a través de un lazo que atraviesa dichos bloques constructivos básicos (101, 102, 103, 104) hasta que encuentre un puerto de salida que lo acerque a su destino,

5

10

15

20

25

30

donde cada bloque constructivo básico (101) comprende una etapa de recepción de paquetes (RECEPTION), una etapa de expulsión de paquetes (EJECTION) y un búfer FIFO (DFIFO), donde dicho búfer FIFO (DFIFO) tiene dos puertos de entrada (R<sub>3</sub>, L<sub>i</sub>) y dos puertos de salida (E<sub>3</sub>, L<sub>o</sub>), donde uno de los puertos de entrada (R<sub>3</sub>) está conectado a una salida de dicha etapa de recepción de paquetes (RECEPTION), y el otro puerto de entrada (L<sub>i</sub>) está conectado a un puerto de salida de un búfer FIFO de un bloque constructivo básico anterior (104), y donde uno de los puertos de salida (E<sub>3</sub>) está conectado a una entrada de dicha etapa de expulsión de paquetes (EJECTION), y el otro puerto de salida (L<sub>o</sub>) está conectado a un puerto de entrada de un búfer FIFO de un bloque constructivo básico posterior (102), estando dicho búfer FIFO (DFIFO) configurado para que o bien un paquete abandone el encaminador a través del puerto (E<sub>3</sub>) conectado a dicha etapa de expulsión de paquetes (EJECTION), o bien un paquete abandone el búfer FIFO (DFIFO) a través del puerto (L<sub>o</sub>) conectado a dicho bloque constructivo básico posterior (102) para que siga circulando a través de dicho lazo,

estando el encaminador caracterizado por que dicha etapa de recepción (RECEPTION) de cada uno de dichos 2·B bloques constructivos básicos (101, 102, 103, 104), comprende una entrada (X-) y tres salidas (R<sub>1</sub> R<sub>2</sub> R<sub>3</sub>), donde dicha entrada y salidas se conectan a través de un demultiplexador de paquetes; y dicha etapa de expulsión de paquetes (EJECTION) comprende tres entradas (E<sub>1</sub> E<sub>2</sub> E<sub>3</sub>) y una salida (X+), donde

dichas entradas y salida se conectan a través de un multiplexador de paquetes.

2. El encaminador de la reivindicación 1, donde, de dichas tres salidas (R<sub>1</sub> R<sub>2</sub> R<sub>3</sub>) de la

etapa de recepción (RECEPTION) de cada uno de dichos 2·B bloques constructivos

básicos (101, 102, 103, 104), se elige, para un paquete entrante, una primera salida (R<sub>1</sub>,

Cons<sub>X+</sub>) cuando el nodo local (100) conectado al encaminador es el destino del

paquete.

5

10

15

20

25

30

3. El encaminador de cualquiera de las reivindicaciones anteriores, donde, de dichas

tres salidas (R<sub>1</sub> R<sub>2</sub> R<sub>3</sub>) de la etapa de recepción (RECEPTION) de cada uno de dichos

2.B bloques constructivos básicos (101, 102, 103, 104), se elige, para un paquete

entrante, una segunda salida (R2) conectada a dicha etapa de expulsión de paquetes

(EJECTION), si se dan simultáneamente las tres siguientes condiciones:

-el destino del paquete se puede alcanzar siguiendo la dimensión y dirección del

movimiento del actual paquete, es decir, el puerto de salida del bloque

constructivo básico acerca el paquete a destino;

-no hay ningún paquete en la etapa de expulsión (EJECTION) esperando a usar

el puerto de salida (X+); y

-un encaminador vecino conectado a través del puerto de salida del bloque

constructivo básico dispone de espacio para al menos un paquete.

4. El encaminador de las reivindicaciones 2 y 3, donde, de dichas tres salidas (R<sub>1</sub> R<sub>2</sub>

R<sub>3</sub>) de la etapa de recepción (RECEPTION) de cada uno de dichos 2·B bloques

constructivos básicos (101, 102, 103, 104), se elige, para un paquete entrante, una

tercera salida (R<sub>3</sub>) conectada a dicho búfer (DFIFO), obligando a dicho paquete a

moverse continuamente dentro del lazo formado por el conjunto de bloques

constructivos básicos, cuando ninguna de las dos alternativas previas son

seleccionables y se cumple al menos una de las siguiente condiciones:

-el paquete pertenece a un tráfico no ordenado, el búfer (DFIFO) dispone de

espacio para recibir el paquete, y el espacio de almacenamiento de los búferes

de los diversos bloques constructivos básicos disponen de espacio para recibir

5

10

15

20

25

todos los posibles paquetes en tránsito pertenecientes a tráficos con mayor prioridad que el actual; o

-el paquete pertenece a un tráfico ordenado, el búfer (DFIFO) dispone de espacio para recibir el paquete y en los búferes de los diversos bloques constructivos básicos no existe otro paquete perteneciente a un tráfico ordenado.

5. El encaminador de cualquiera de las reivindicaciones anteriores, donde dicha etapa de recepción (RECEPTION) de cada uno de mencionados 2·B bloques constructivos básicos (101, 102, 103, 104) está configurada para almacenar temporalmente al menos un paquete.

6. El encaminador de cualquiera de las reivindicaciones anteriores, donde de dichas tres entradas ( $E_1$   $E_2$   $E_3$ ) de la etapa de expulsión de paquetes (EJECTION) de cada uno de dichos 2·B bloques constructivos básicos (101, 102, 103, 104): una primera entrada ( $E_3$ ) comprende un espacio de almacenamiento configurado para almacenar al menos dos paquetes procedentes del búfer FIFO (DFIFO) al que se encuentra conectada; y una segunda entrada ( $E_1$ ) está configurada para conectar la etapa de expulsión (EJECTION) a un puerto inyector ( $Inj_{X+}$ ) del nodo local (100); y una tercera entrada ( $E_2$ ) está configurada para conectar la etapa de expulsión (EJECTION) con la etapa de recepción (RECEPTION).

- 7. Un sistema que comprende una pluralidad de encaminadores de paquetes de acuerdo con cualquiera de las reivindicaciones anteriores, donde dicha pluralidad de encaminadores forma una determinada topología, y donde cada encaminador de dicha pluralidad de encaminadores, está configurado para girar en un determinado sentido, siendo el sentido de giro de cada encaminador opuesto al sentido de giro de los encaminadores que se encuentren adyacentes al mismo.

- 8. El sistema de la reivindicación 7, que comprende un camino cíclico que pasa por cada uno de los encaminadores de dicha pluralidad una y solo una vez.

9. El sistema de la reivindicación 8, configurado para que, para cada bloque constructivo básico (101, 102, 103, 104) de cada encaminador, un paquete almacenado en dicho búfer FIFO (DFIFO) abandone el correspondiente encaminador a través del puerto (E<sub>3</sub>) conectado a la etapa de expulsión de paquetes correspondiente (EJECTION), si se cumple al menos una de las siguientes condiciones:

-Si se trata de un paquete de un sólo destino y el puerto de salida del bloque constructivo actual acerca el paquete a destino;

-Si se trata de un paquete multidestino, el puerto de salida del bloque constructivo actual acerca el paquete a al menos uno de sus destinos y el espacio de almacenamiento de la etapa de expulsión (EJECTION) asociado al puerto de entrada (E<sub>2</sub>) está vacío;

-Si se trata de un paquete de uno o más destinos, ha dado un número de vueltas en lazo del encaminador superior a un determinado umbral y el puerto de salida del bloque constructivo actual conecta a un enlace de comunicación perteneciente a dicho camino cíclico.

10. Un programa informático que comprende medios de código de programa informático adaptados para implementar el encaminador de paquetes según cualquiera de las reivindicaciones de la 1 a la 6 o el sistema según cualquiera de las reivindicaciones de la 7 a la 9, cuando dicho programa se ejecuta en un ordenador, un procesador de señal digital, una disposición de puertas de campo programable, un circuito integrado de aplicación específica, un microprocesador, un microcontrolador, y cualquier otra forma de hardware programable.

25

5

10

15

20

DECLARACIÓN CONFORME AL ARTÍCULO 19.1) relativa a la **PCT/ES2011/000343**, titulada ENCAMINADOR DE PAQUETES PARA SISTEMAS MULTIPROCESADOR.

Las modificaciones que se realizan de las reivindicaciones presentadas, consisten en la unión de las reivindicaciones 1 y 2 originales. De esta forma, se proporciona una implementación concreta de la etapa de recepción de cada bloque constructivo básico del encaminador de paquetes.

En concreto, dicho bloque comprende un demultiplexor de paquetes que conecta una entrada y tres salidas, y un multiplexador de paquetes que conecta tres entradas y una salida. Esta modificación en las reivindicaciones no implica ningún cambio en la descripción y figuras, ni por adición ni por omisión.

La patente prioritaria española P201001589, ha sido concedida con examen previo a fecha 21 de Octubre de 2011 (número de concesión 2360441B2). El juego de reivindicaciones de la patente concedida, es idéntico al adjunto a esta declaración según el artículo 19.1.